# Gallium Arsenide Design Methodology and Testing of a Systolic Floating Point Processing Element

by

Andrew J. Beaumont-Smith, B.E.(Hons)

A thesis submitted in fulfilment of the requirement for the degree of

Master of Engineering Science

The University of Adelaide

Faculty of Engineering

Department of Electrical and Electronic Engineering

Adelaide, South Australia

November 1995

# Contents

| Al | bstrac | :t          |                                  |       |            |               |               |     |     | V   |

|----|--------|-------------|----------------------------------|-------|------------|---------------|---------------|-----|-----|-----|

| D  | eclara | tion        |                                  |       |            |               |               |     |     | vii |

| A  | cknow  | ledgemen    | ts                               |       |            |               |               |     |     | vii |

| Li | st of  | Publicatio  | ns                               |       |            |               |               |     |     | ix  |

| Li | st of  | Symbols     |                                  |       |            |               |               |     |     | x   |

| Li | st of  | Abbreviat   | ions                             |       |            |               |               |     |     | xii |

| 1  | Intro  | duction     |                                  |       |            |               |               |     |     | 1   |

|    | 1.1    | High Perfo  | rmance Computing                 |       | ٠          | •             | ·             | *   |     | ]   |

|    | 1.2    | Systolic Pr | ocessing for Matrix Computations |       | •          | •             | •             | * : |     | ţ   |

|    |        | 1.2.1 Alg   | orithms and Architecture         | *: :* | •          |               | ٠             | •   | •   | •   |

|    |        | 1.2.2 Gra   | nularity                         |       |            |               |               | ·   | •   | (   |

|    |        | 1.2.3 Im    | olementations and Issues         |       |            | *             | () <b>•</b> ) | * : | •   | •   |

|    | 1.3    | Gallium A   | rsenide Technology               |       | 2 <b>5</b> | ÷.            | æ             |     |     | 10  |

|    |        | 1.3.1 Ga    | lium Arsenide Devices            |       | 9 8        | •             | 12            |     | ÷   | 1:  |

|    | 1.4    | Contributi  | on of the Thesis                 |       | 0: 36      |               | *:            |     |     | 1   |

|    | 1.5    | Outline of  | the Thesis                       |       |            | ٠             | <b>.</b>      | 3 9 | • : | 10  |

| 2  | Gall   | ium Arser   | ide Technology                   |       |            |               |               |     |     | 18  |

|    | 2.1    | GaAs ME     | SFET Device Modelling            |       |            | ٠             |               | í.  | 7   | 13  |

|    |        | 2.1.1 Dr    | in Current                       |       |            | 7. <b>0</b> 0 |               | :00 | •   | 19  |

|    |        | 2.1.2 Die   | de                               |       |            | ٠             | •             |     | ė   | 2   |

|    |        |             |                                  |       |            |               |               |     |     |     |

|      | 2.1.3   | Parasitic Capacitances                            | 21 |

|------|---------|---------------------------------------------------|----|

|      | 2.1.4   | Parasitic Resistances                             | 22 |

|      | 2.1.5   | Second Order Effects                              | 22 |

|      | 2.1.6   | Simulating Worst Case                             | 24 |

| 2.2  | GaAs I  | MESFET Logic Classes                              | 24 |

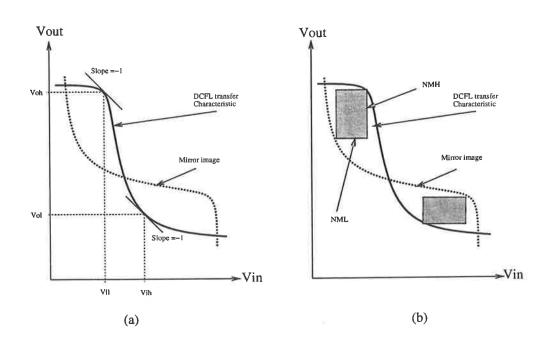

|      | 2.2.1   | Direct Coupled FET Logic                          | 27 |

|      | 2.2.2   | Source Follower Direct Coupled FET Logic          | 32 |

|      | 2.2.3   | Super Buffer FET Logic                            | 35 |

|      | 2.2.4   | Performance Comparison                            | 36 |

| 2.3  | Design  | Methodology                                       | 37 |

|      | 2.3.1   | Layout Style                                      | 37 |

|      | 2.3.2   | Design Tools                                      | 38 |

| 2.4  | Circui  | t Modelling and Parasitic Extraction              | 42 |

|      | 2.4.1   | Interconnect Analysis                             | 42 |

|      | 2.4.2   | Capacitance                                       | 43 |

|      | 2.4.3   | Characteristic Impedance                          | 44 |

|      | 2.4.4   | Resistance                                        | 49 |

|      | 2.4.5   | Inductance                                        | 50 |

|      | 2.4.6   | Line Delay                                        | 51 |

|      | 2.4.7   | Source Impedance of the Driving Gate              | 54 |

|      | 2.4.8   | Interconnect Models                               | 54 |

|      | 2.4.9   | Crosstalk                                         | 57 |

|      | 2.4.10  | Package Parasitics                                | 58 |

|      | 2.4.11  | Pad Structures                                    | 59 |

|      | 2.4.12  | Power Supply and Ground Lines                     | 60 |

| 2.5  | Summ    | nary                                              | 61 |

| Syst | tolic R | ing Processing Element                            | 62 |

| 3.1  | Digit-  | Serial Multiplication                             | 62 |

| 3.2  | Digit-  | -Serial Floating Point Multiplication             | 68 |

|      | 3.2.1   | Floating Point Numbers                            | 68 |

|      | 3.2.2   | A Systolic Cell for Floating Point Multiplication | 68 |

|   |      | 3.2.3   | Digit-Serial Floating Point Multiplier Model           | 9          |

|---|------|---------|--------------------------------------------------------|------------|

|   | 3.3  | A Syst  | olic Ring Floating Point Processing Element            | 4          |

|   | 3.4  | Perform | nance Metric of a Rectangular Systolic Array Processor | 9          |

|   | 3.5  | Archite | ecture Optimisation                                    | 1          |

|   |      | 3.5.1   | Area-Time Model Evaluation                             | 4          |

|   |      | 3.5.2   | Processor Bandwidth Requirement                        | 6          |

|   | 3.6  | Summa   | ary                                                    | 7          |

| 4 | Desi | gn, Lay | yout and Simulation 8                                  | 9          |

|   | 4.1  | Introdu | uction                                                 | 9          |

|   | 4.2  | Floatin | ng Point Representation                                | 0          |

|   | 4.3  | GaAs    | Circuit Design, Simulation and Layout                  | 1          |

|   |      | 4.3.1   | Data Flip-Flop                                         | 1          |

|   |      | 4.3.2   | Full Adder                                             | 9          |

|   |      | 4.3.3   | Systolic Cell                                          | 6          |

|   |      | 4.3.4   | I/O Pads                                               | 18         |

|   |      | 4.3.5   | Ring Controller                                        | 3          |

|   |      | 4.3.6   | Flag Checking                                          | 9          |

|   |      | 4.3.7   | Clock Generation                                       | .9         |

|   |      | 4.3.8   | Clock Distribution                                     | 23         |

|   |      | 4.3.9   | Systolic Ring                                          | 28         |

|   |      | 4.3.10  | Floorplan                                              | 28         |

|   |      | 4.3.11  | Power Circuit                                          | 80         |

|   | 4.4  | Fabric  | ation and Packaging                                    | 13         |

| 5 | Test | ing the | e Processing Element Chip                              | 5          |

|   | 5.1  | Test F  | ixture                                                 | 15         |

|   |      | 5.1.1   | PCB Design                                             | 36         |

|   |      | 5.1.2   | Construction                                           | Į4         |

|   | 5.2  | Test E  | Equipment and Set-up                                   | <u>1</u> 4 |

|   | 5.3  | Circui  | t Testing                                              | 16         |

|   |      |         | Practical Terminations                                 | 17         |

|              |                                   | 5.3.2   | Fix 1  | : Grou  | nd B   | oun   | ce.               |     |      | •       | •   |      | 8            | ٠  | •  | •     |     | •   | £.         | ě.   | 8 8  | •       | •             | * *  | 147 |

|--------------|-----------------------------------|---------|--------|---------|--------|-------|-------------------|-----|------|---------|-----|------|--------------|----|----|-------|-----|-----|------------|------|------|---------|---------------|------|-----|

|              |                                   | 5.3.3   | Fix 2  | : Sepa  | rate l | Pow   | er S              | upp | lies |         | ¥   | Sà.  | <b>€</b> 8 9 |    | *  | · ·   |     |     | ٠          | •::  | * 0  | 0 €     | •             |      | 148 |

|              | 5.4                               | Finger  | ed ME  | SFET    | Test   | Strı  | ıctu              | res |      | <b></b> | •   | ٠    | <b>*</b> : 3 |    |    |       |     |     | a <b>t</b> | •    |      | •       | •             | ÷ :  | 149 |

|              | 5.5                               | Systoli | c Cell | Functi  | onal   | Test  | ing               |     |      | •       | •   | •    | ě (          |    |    |       |     |     | •          |      |      |         | : <u>:</u> :: | ¥ 8  | 155 |

|              |                                   | 5.5.1   | Gener  | ating [ | Test ' | Vect  | ors               |     | ٠.   | •       |     | •    |              |    | ·  |       |     | *   | <b>⊙</b> 1 | ě: : | ÷ 11 | 0E - (# | 300           | * *  | 155 |

|              | 5.6                               | Systoli | c Ring | Testin  | ıg .   |       | () <b>*</b> : (*) |     | *: : |         |     | (•j) | †<br>* :     |    | 29 | 181 1 |     | ٠   |            |      |      | h 25    |               |      | 156 |

|              | 5.7                               | Clock   | Genera | tion C  | ircui  | t     |                   |     |      |         |     |      | •            |    | ě  | ē     |     |     | •          |      |      | •       | •             |      | 159 |

| 6            | Disc                              | ussion  | and E  | uture   | Wo     | rk    |                   |     |      |         |     |      |              |    |    |       |     |     |            |      |      |         |               |      | 169 |

|              | 6.1                               | Discus  | sion . |         |        | 69    |                   |     |      |         | •   | 990  | * 8          |    | ** |       | • : | *   | \ <b>.</b> | *    |      | 5 12    | je?           | * ** | 169 |

|              | 6.2                               | Future  | Work   |         |        | * * * |                   |     |      |         | ×   |      | * :          | •  | 8. | •     |     | ٠   | ٠          | ٠    | •    |         | •             | • •  | 173 |

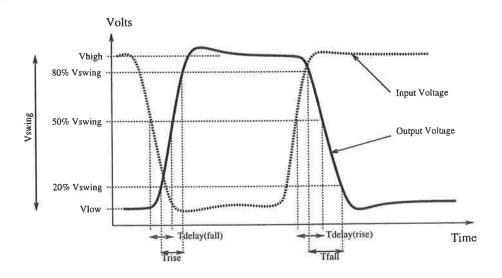

| A            | ppen                              | dix A   | : GaA  | s Digi  | tal l  | Log   | ic P              | erf | orn  | na      | n(  | ce   | S            | pe | ci | fic   | ati | ioı | ns         |      |      |         |               |      | 176 |

| A            | ppen                              | dix B   | : PE ( | Chip I  | Pin A  | Allo  | cati              | on  |      |         |     |      |              |    |    |       |     |     |            |      |      |         |               |      | 179 |

| A            | Appendix C: Test Equipment Set-up |         |        |         |        |       |                   |     |      |         | 182 |      |              |    |    |       |     |     |            |      |      |         |               |      |     |

| Bibliography |                                   |         |        |         |        |       |                   |     |      |         | 188 |      |              |    |    |       |     |     |            |      |      |         |               |      |     |

#### Abstract

Despite the recent advances in computing performance, there remain many signal processing tasks that are beyond the capabilities of current off-the-shelf computing systems. These tasks include matrix intensive operations such as real-time digital Kalman filtering, signal processing and computer simulation algorithms for electronic circuits and mechanical structures and thermal system modelling. This dependence on  $O(n^3)$  matrix operations leads to a requirement for a parallel computer architecture in the form of a multi-dimensional array of processing elements.

A general purpose matrix processing engine is described in this thesis which deals in particular with the implementation of a single processing element which forms part of a two dimensional processing array. The processing element performs addition, multiplication and multiplication – accumulation of two floating point numbers.

An architecture for a class of digit-serial systolic ring floating point processing element is investigated and a  $0.8\mu m$  gallium arsenide implementation is realised using Vitesse HGAAS-II technology. Gallium arsenide technology was chosen to implement the processing element because of its high speed and low power advantages over conventional technologies such as silicon ECL. Studies were conducted to develop an optimised logic class for this technology. A mixed logic approach using DCFL (direct coupled FET logic), SDCFL (source follower DCFL), SBFL (super buffer FET logic) was used.

A new physical layout strategy 'ring notation' was developed which was shown to be suitable for the design of high speed circuits using these classes of logic. This strategy achieves good power supply isolation from high speed signal interconnects and high packing density for these types of circuits.

A CAD environment for gallium arsenide was developed which includes the modelling of circuit parasitics, layout, circuit extraction and technology files. Circuit primitives were

designed including flip-flops, adders and multiplexers.

Architectural studies were carried out to determine the optimum architecture for this technology. It is shown that the *area-time* metric should be used to optimise these processors.

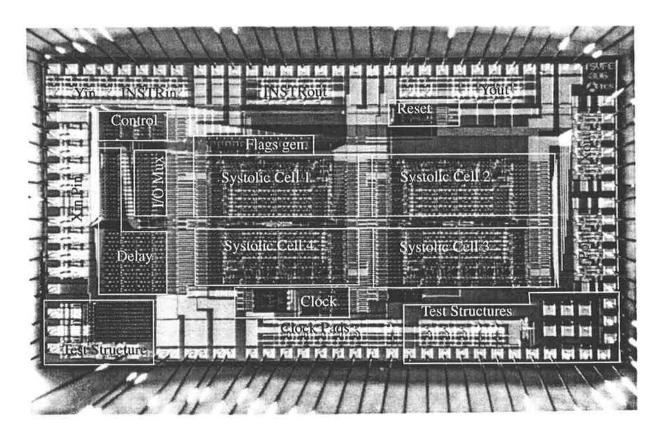

A four bit per digit implementation of the systolic-ring floating point processing element was realised for an extended floating point format. A chip was successfully fabricated using the HGAAS-II process and measured  $3mm \times 5.7mm$ . It contained 12,000 devices and has a maximum operating speed of 300MHz, producing 11Mflops for multiply – accumulate operations. The chip was tested and found to be fully functional at 128MHz (due to process variation) to produce a computation rate of 5Mflops.

# Declaration

This thesis contains no material which has been accepted for the award of any other degree or diploma in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text.

I give consent to this copy of my thesis, when deposited in the University Library, being available for loan and photocopying.

Signed:

Date: 5 Feb 1996

## Acknowledgements

Firstly, I would like to thank my supervisors, Dr. Kamran Eshraghian and Dr. Cheng-Chew Lim for their guidance and assistance with the work and the preparation of this thesis.

I would like to thank Dr. Warren Marwood for the enlightenment he has given me through the work and papers we have written jointly, for proof reading the thesis and countless interesting late night discussions.

Thanks also to my colleagues in the department and from other Universities including Mr. Ali Moini, Mr. Michael Liebelt, Dr. Jens Jakobsen (Jydsk Telefon, Denmark), Mr. Eric Chu, Mr. Mike McGeever, Mrs. Song Cui, Mr. Tim Shaw and Mr. Gyudong Kim (Seoul National University). Mr. Mike McGeever also assisted this work by characterising the I-V curves of the fabricated MESFET devices.

The support of The Australian Research Council and the Sir Ross & Sir Keith Smith Foundation is gratefully acknowledged.

Lastly I would like to thank my wife, Natalie for her endless patience and assistance in proof reading.

ABS

## List of Publications

The following is a list of publications by the author and colleagues which are related to this thesis.

A. Beaumont-Smith, W. Marwood, C.C. Lim and K. Eshraghian. "Design and Implementation of a GaAs Systolic Floating Point Processing Element". Submitted to IEE Proceedings-E, Computers and Digital Techniques, 1995.

A. Beaumont-Smith, W. Marwood and C.C. Lim. "A CMOS Linear Systolic Processing Element". Proc. 13th Australian Microelectronics Conference, pp. 74-79, July 1995.

A. Beaumont-Smith, W. Marwood, K. Eshraghian and C.C. Lim. "The Gallium Arsenide Implementation of a Systolic Floating Point Processing Element". *Proc. 12th Australian Microelectronics Conference*, pp. 255-260, October 1993.

W. Marwood and A. Beaumont-Smith. "The Implementation of a Generalised Systolic Serial Floating Point Multiplier". Proc. APCCAS'92, IEEE Asia-Pacific Conference on Circuits and Systems, pp. 513-518, December 1992.

W. Marwood and A. Beaumont-Smith. "The Architecture and Optimisation of Systolic Ring Processors". Proc. TENCON '92: IEEE Region 10 Conference, pp. 735-739, November 1992.

W. Marwood, C.C. Lim, K. Eshraghian and A. Beaumont-Smith. "Systolic Matrix Processor Architecture for Very High Speed Signal Processing". *Proc. IREECON International Convention*, 1991.

A. Beaumont-Smith, W. Marwood, C.C. Lim and K. Eshraghian, "Ultra High Speed Gallium Arsenide Systems: Design Methodology, CAD tools and Architecture". *Proc. Microelectronics* '91, I.E.Aust Conference, pp. 85-90, June 1991.

#### Software:

A. Beaumont-Smith. "EXT2HSP - A conversion program from MAGIC to HSPICE for GaAs circuits", The University of Adelaide, Adelaide, 1992.

A. Beaumont-Smith. "GAASNET V2.0 - A gallium arsenide network extractor", Integrated Silicon Design Pty.Ltd., Adelaide, 1991.

# List of Symbols

| $\epsilon_r$                  | Relative Dielectric Constant                                 |

|-------------------------------|--------------------------------------------------------------|

| $\epsilon_{eff}$              | Effective Dielectric Constant                                |

| $\sigma$                      | Conductivity or Standard Deviation (for Process Parameters)  |

| ρ                             | Resistivity                                                  |

| $Z_0$                         | Characteristic Impedance                                     |

| $W_G$                         | Channel Length                                               |

| $L_G$                         | Gate Length                                                  |

| d                             | Gate to Channel Spacing                                      |

| eta                           | Transconductance Parameter $or$ Number Base                  |

| $\alpha$                      | Saturation Factor                                            |

| $\lambda$                     | Channel Length Modulation Parameter                          |

| γ                             | Drain Voltage Induced Threshold Voltage Lowering Coefficient |

| δ                             | $I_{ds}$ Feedback Factor for TOM Model $or$ Skin Depth       |

| b                             | Critical Field for Mobility Degradation                      |

| $I_{ds}$                      | Drain to Source Current                                      |

| $I_{DSS}$ .                   | Drain-Source Saturation Current at Zero Gate-Source Voltage  |

| $I_D$                         | Diode Current                                                |

| $I_s$                         | Diode Saturation Current                                     |

| $V_d$                         | Diode Voltage                                                |

| $V_{gs}$                      | Gate to Source Voltage                                       |

| $V_{ds}$                      | Drain to Source Voltage                                      |

| $V_{TO}$                      | Threshold Voltage                                            |

| VGEXP                         | Gate Voltage Exponent                                        |

| $V_{ds0}$                     | Drain to Source Voltage for the Curtice II model             |

| N                             | Diode Ideality Factor                                        |

| T                             | Temperature in Kelvin                                        |

| $q = 1.60212 \times 10^{-19}$ | Electronic Charge                                            |

|                               |                                                              |

| $k = 1.38062 \times 10^{-23}$            | Boltzmanns Constant                                         |

|------------------------------------------|-------------------------------------------------------------|

| $\epsilon_0 = 8.854 \times 10^{-12} F/m$ | Permittivity of Free Space                                  |

| $\mu_0 = 4\pi \times 10^{-7} H/m$        | Permeability of Free Space                                  |

| r                                        | Number of Bits per Digit                                    |

| s                                        | Sign Bit                                                    |

| m                                        | Number of Mantissa Bits                                     |

| e                                        | Number of Exponent Bits                                     |

| q                                        | Number of Systolic Cells                                    |

| g                                        | Number of Guard Digits                                      |

| k                                        | Number of Digits in a Floating Point Operand                |

| p                                        | Order of a Square Systolic Array                            |

| $n_c$                                    | Number of Systolic Cells in a Systolic Ring                 |

| $n_d$                                    | Number of Digit Delay Cells in a Systolic Ring              |

| C                                        | Number of Circulations of Operands in a Systolic Ring       |

| $A_{proc}$                               | Total Active Area of a Systolic Processing Array            |

| $A_{pe}$                                 | Active Area of a Processing Element                         |

| $T_{	extit{pe}}$                         | Time to Process One Set of Operands in a Processing Element |

| $B_{proc}$                               | Systolic Processor Bandwidth                                |

## List of Abbreviations

Al

Aluminium

CIF

Caltech Intermediate Form

DAS

Digital Acquisition System

**DCFL**

Direct Coupled FET Logic

DFET

Depletion FET

ECL

Emitter Coupled Logic

EFET

Enhancement FET

ESD

Electro-static Discharge

GaAs

Gallium Arsenide

Gflops

Giga Floating Point Operations per Second

HEMT

High Electron Mobility Transistor

LCC

Leaded Chip Carrier

**MATRISC**

MATrix Reduced Instruction Set Computer

**MESFET**

Metal Semiconductor FET

Mflops

Mega Floating Point Operations per Second

MIPS .

Mega Instructions per Second

PE

Processing Element

SAGA

Self-Aligned Gate

SBFL

Super Buffer FET Logic

SDCFL

Source Follower Direct Coupled FET Logic

Si

Silicon

SI

Semi Insulating

**SIMD**

Single Instruction, Multiple Data

SPICE

Simulation Program for Integrated Circuit Estimation

TEM

Transverse Electro-Magnetic

WSI

Wafer Scale Integration

# List of Figures

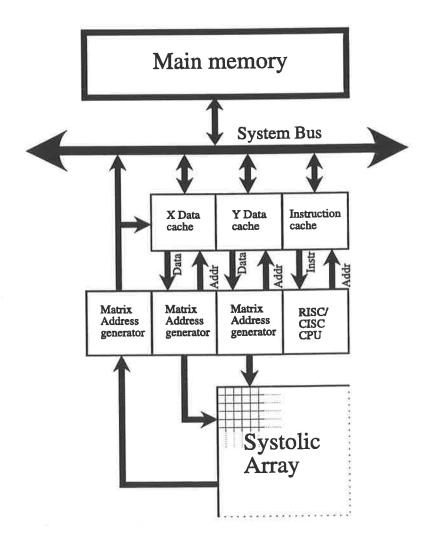

| 1 | .1   | Matrix processor architecture (MATRISC)                                                                                    | 3  |

|---|------|----------------------------------------------------------------------------------------------------------------------------|----|

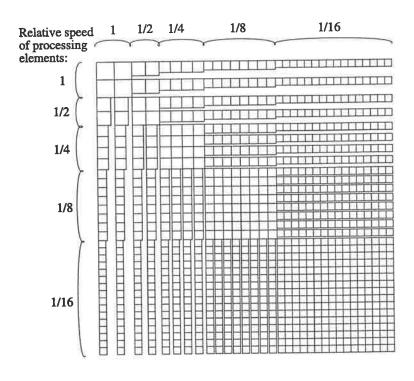

| 1 | 2    | A constant bandwidth mesh connected systolic array.                                                                        | 4  |

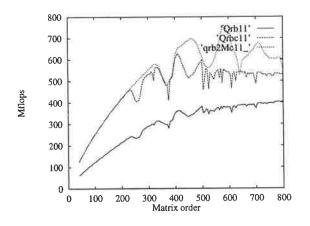

| 1 | 3    | A performance comparison of a conventional systolic array and a constant                                                   |    |

|   |      | bandwidth array when implementing a block QR factorisation algorithm.                                                      | 5  |

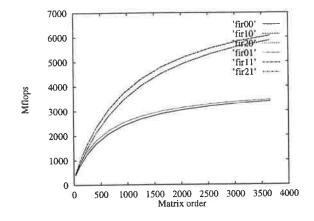

| 1 | 1.4  | Simulated performance for FIR filters implemented on an order 40 MA-                                                       |    |

|   |      | TRISC processor                                                                                                            | 5  |

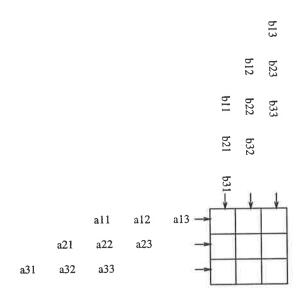

| 1 | 1.5  | A $3 \times 3$ engagement processor with input matrices A and B                                                            | 7  |

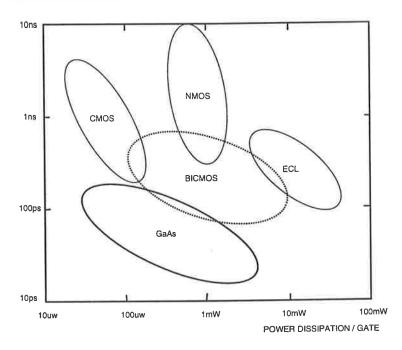

| ] | 1.6  | Speed versus power for GaAs, CMOS, BiCMOS, nMOS and ECL tech-                                                              |    |

|   |      | nologies                                                                                                                   | 11 |

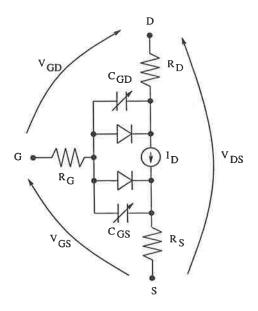

| 6 | 2.1  | GaAs MESFET equivalent circuit                                                                                             | 19 |

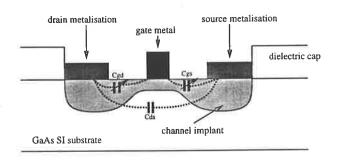

| 4 | 2.2  | Cross section of a MESFET device                                                                                           | 21 |

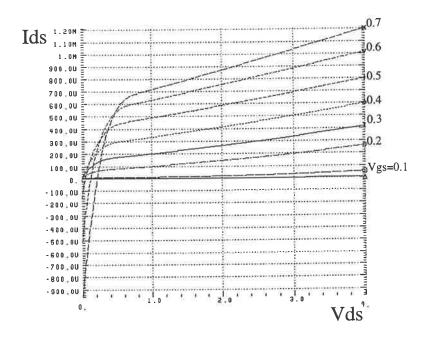

| 4 | 2.3  | Simulated I–V characteristics for an EFET, $L=0.8\mu m, W=10\mu m.$                                                        | 27 |

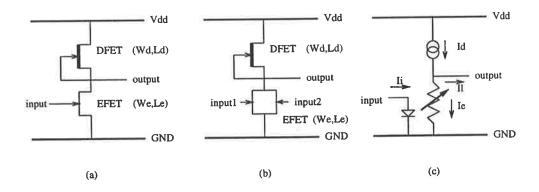

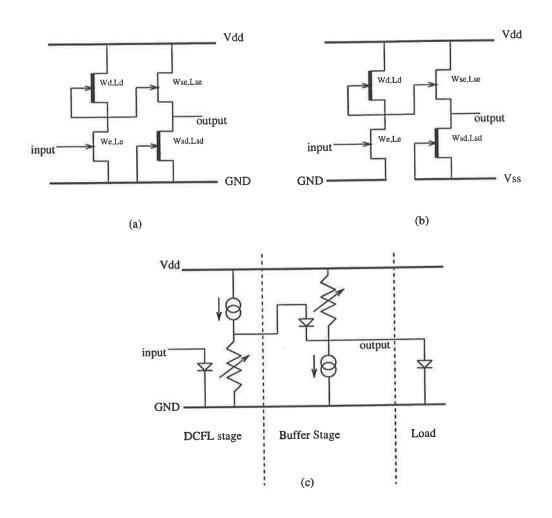

| 4 | 2.4  | (a) DCFL inverter, (b) 2 input NOR gate, (c) equivalent circuit                                                            | 28 |

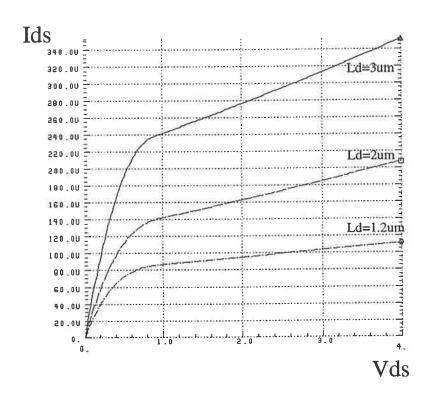

|   | 2.5  | Drain current for a DFET with $V_{gs}=0$ for a 1.2, 2 and $3\mu$ gate length                                               | 29 |

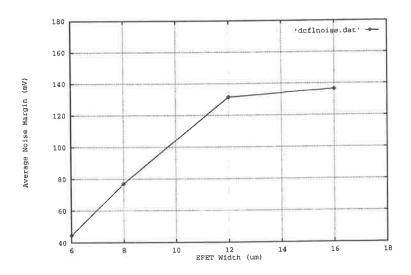

|   | 2.6  | Average noise margin of a three input DCFL NOR gate as a function of $W_e$ .                                               | 30 |

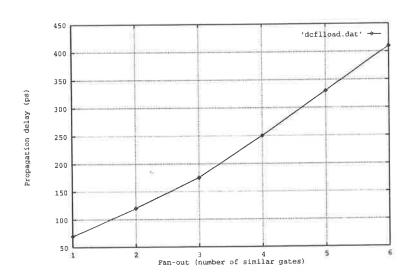

|   | 2.7  | Propagation delay of a DCFL inverter as a function of fan-out (capacitive                                                  |    |

|   |      | $load). \dots \dots$ | 31 |

|   | 2.8  | (a) SDCFL inverter, (b) SDCFL inverter with extra supply, (c) equivalent                                                   |    |

|   |      | circuit                                                                                                                    | 33 |

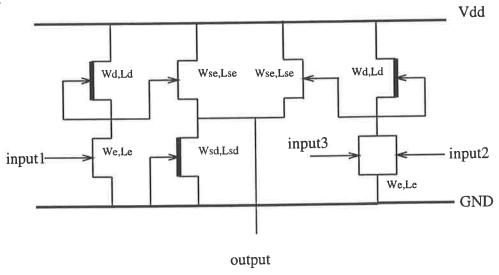

|   | 2.9  | OR-AND-INVERT (OAI) logic structure.                                                                                       | 33 |

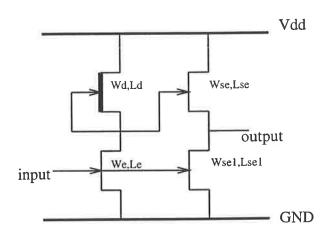

|   | 2.10 | SBFL inverter.                                                                                                             | 36 |

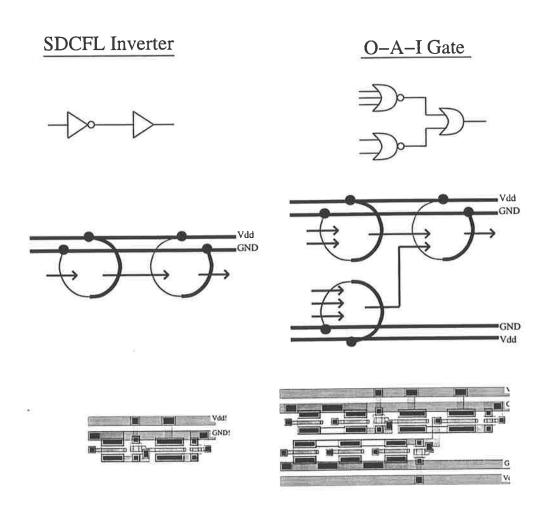

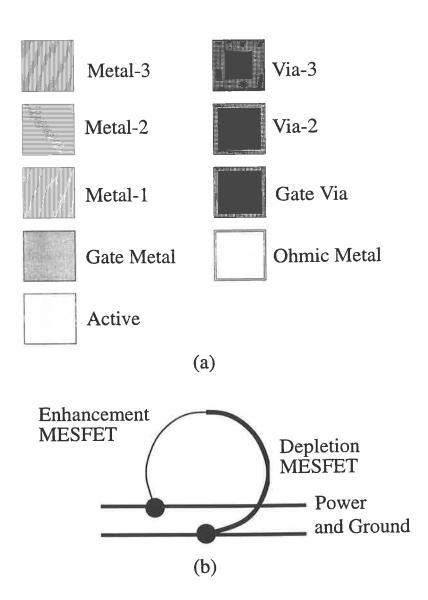

|   |      | Schematic, ring notation and layout for a SDCFL inverter and OAI structure.                                                |    |

|   |      | (a) Physical layers used for layout and (b) key for ring notation                                                          | 40 |

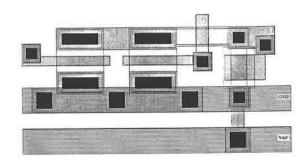

|   | 2.13 | DCFL 2 input NOR gate layout                                                                                               | 41 |

|   |      |                                                                                                                            |    |

| 2.14 | DCFL 3 input NOR gate layout                                                                                            | 41              |

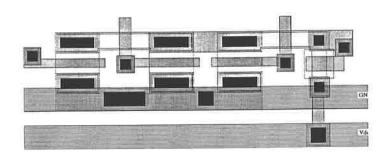

|------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.15 | SDCFL buffer layout                                                                                                     | 41              |

| 2.16 | SDCFL 2 input OR gate buffer layout                                                                                     | 41              |

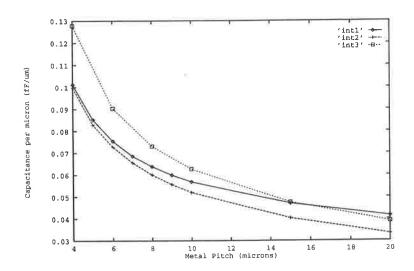

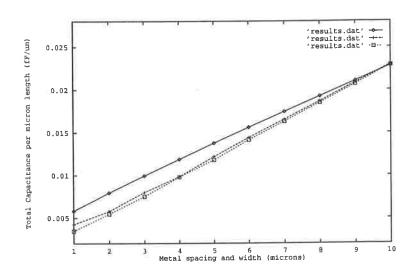

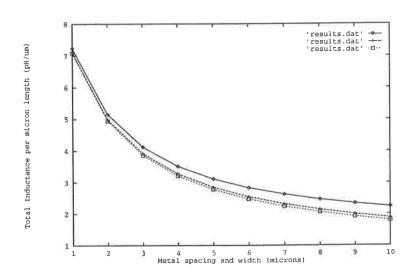

| 2.17 | Inter-nodal capacitance of two neighbouring wires on $100\mu m~[\epsilon_r=4(+)],$                                      |                 |

|      | $450\mu m~[\epsilon_r=4(\diamond)]$ and $100\mu m~[\epsilon_r=8(\sqcap)]$ thick GaAs SI substrate with a                |                 |

|      | backplane and dielectric constant for the inter-level dielectric                                                        | 43              |

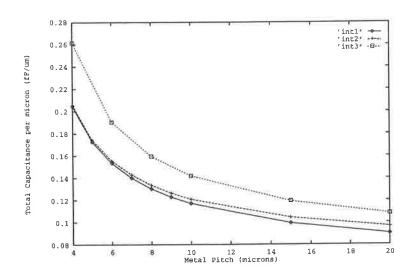

| 2.18 | Total capacitance of the centre $2\mu m$ wide wire on $100\mu m$ [ $\epsilon_r = 4(+)$ ],                               |                 |

|      | $450\mu m~[\epsilon_r=4(\diamond)]$ and $100\mu m~[\epsilon_r=8(\sqcap)]$ thick GaAs SI substrate with a                |                 |

|      | backplane and dielectric constant for the inter-level dielectric                                                        | 44              |

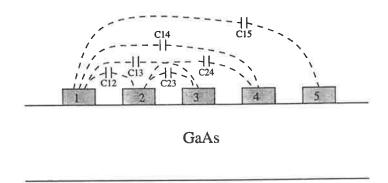

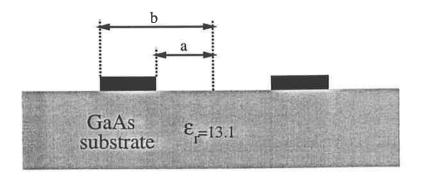

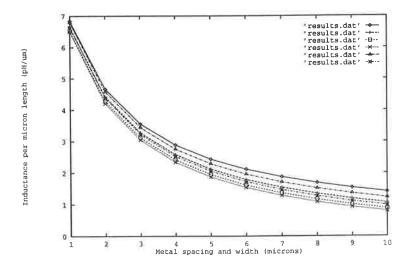

| 2.19 | Five equally spaced conductors on a GaAs substrate                                                                      | 45              |

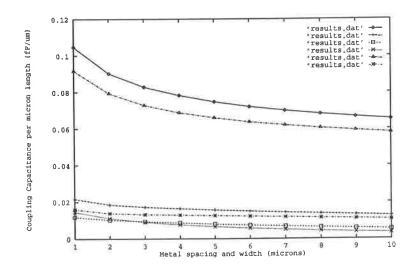

| 2.20 | Coupling capacitance between electrodes for 5 equal width and spacing                                                   |                 |

|      | electrodes on $100\mu m$ thick GaAs SI substrate embedded in dielectric ( $\epsilon_r =$                                |                 |

|      | 4), $2\mu m$ thick with a backplane metallisation ( $\diamond = C12, + = C13, \sqcap =$                                 |                 |

|      | $C14, \times = C15, \triangle = C23, * = C24).$                                                                         | 45              |

| 2.21 | $\Gamma$                               |                 |

|      | width and spacing electrodes on $100 \mu m$ thick GaAs SI substrate embedded                                            |                 |

|      | in dielectric ( $\epsilon_r = 4$ ), $2\mu m$ thick with a backplane metallisation                                       | 46              |

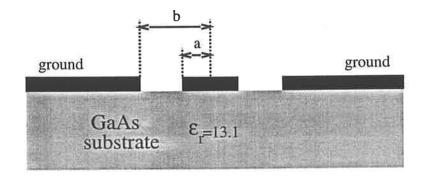

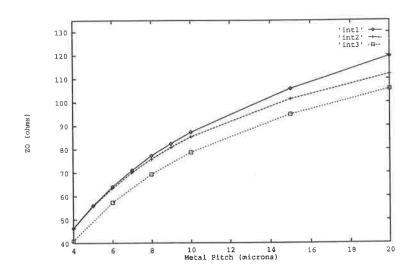

| 2.22 | Coplanar waveguide (cross section)                                                                                      | 46              |

|      | Coplanar strips (cross section)                                                                                         | 47              |

|      | Characteristic impedance of the centre $2\mu m$ wide wire on $100\mu m$ [ $\epsilon_r =$                                |                 |

|      | $4(\diamond)$ ], $450\mu m$ [ $\epsilon_r = 4(+)$ ] and $100\mu m$ [ $\epsilon_r = 8(\sqcap)$ ] GaAs SI substrate with  |                 |

|      | a backplane and dielectric constant for the inter-level dielectric                                                      | 48              |

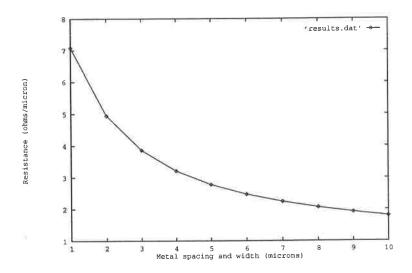

| 2.25 | Resistance $(10^{-2}\Omega/\mu m)$ of a wire as a function of design rule                                               | 50              |

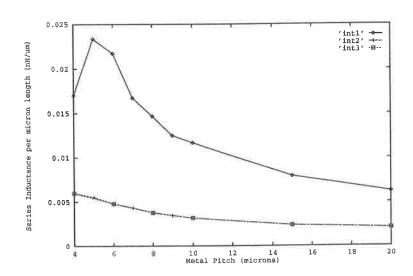

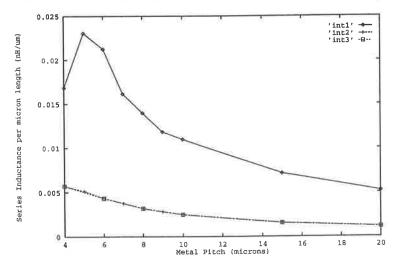

| 2.26 | Self plus mutual inductance of the centre $2\mu m$ wide wire on $100\mu m$ [ $\epsilon_r =$                             |                 |

|      | $4(+)$ ], $450\mu m$ [ $\epsilon_r = 4(\diamond)$ ] and $100\mu m$ [ $\epsilon_r = 8(\sqcap)$ ] thick GaAs SI substrate |                 |

|      | with a backplane and dielectric constant for the inter-level dielectric                                                 | 52              |

| 2.2  | 7 Mutual inductance of the centre $2\mu m$ wide wire on $100\mu m$ [ $\epsilon_r = 4(+)$ ],                             |                 |

|      | $450\mu m \ [\epsilon_r = 4(\diamond)]$ and $100\mu m \ [\epsilon_r = 8(\sqcap)]$ thick GaAs SI substrate with a        |                 |

|      | backplane and dielectric constant for the inter-level dielectric                                                        | $5\overline{2}$ |

| 2.28 | Self plus mutual inductance of 5 equal width and spaced interconnects on            |    |

|------|-------------------------------------------------------------------------------------|----|

|      | a $100\mu m$ GaAs SI substrate with a backplane ( $\diamond = L11 = L55, + = L22 =$ |    |

|      | $L33, \sqcap = L33$ )                                                               | 53 |

| 2.29 | Mutual inductance of 5 equal width and spaced interconnects on a $100\mu m$         |    |

|      | GaAs SI substrate with a backplane ( $\diamond$ = L12, + = L13, $\sqcap$ = L14,     |    |

|      | $\times = L15, \Delta = L23, * = L24).$                                             | 53 |

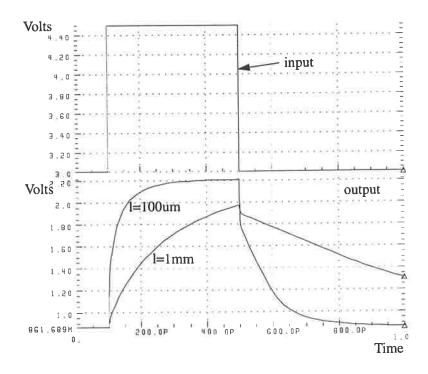

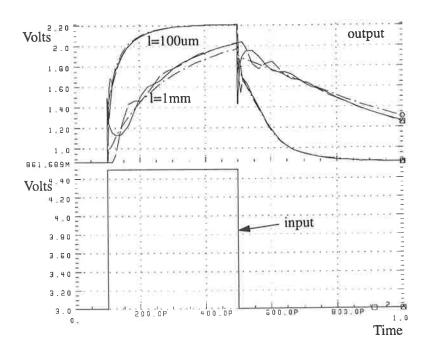

| 2.30 | Transient analysis of a $100\mu m$ and $1mm$ line modelled as a lumped capacitor.   | 55 |

| 2.31 | Transient analysis of a $100\mu m$ and $1mm$ line modelled as a lossy TL and        |    |

|      | a lumped capacitor                                                                  | 56 |

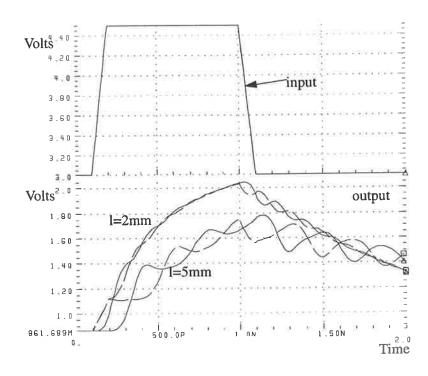

| 2.32 | Transient analysis of a 2mm and a 5mm line modelled as a lossy TL                   |    |

|      | (signals plotted at start and end of the TL)                                        | 57 |

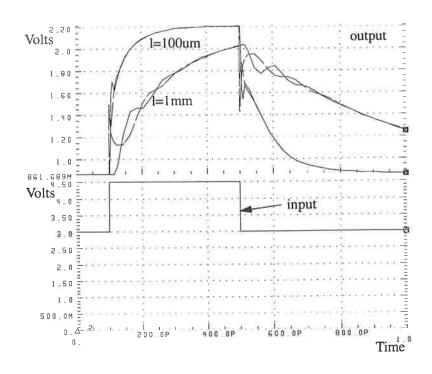

| 2.33 | Transient analysis of a $100\mu m$ and $1mm$ line modelled as a lossless TL         | 58 |

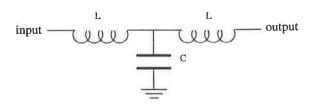

| 2.34 | Equivalent model for a LCC pad and bond, $L=1.4nH,\ C=40fF.$                        | 59 |

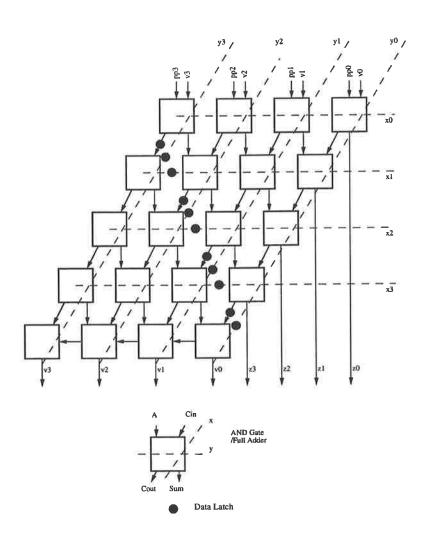

| 0.1  | A ' limit four hit non digit multiplier                                             | 66 |

| 3.1  | A pipelined four-bit per digit multiplier                                           |    |

| 3.2  | A pipelined four-bit per digit multiplier optimised for both area and crit-         | 67 |

|      | ical path.                                                                          | 68 |

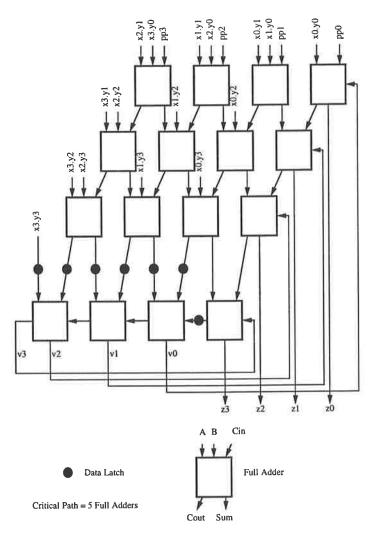

| 3.3  | A digit-serial multiplier array.                                                    | 69 |

| 3.4  | A digit—serial multiplier cell                                                      | 73 |

| 3.5  | Operand movement through a four cell linear array of recurrence cells.              | 10 |

| 3.6  | Operand movement through a modified four cell linear array of recurrence            | 79 |

|      | cells.                                                                              | 73 |

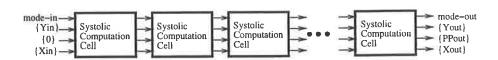

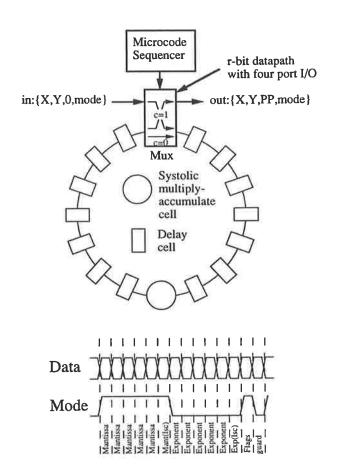

| 3.7  | The systolic ring multiply/accumulate processing element                            | 75 |

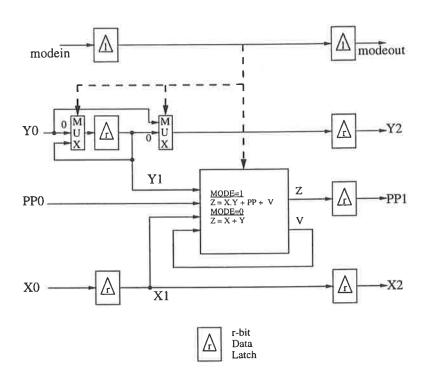

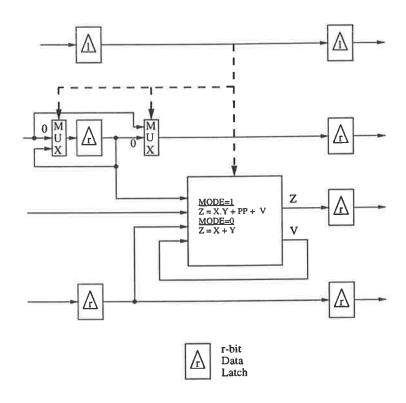

| 3.8  | The systolic multiply/accumulate cell                                               | 78 |

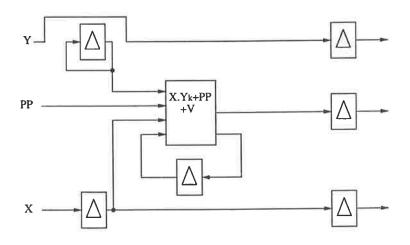

| 3.9  | The logical function of the systolic cell during multiplication                     | 78 |

| 3.10 | The logical function of the systolic cell during denormalisation                    | 79 |

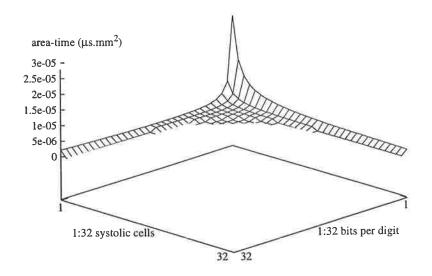

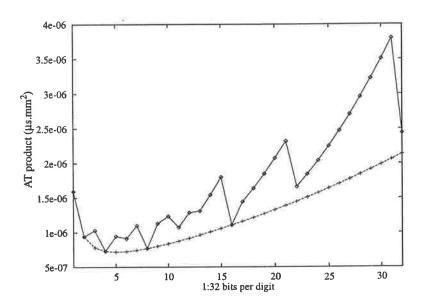

| 3.11 | 1 The $AT$ metric for the systolic ring multiplier                                  | 84 |

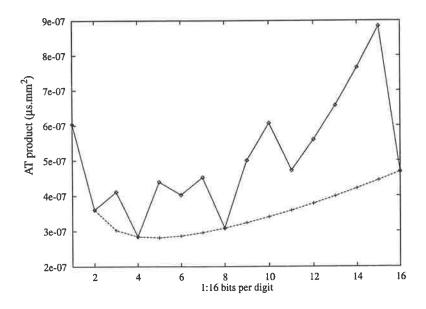

| 3.12 | 2 The AT metric for the systolic ring multiplier for a continuous model and         |    |

|      | a constrained model with the maximum number of systolic cells versus the            |    |

|      | number of bits per digit for $m = 32$ and $e = 16$                                  | 85 |

| 3.13 | The AT metric for the systolic ring multiplier for a continuous model and                 |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | a constrained model with the maximum number of systolic cells versus the                  |     |

|      | number of bits per digit for $m = 64$ and $e = 16$                                        | 85  |

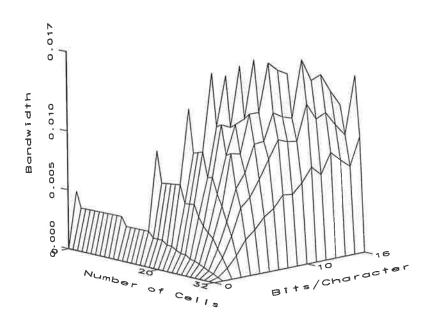

| 3.14 | The bandwidth metric for the systolic ring processing element under the                   |     |

|      | constraint of constant area.                                                              | 86  |

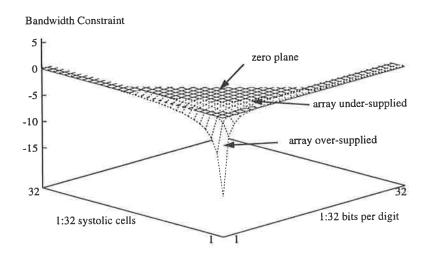

| 3.15 | The bandwidth constraint for the systolic ring processing element for ten                 |     |

|      | million gates                                                                             | 87  |

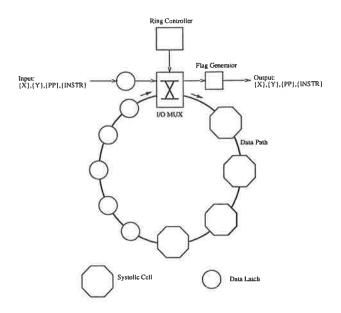

| 4.1  | Processing element architecture                                                           | 91  |

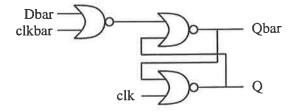

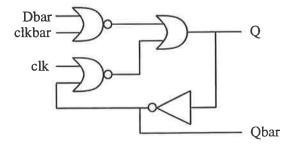

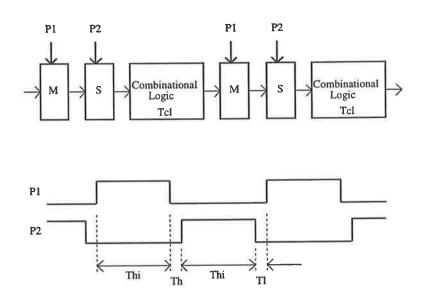

| 4.2  | Master-slave half latch (1)                                                               | 92  |

| 4.3  | Master-slave half latch (2)                                                               | 92  |

| 4.4  | Master-slave half latch (3)                                                               | 93  |

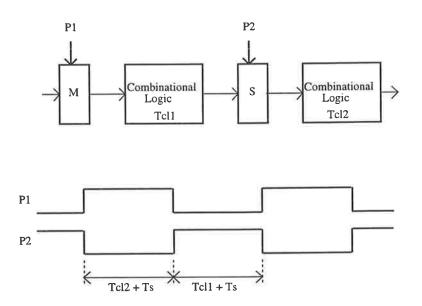

| 4.5  | Clock Scheme 1                                                                            | 93  |

| 4.6  | Clock Scheme 2                                                                            | 94  |

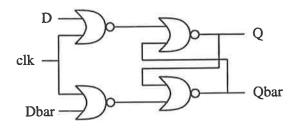

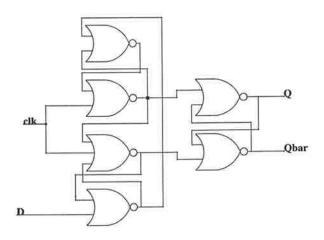

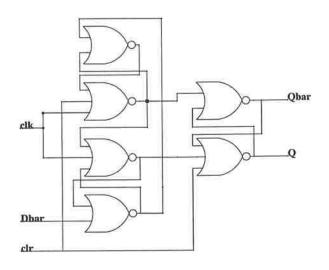

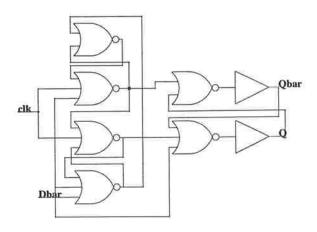

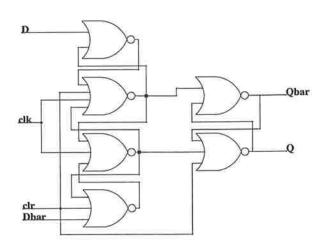

| 4.7  | Data flip-flop 1: Schematic of a 6-NOR data flip-flop with a single input.                | 95  |

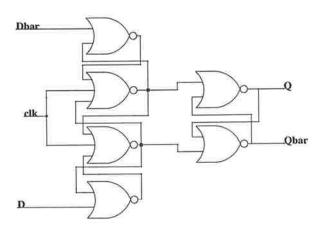

| 4.8  | Data flip-flop 2: Schematic of a 6-NOR data flip-flop with $D$ and $\overline{D}$ inputs. |     |

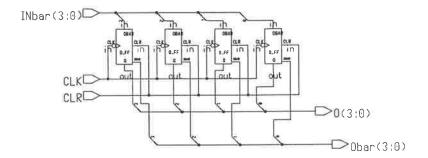

| 4.9  | Data flip-flop 3: Schematic of a 6-NOR data flip-flop with clear                          | 96  |

| 4.10 | • •                                                                                       | 96  |

| 4.11 | Data flip-flop 5: Schematic of a 6-NOR data flip-flop with clear, D and                   | i   |

|      | $\overline{D}$ inputs                                                                     | 97  |

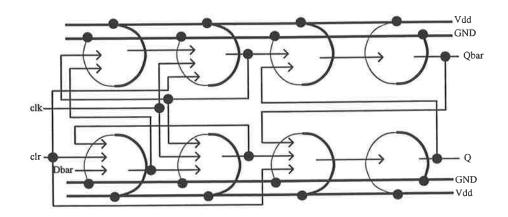

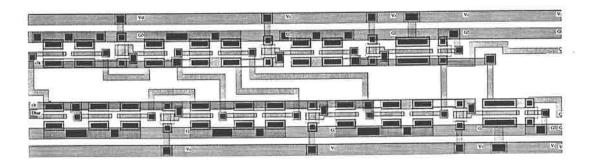

|      | Ring notation of a GaAs data flip-flop with clear or preset                               | 98  |

|      | Layout of a GaAs data flip-flop using ring notation                                       | 98  |

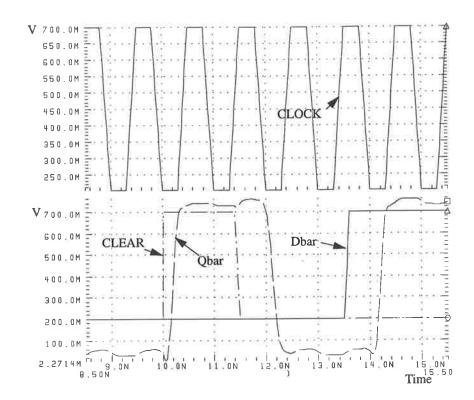

| 4.14 | SPICE transient response simulation of a GaAs data flip-flop with a 1 GHz                 |     |

|      | clock                                                                                     | 99  |

|      | Final version of the data flip-flop schematic with clear                                  | 100 |

|      | 3 Toggle flip-flop layout                                                                 | 100 |

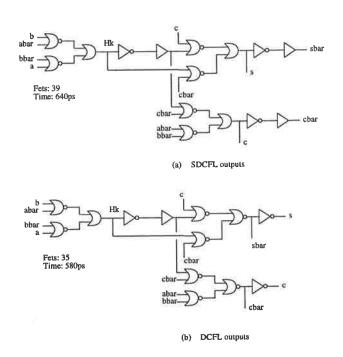

| 4.17 | 7 SDCFL implementation of a full adder using adder half equations with (a)                |     |

|      | SDCFL outputs and (b) DCFL outputs                                                        | 101 |

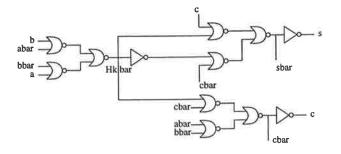

| 4.18 | 8 DCFL implementation of a full adder using adder half equation with DCFL                 |     |

|      | outputs                                                                                   | 101 |

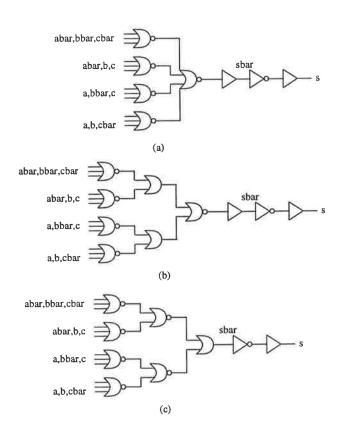

| 4.19 | 9 Full adder sum generation circuits                                                      | 102 |

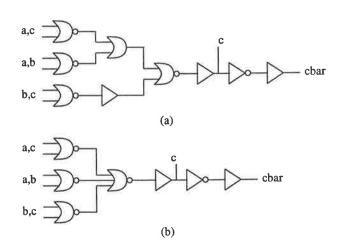

| 1.20 | O Full adder carry generation circuits                                                    | 103 |

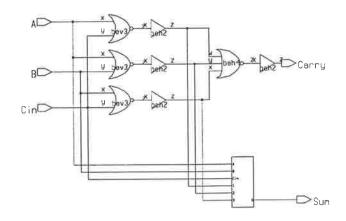

| 1.21  | Carry generation circuit used in the final design                                | 104   |

|-------|----------------------------------------------------------------------------------|-------|

| 1.22  | Sum generation circuit used in the final design.                                 | 105   |

| 1.23  | Full adder layout                                                                | 105   |

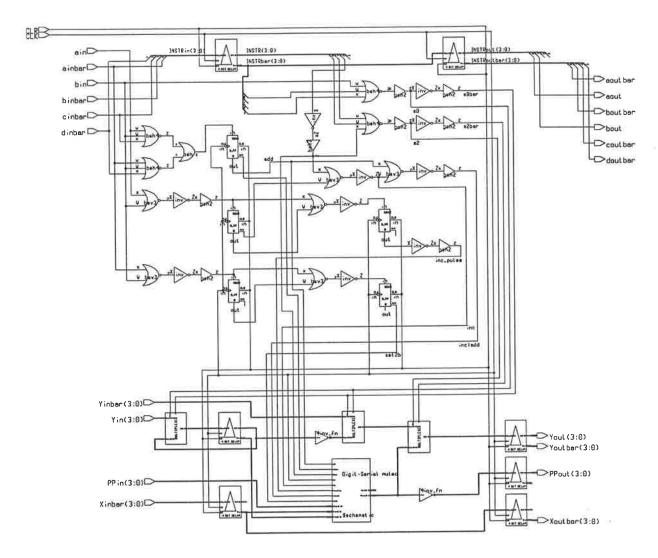

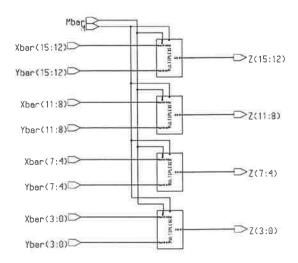

|       | Nibble-serial multiplier schematic                                               | 108   |

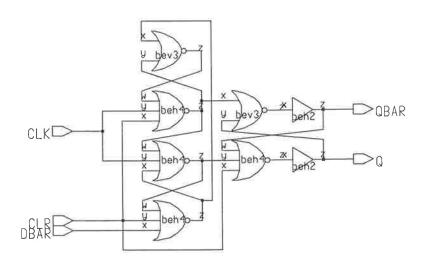

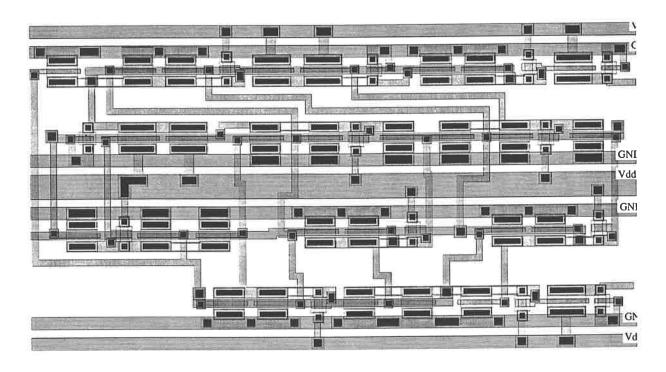

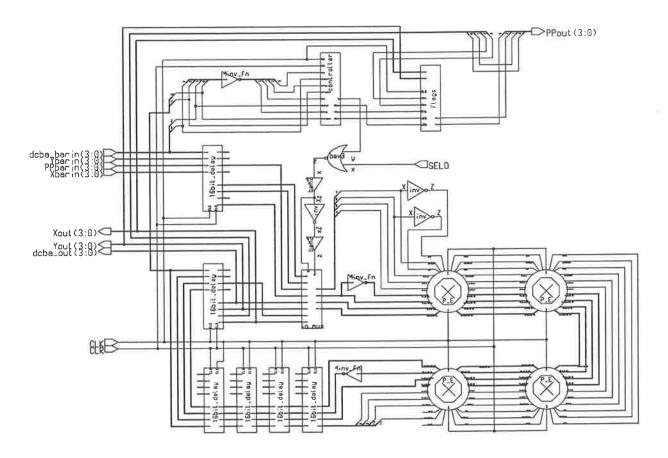

|       | Schematic of the systolic cell                                                   | 109   |

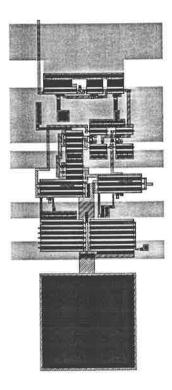

| 4.26  | Layout of the systolic cell                                                      | 109   |

| 4.27  | SPICE simulation of the critical path through the digit-serial multiplier.       | 110   |

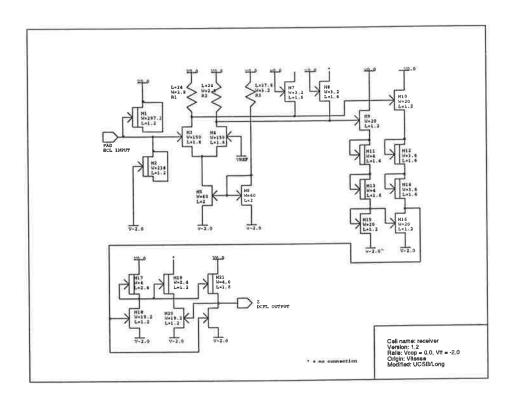

| 4.28  | Schematic of the input pad                                                       | 111   |

| 4.29  | Layout of the input pad                                                          | 111   |

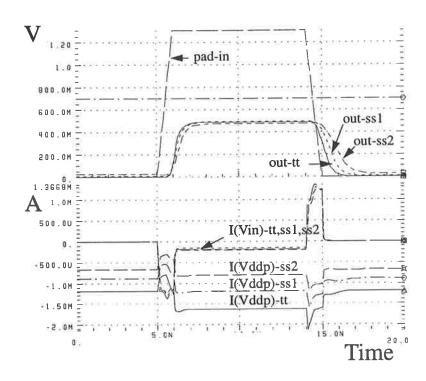

| 4.30  | Simulation of an input pad receiver with VREF= 0.7V showing input,               |       |

|       | output response and the current drawn using typical-typical, slow-slow-1         |       |

|       | and $slow$ - $slow$ - $2$ process parameters                                     | 112   |

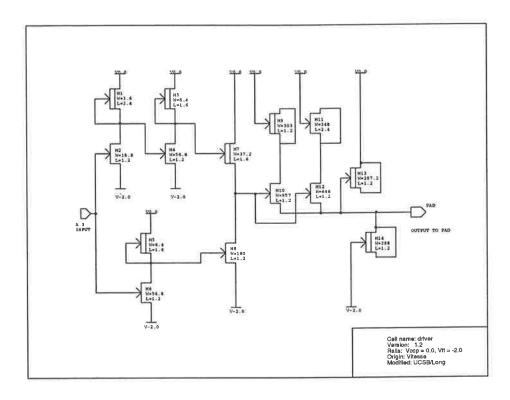

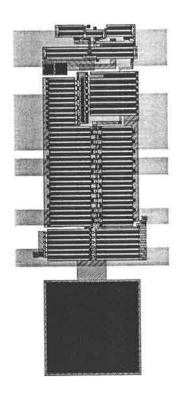

| 4.31  | Schematic of the output pad                                                      | 113   |

| 4.32  | Layout of the output pad                                                         | 114   |

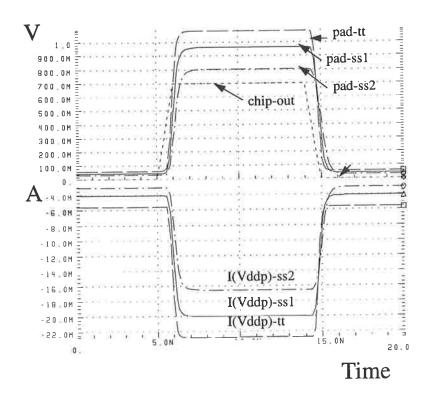

| 4.33  | Simulation of an output pad showing the voltage response and current             |       |

|       | drawn for $typical-typical$ , $slow-slow-1$ and $slow-slow-2$ process parameters | . 114 |

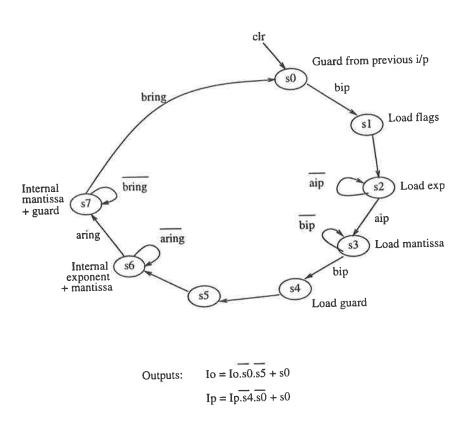

| 4.34  | State transition diagram for the ring controller                                 | 115   |

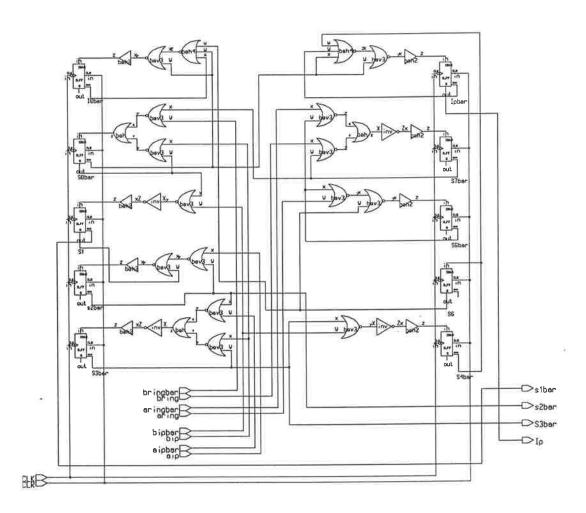

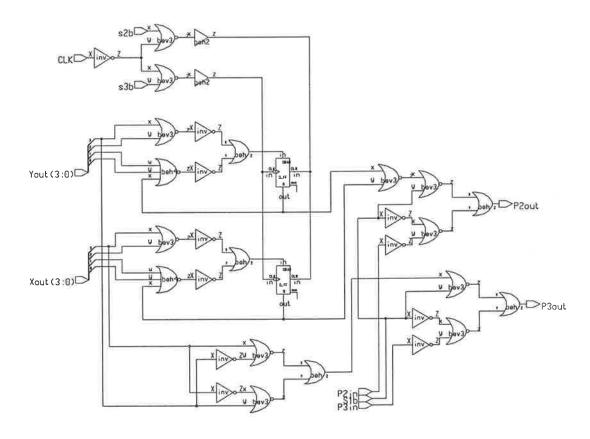

|       | Circuit schematic of the ring controller                                         | 116   |

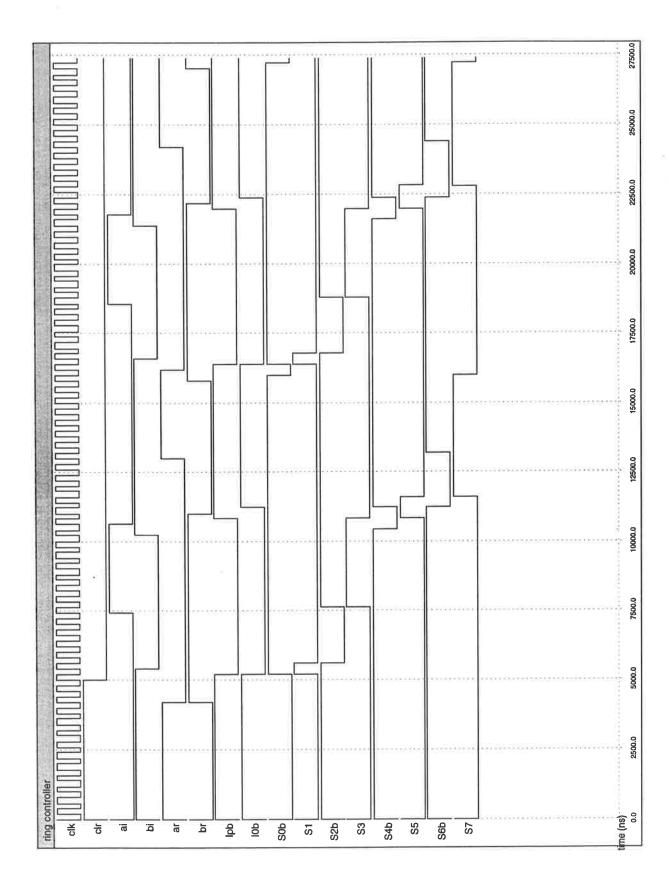

| 4.36  | Functional simulation of the ring controller using IRSIM                         | 117   |

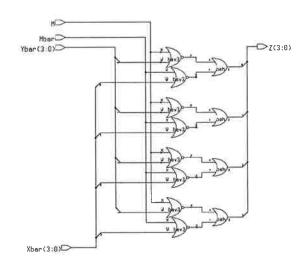

| 4.37  | aSchematic of a 4-bit multiplexer                                                | 118   |

|       | bSchematic of the I/O multiplexer                                                | 118   |

| 4.38  | Schematic of the flag generation circuit                                         | 120   |

|       | Layout of the flag generation circuit                                            | 120   |

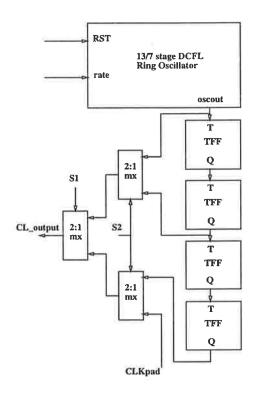

|       | Clock architecture                                                               | 121   |

|       | Clock generator layout                                                           | 121   |

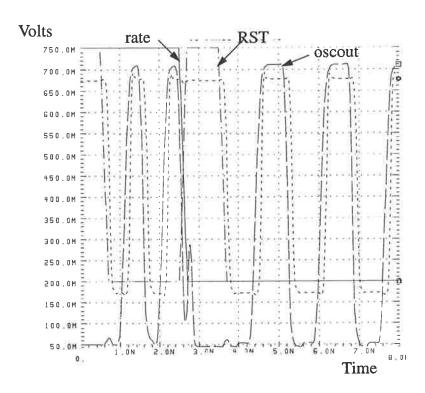

|       | 2 Clock generator transient simulation for two clock rates                       | 122   |

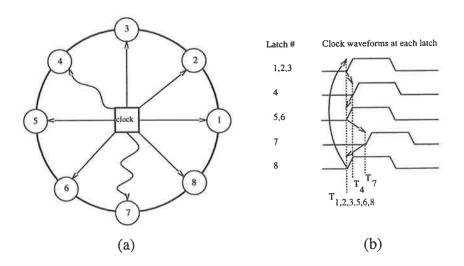

| 4.43  | 3 (a) A clocked ring where the arrows indicate the delay from the clock          |       |

|       | generator to the latch, (b) Clock timing where arrows indicate clock skew        |       |

|       | between adjacent latches                                                         | 124   |

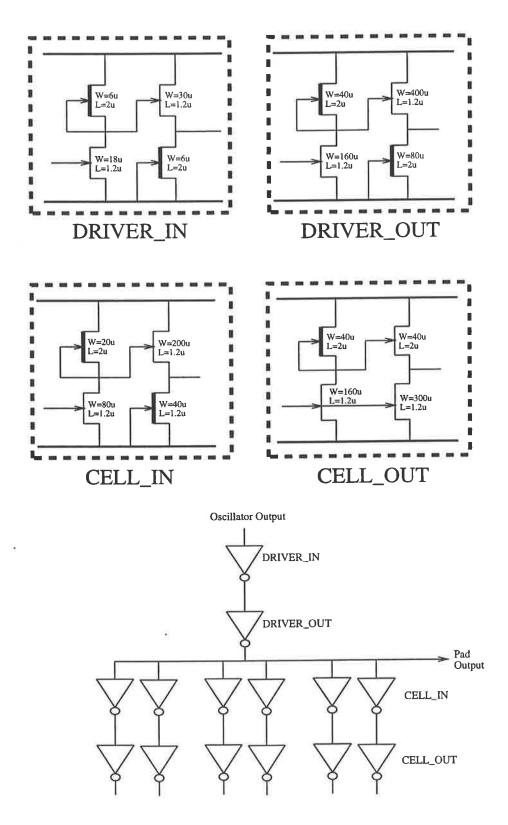

| 4.44  | 4 Two stages of super buffers used to drive the clock tree                       | 125   |

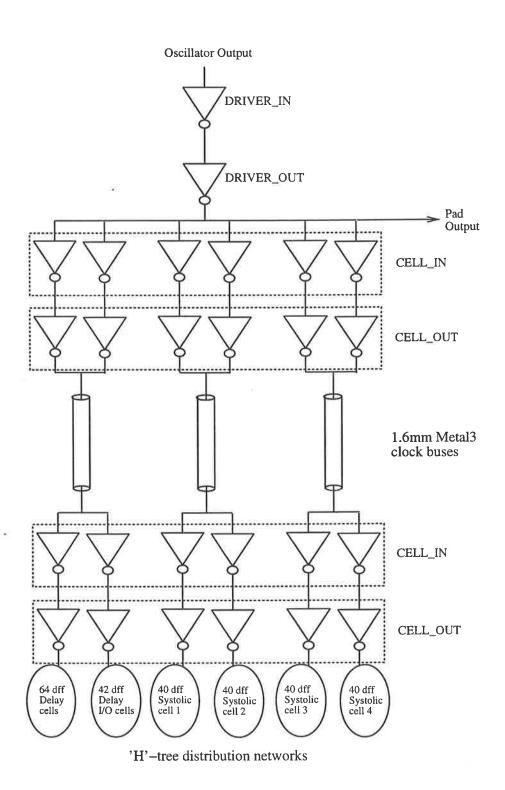

| A A ! | Schemetic of the simulated clock distribution network.                           | 126   |

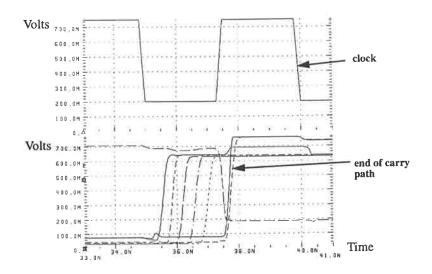

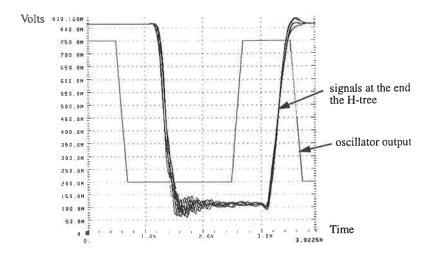

| 4 46 | SPICE simulation of the clock distribution across the chip                                  | 127 |

|------|---------------------------------------------------------------------------------------------|-----|

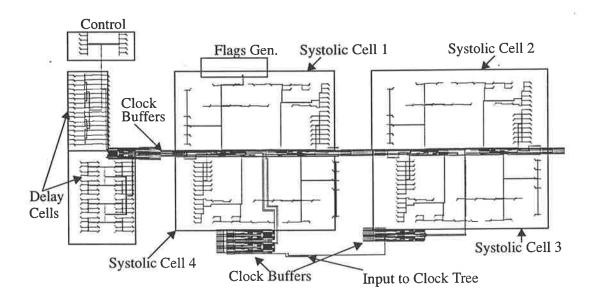

|      | Layout of the clock distribution circuit                                                    | 127 |

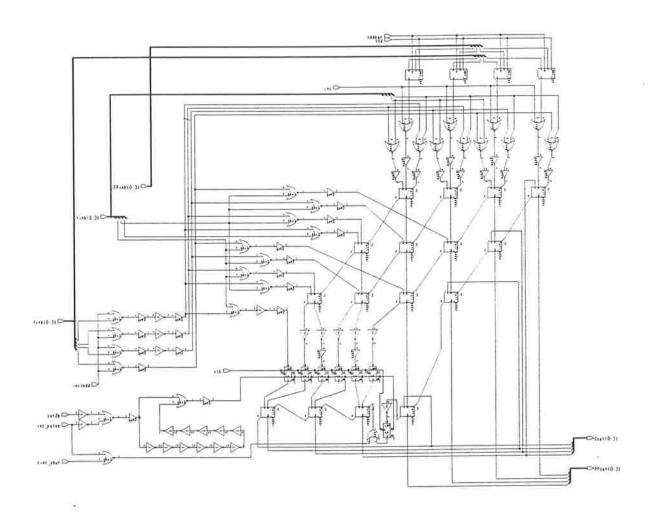

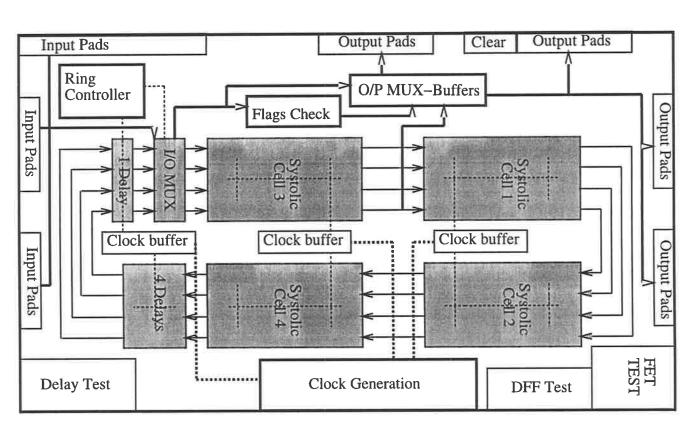

|      | Schematic of the systolic ring processing element                                           | 129 |

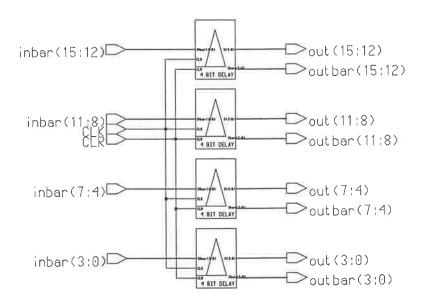

|      | A 4-bit delay element                                                                       | 129 |

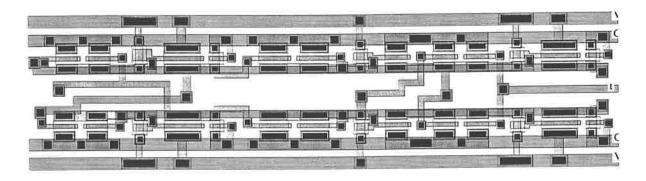

|      | A 16-bit delay element used in the systolic ring                                            | 130 |

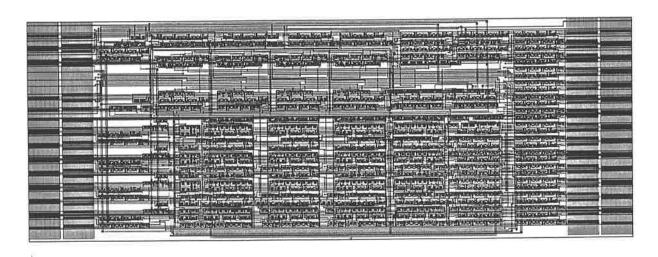

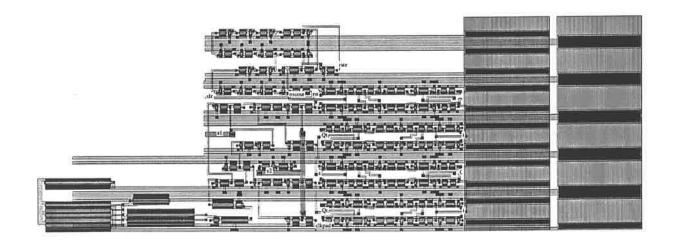

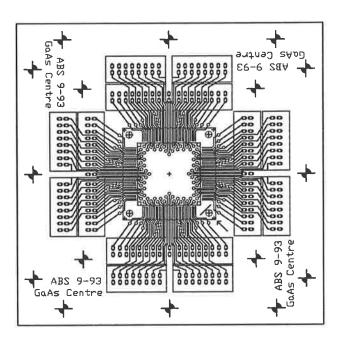

|      | Floorplan of the processing element chip including test structures                          | 131 |

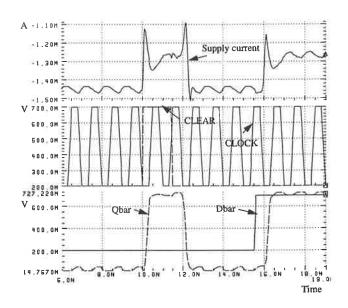

|      | 2 Data flip-flop simulation showing supply current                                          | 133 |

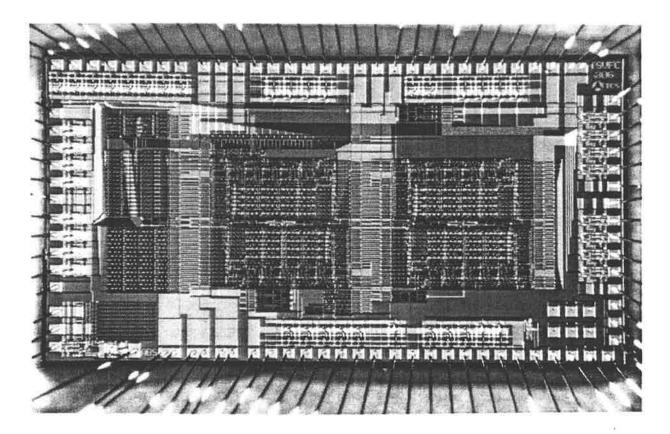

|      | 3 Micrograph of the fabricated GaAs systolic PE chip with the floorplan                     |     |

| 4.00 | overlaid                                                                                    | 134 |

|      | overlaid                                                                                    |     |

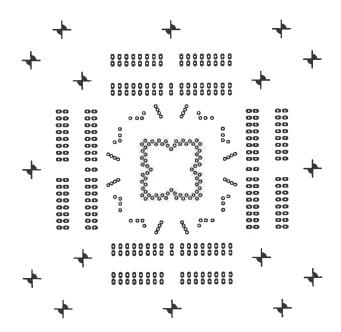

| 5.1  | Top layer of the test fixture PCB                                                           | 136 |

| 5.2  | Bottom layer negative of the test fixture PCB                                               | 137 |

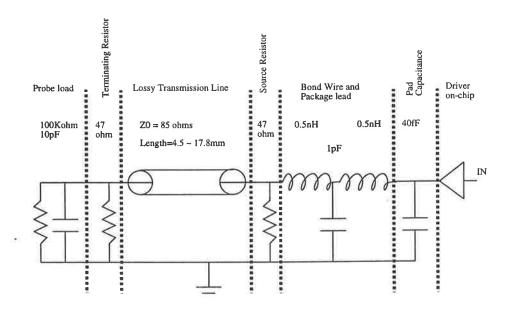

| 5.3  | Equivalent circuit of a signal driven off chip                                              | 138 |

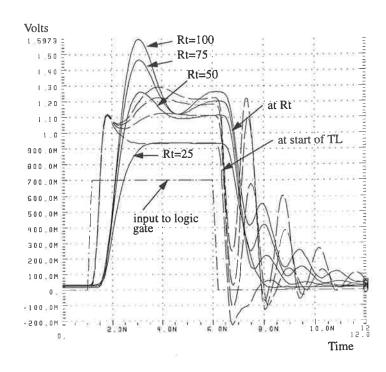

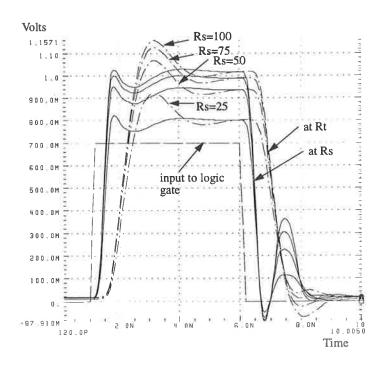

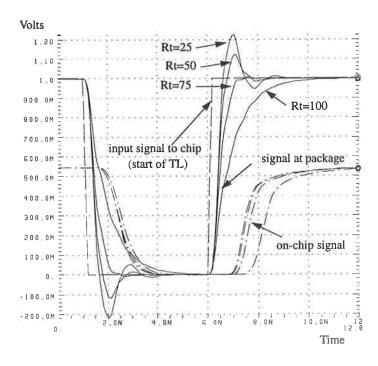

| 5.4  | Simulation of a $40mm$ long line with no $Rs$ and $Rt = 25$ , $50$ , $75$ and $100\Omega$ . | 140 |

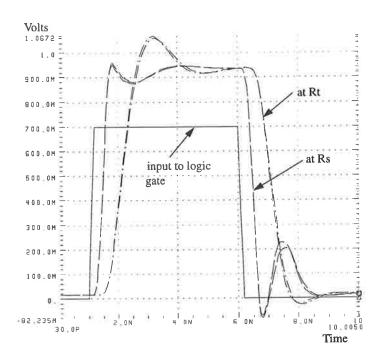

| 5.5  | Simulation of a $40mm$ long line with $Rt = 50\Omega$ and $Rs = 25, 50, 75$ and             |     |

|      | $100\Omega$                                                                                 | 140 |

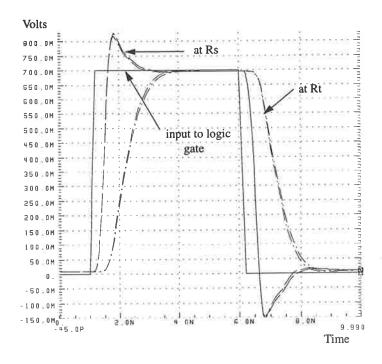

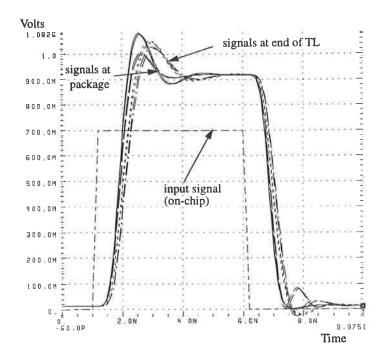

| 5.6  | Simulation of a $40mm$ long line with $Rt = 50\Omega$ and $Rs = 50\Omega$ for track         |     |

|      | widths of $0.3048mm$ , $0.381mm$ and $0.5mm$                                                | 141 |

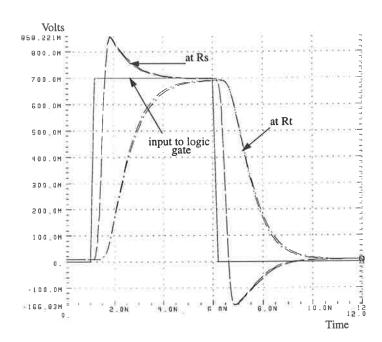

| 5.7  | Simulation of a $40mm$ long line with $Rt=25\Omega$ and $Rs=25\Omega$ for track             |     |

|      | widths of 0.3048mm, 0.381mm and 0.5mm                                                       | 141 |

| 5.8  | Simulation of a $40mm$ long line with $Rt=25\Omega$ and $Rs=25\Omega$ for track             |     |

|      | widths of $0.3048mm$ , $0.381mm$ and $0.5mm$ . The PCB is $\frac{1}{16}$ " thick            | 142 |

| 5.9  | Simulation of a $40mm$ long line with $Rt = 25, 50, 75$ and $100\Omega$ , signal is         |     |

|      | being driven onto the chip                                                                  | 142 |

| 5.1  | 10 Simulation of the four possible interconnect types on the PCB with $47\Omega$            |     |

|      | source and terminating resistors.                                                           | 143 |

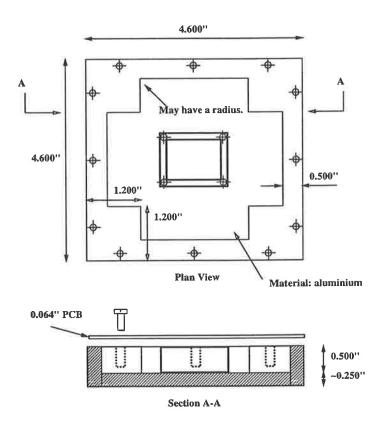

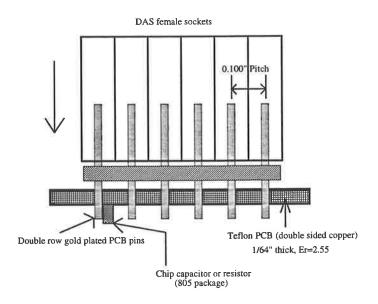

| 5    | 11 High speed test jig for 132/64 MLC packages                                              | 144 |

| 5.   | 12 Cross section through the PCB                                                            | 145 |

| 5.   | 13 Photograph of the high speed test jig with a chip and heat-sink installed.               | 145 |

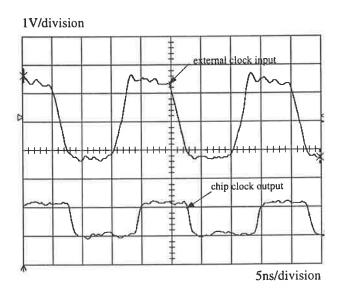

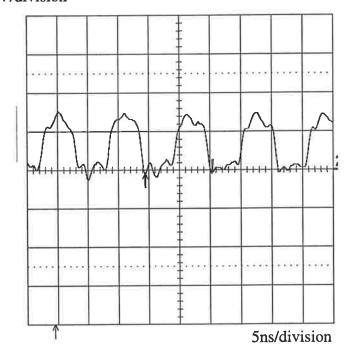

| 5.   | 14 External clock input and chip clock output waveforms                                     | 147 |

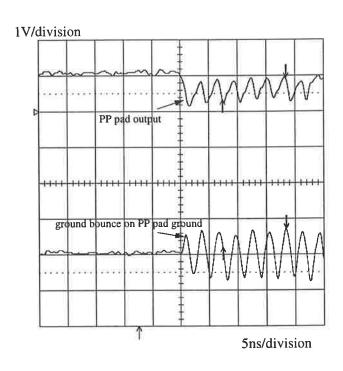

|      | 15 Signal p2out and the pad ground showing ground bounce                                    |     |

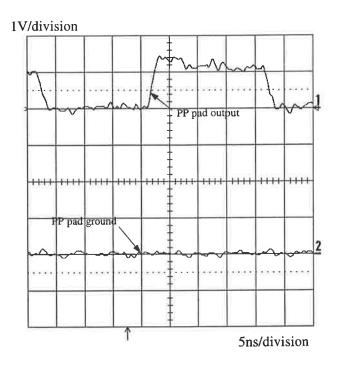

|      | 16 Signal p2out and the pad ground with the ground bounce solved                            |     |

| 5.17 | Layout of a fingered enhancement mode MESFET (5 fingers $\times$ 74.8 $\mu$ wide).                                              | 150        |

|------|---------------------------------------------------------------------------------------------------------------------------------|------------|

|      | Layout of a fingered depletion mode MESFET (5 fingers $\times$ 74.8 $\mu m$ wide).                                              |            |

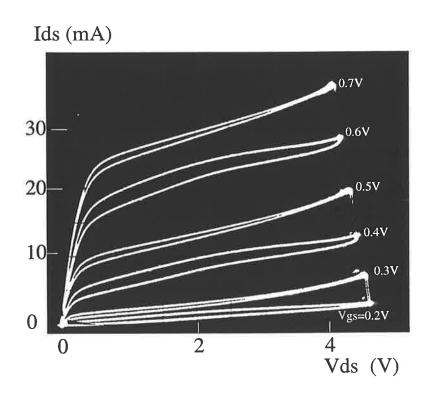

|      | Photograph of the EFET I-V characteristics from the curve tracer                                                                | 151        |

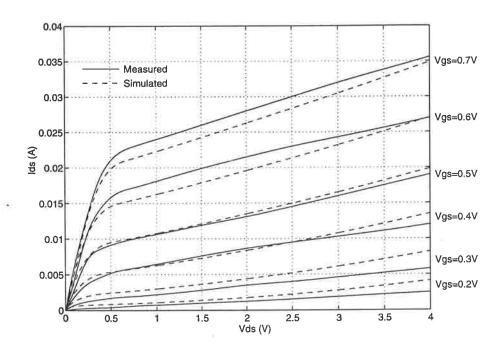

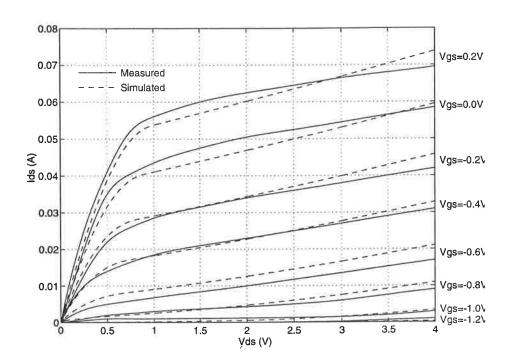

|      | Comparison of measured and simulated EFET I-V characteristics using                                                             |            |

|      | typical process parameters                                                                                                      | 152        |

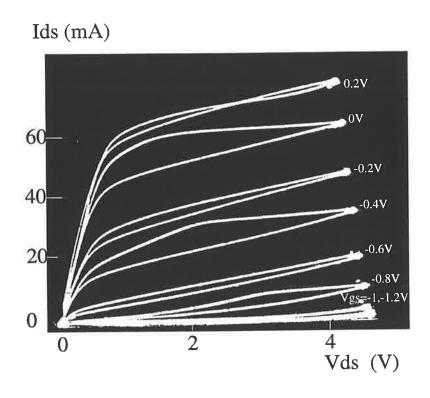

| 5.21 | Photograph of the DFET I-V characteristics from the curve tracer                                                                | 153        |

|      | Comparison of measured and simulated DFET I-V characteristics                                                                   | 154        |

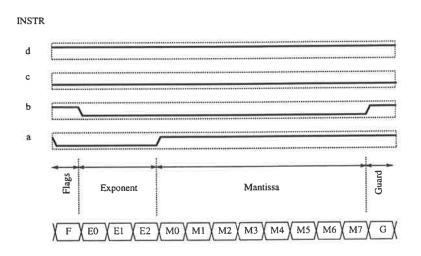

| 5.23 | Instruction nibble for multiplication mode.                                                                                     | 155        |

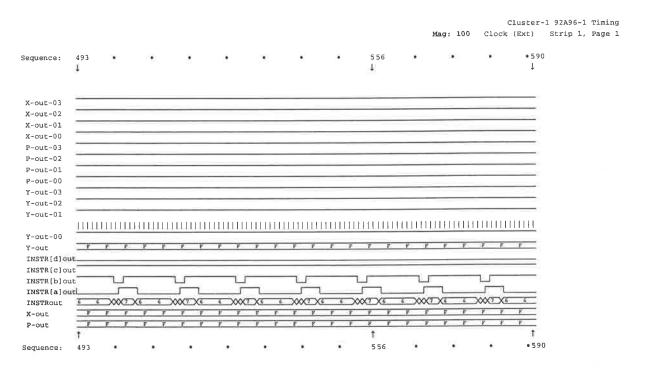

| 5.24 | Systolic cell testing in multiplication mode at 50MHz (zero by zero)                                                            | 156        |

| 5.25 | Systolic cell testing in multiplication mode at 50MHz                                                                           | 157        |

| 5.26 | Results of the systolic cell in multiplication mode at 50MHz                                                                    | 157        |

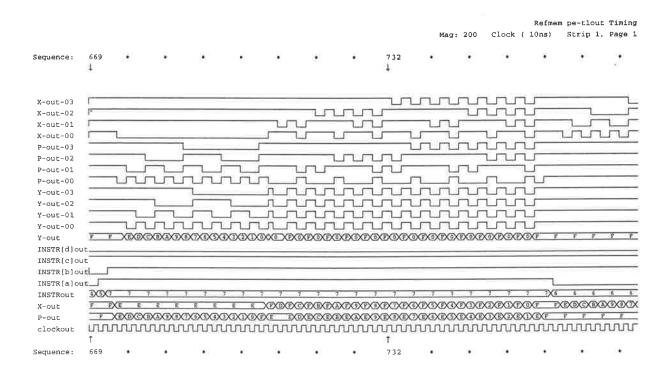

| 5.27 | Test results of the PE in floating point addition mode at 128MHz                                                                | 159        |

| 5.28 | Test results of the PE in floating point denormalisation mode at 128MHz.                                                        | 160        |

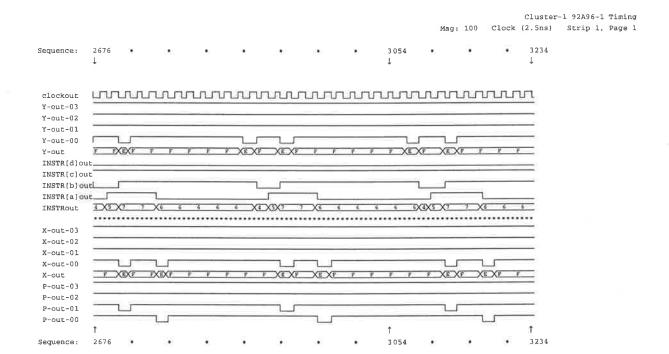

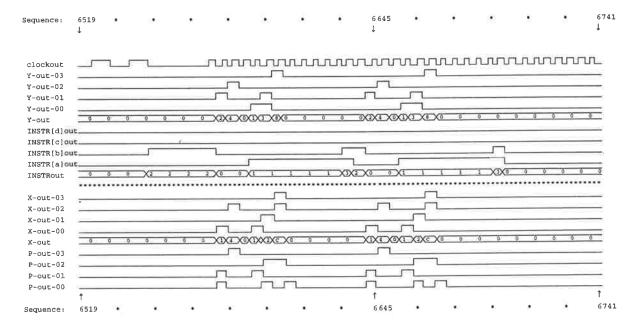

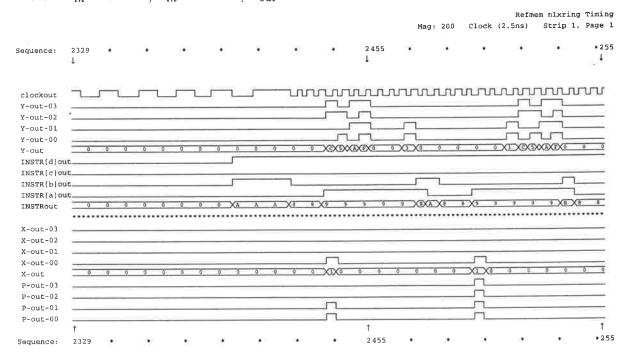

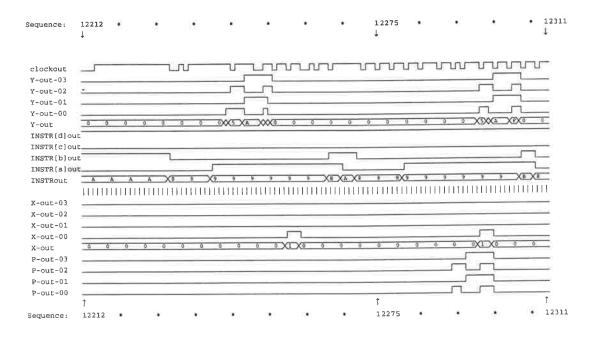

| 5.29 | aSystolic ring operating in floating point multiplication mode at 91MHz                                                         |            |

|      | where $X_{in} = 0 \times e^0$ , $Y_{in} = 0 \times e^0$ , $P_{out} = 0 \times e^0$                                              | 161        |

| 5.29 | bSystolic ring operating in floating point multiplication mode at 91MHz                                                         |            |

|      | where $X_{in} = 0.00000001 \times e^0$ , $Y_{in} = 0.FA5C3000 \times e^0$ and $P_{out} = 0.0000000000000000000000000000000000$  | 7×         |

|      | $e^0$ ,                                                                                                                         | 161        |

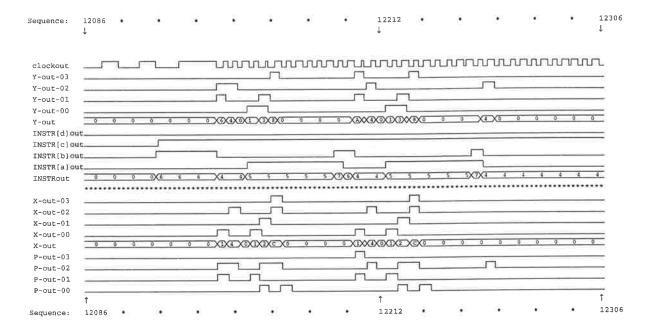

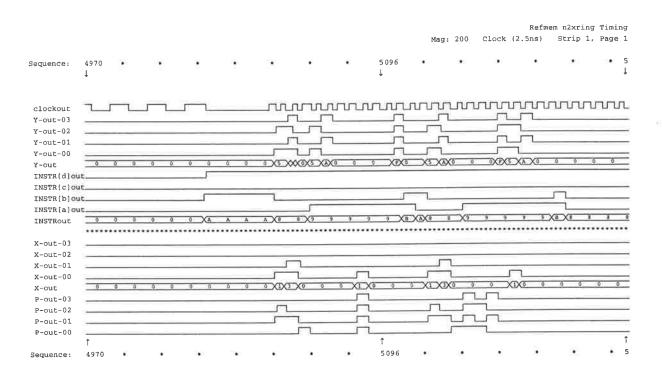

| 5.29 | cSystolic ring operating in floating point multiplication mode at 91MHz                                                         |            |

|      | . where $X_{in} = 0.00010000 \times e^{031}, Y_{in} = 0.00A5F100 \times e^{0F5}$ and $P_{out} =$                                |            |

|      | $0.000000A5F \times e^{126}$                                                                                                    | 162        |

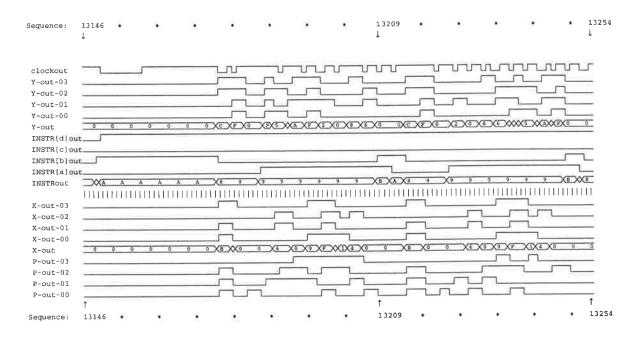

| 5.29 | dSystolic ring operating in floating point multiplication mode at 91MHz                                                         |            |

|      | where $X_{in} = 0.00010488 \times e^{0.031}$ , $Y_{in} = 0.00A5F000 \times e^{0.05}$ and $P_{out} = 0.00A5F000 \times e^{0.05}$ |            |

|      | $0.000000A8D \times e^{126}$                                                                                                    | 162        |

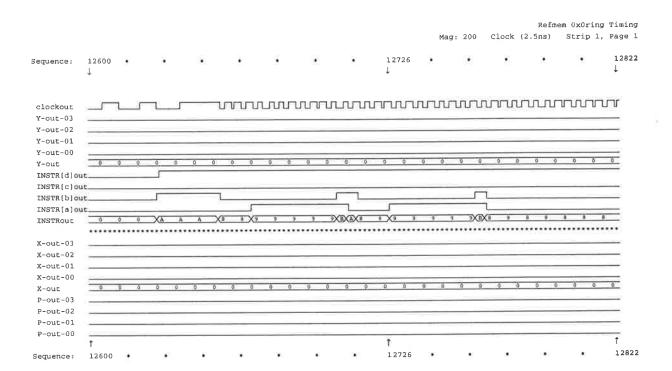

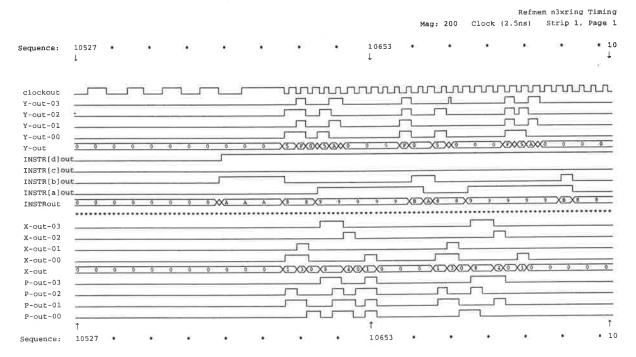

| 5.30 | DaSystolic ring operating in floating point multiplication mode at 128MHz                                                       |            |

|      | where $X_{in} = 0 \times e^0$ , $Y_{in} = 0 \times e^0$ and $P_{out} = 0 \times e^0$                                            | 163        |

| 5.30 | ObSystolic ring operating in floating point multiplication mode at 128MHz                                                       |            |

|      | where $X_{in} = 0.00100000 \times e^0$ , $Y_{in} = 0.FA500000 \times e^0$ and $P_{out} = 0.000FA500000 \times e^0$              | $\times 0$ |

|      | .0                                                                                                                              | 163        |

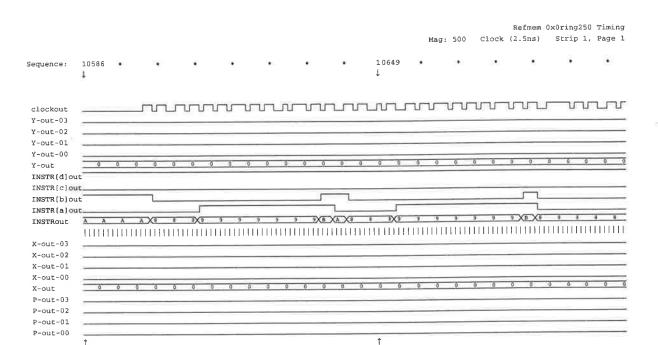

| 5.30c       | Systolic ring operating in floating point multiplication mode at 128MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|             | where $X_{in}=041F9060\times e^{00B},\ Y_{in}=FA5F6802\times e^{0FC}$ and $P_{out}=0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|             | $0.04085C612 \times e^{107} \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 164  |

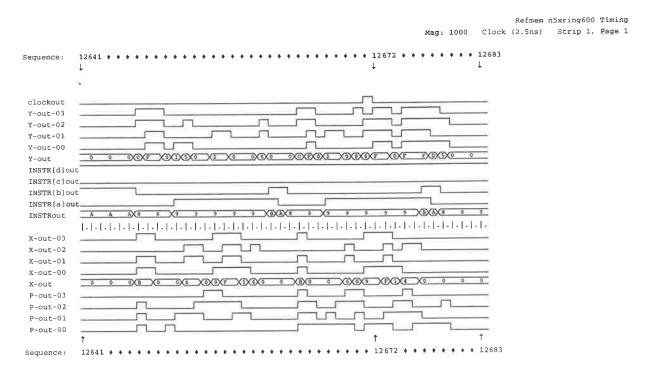

| 5.31        | Test results of the PE in floating point multiplication mode at 350MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 164  |

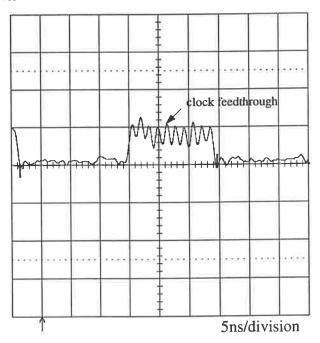

| 5.32        | Clock generator set for 37.5MHz operation showing feedthrough from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|             | source ( $Vdd = 1.89 V$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 165  |

| 5.33        | Clock generator set for 150MHz operation showing measured frequency of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|             | 91 <i>MHz</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 166  |

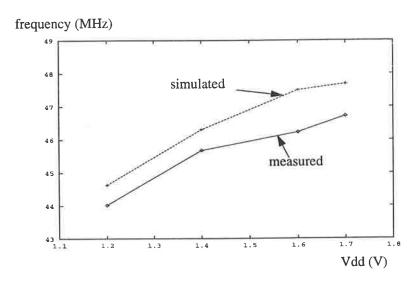

| 5.34        | Variation of clock frequency with power supply voltage for $CKrate = 1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 167  |

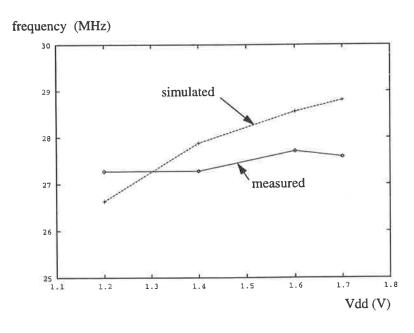

| 5.35        | Variation of clock frequency with power supply voltage for $CKrate = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 167  |

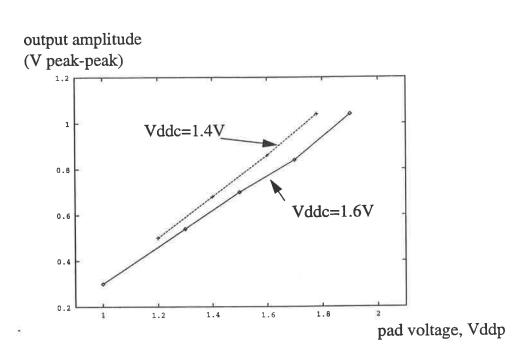

| 5.36        | Variation of peak-peak output voltage with pad power supply voltage for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|             | Vddc = 1.6 V, $CKrate = 1$ and $Vddc = 1.4 V$ , $CKrate = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 168  |