# Threshold Logic Based Implementation of High Performance VLSI Arithmetic Circuits

by

#### Peter Celinski

B.E. (Electrical & Electronic Engineering, with Honors), The University of Adelaide, Australia, 1998

Thesis submitted for the degree of

**Doctor of Philosophy**

in

Electrical and Electronic Engineering University of Adelaide

December, 2006

© 2006 Peter Celinski All Rights Reserved

# **Contents**

| Contents    |                                             | iii  |

|-------------|---------------------------------------------|------|

| Abstract    |                                             | vii  |

| Statemen    | nt of Originality                           | ix   |

| Acknowle    | edgments                                    | хi   |

| Conventi    | ons                                         | xiii |

| Publication | ons                                         | χV   |

| List of Fi  | gures                                       | xix  |

| List of Ta  | ables                                       | xiii |

| Chapter :   | 1. Introduction                             | 1    |

| 1.1         | Context and Technology                      | 2    |

| 1.2 Т       | Threshold Logic                             | 3    |

| 1.3 Т       | Thesis Overview and Organization            | 6    |

| 1.4         | Original Contributions                      | 7    |

| Chapter 2   | 2. Threshold Logic Arithmetic               | 9    |

| 2.1         | Neural Computation                          | 10   |

| 2.2         | Γhreshold Logic vs. Conventional Logic      | 10   |

| 2.3         | Threshold Logic Addition and Multiplication | 14   |

| 2           | 2.3.1 Addition Networks                     | 14   |

| 2           | 2.3.2 Multiplication Networks               | 18   |

| 2.4 (       | Chapter Summary                             | 20   |

| Chapter     | 3. Threshold Logic Circuit Implementations  | 21   |

| 3.1     | Thresh  | nold Gate Implementations                                         | 22 |

|---------|---------|-------------------------------------------------------------------|----|

|         | 3.1.1   | Voltage/Charge Mode TL Gates                                      | 23 |

|         | 3.1.2   | Current/Conductance Mode TL Gates                                 | 26 |

|         | 3.1.3   | Other Gate Implementations                                        | 29 |

|         | 3.1.4   | Gate Implementation Comparison                                    | 29 |

|         | 3.1.5   | Design Considerations                                             | 35 |

|         | 3.1.6   | TL Based System Implementations                                   | 37 |

| 3.2     | Chapt   | er Summary                                                        | 38 |

| Chapter | 4. Ca   | pacitive Threshold Logic Circuit Techniques                       | 41 |

| 4.1     | Charg   | e Recycling Threshold Logic                                       | 42 |

| 4.2     | Self Ti | med Threshold Logic                                               | 45 |

| 4.3     | Delay   | Modeling                                                          | 48 |

|         | 4.3.1   | Logical Effort                                                    | 48 |

|         | 4.3.2   | CRTL Delay Model                                                  | 51 |

|         | 4.3.3   | Applying the Model—Design Comparison Examples $\ \ldots \ \ldots$ | 54 |

| 4.4     | Test C  | hip Results                                                       | 58 |

| 4.5     | Chapt   | er Summary                                                        | 64 |

| Chapter | 5. Tł   | reshold Logic Addition                                            | 65 |

| 5.1     | Thresh  | nold Logic Addition Schemes                                       | 66 |

| 5.2     | Carry   | Lookahead Addition                                                | 67 |

| 5.3     | The A   | -DELTA Adder                                                      | 71 |

|         | 5.3.1   | Adder Architecture                                                | 71 |

|         | 5.3.2   | Design of the 16-bit Adders                                       | 72 |

|         | 5.3.3   | Layout and Simulation Results of A-DELTA                          | 74 |

| 5.4     | Prefix- | -8 Adder                                                          | 76 |

|         | 5.4.1   | Adder Architecture                                                | 76 |

|         | 5.4.2   | Delay Estimation and Comparison                                   | 79 |

| 5.5     | Chapt   | er Summary                                                        | 81 |

| Chapter | r 6. Tł | reshold Logic Multiplication                                      | 83 |

| 6.1    | Paralle | el Multipliers                                         | 84  |

|--------|---------|--------------------------------------------------------|-----|

|        | 6.1.1   | Parallel Counters                                      | 84  |

|        | 6.1.2   | Partial Product Reduction Tree (PPRT) Multipliers      | 85  |

| 6.2    | 3:2 an  | nd 2:2 Counters                                        | 86  |

|        | 6.2.1   | Standard CMOS Counters                                 | 86  |

|        | 6.2.2   | Domino Logic                                           | 87  |

|        | 6.2.3   | Threshold Logic—Kautz 3:2                              | 88  |

|        | 6.2.4   | A Hybrid TL/Domino 3:2 counter                         | 89  |

|        | 6.2.5   | Counter Comparison                                     | 90  |

| 6.3    | Large   | r Counters                                             | 91  |

|        | 6.3.1   | Implementation                                         | 91  |

|        | 6.3.2   | Kautz TL Counters                                      | 92  |

|        | 6.3.3   | Minnick TL Counters                                    | 93  |

|        | 6.3.4   | A Spectrum of TL Counters                              | 96  |

|        | 6.3.5   | Hybrid TL/Domino Counters                              | 101 |

|        | 6.3.6   | Counter Comparison                                     | 102 |

|        | 6.3.7   | Counter Choice                                         | 105 |

| 6.4    | TL Co   | ounter Circuits                                        | 106 |

| 6.5    | Partia  | l Product Reduction Trees                              | 112 |

|        | 6.5.1   | Three-Dimensional Method                               | 112 |

|        | 6.5.2   | Input-Symmetric Counters                               | 112 |

|        | 6.5.3   | Heterogeneous Circuits                                 | 113 |

|        | 6.5.4   | Results                                                | 114 |

| 6.6    | Chapt   | er Summary                                             | 115 |

| Chapte | r 7. Oı | ptical and GaAs Threshold Logic Techniques             | 117 |

| 7.1    |         | Based TL                                               |     |

| 7.2    |         | m Design Considerations                                |     |

|        | 7.2.1   | Physical structure of p-i(MQW)-n diode                 |     |

|        | 7.2.2   | Theoretical Model                                      |     |

|        | 7.2.3   | Nyquist Analog-to-Digital Converter using Optical TL   |     |

|        | 1.2.0   | 1.1 quiet mining to Digital Converter doing Optical II | 100 |

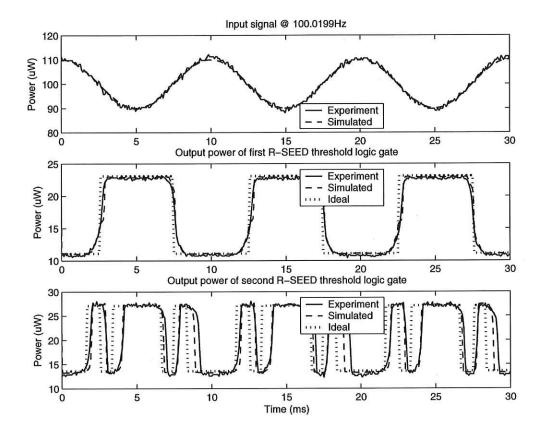

|          | 7.2.4   | Simulations and Experimental Results               | 122 |

|----------|---------|----------------------------------------------------|-----|

| 7.3      | CGaA    | s Threshold Logic                                  | 124 |

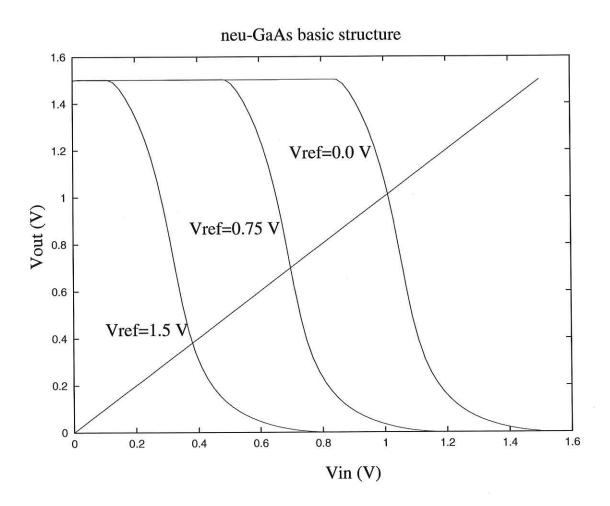

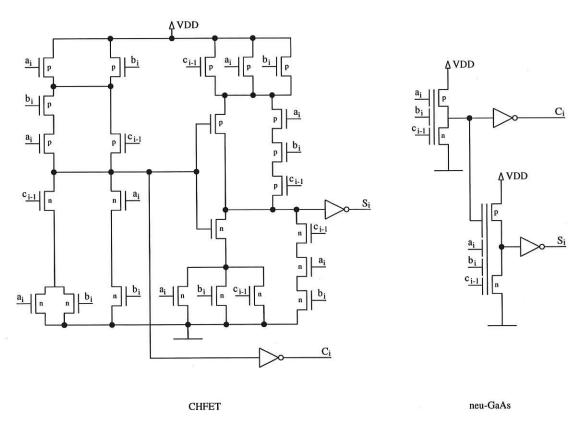

|          | 7.3.1   | Neu-GaAs Basic Structure                           | 126 |

|          | 7.3.2   | Choice of GaAs Technology                          | 126 |

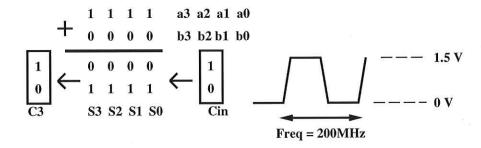

|          | 7.3.3   | A 4-bit neu-GaAs Ripple Carry Adder                | 127 |

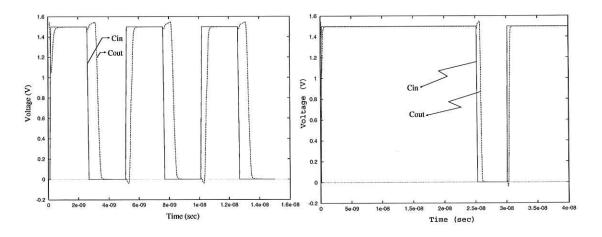

|          | 7.3.4   | Simulation results for the neu-GaAs RCA            | 131 |

|          | 7.3.5   | Gate Leakage                                       | 132 |

| 7.4      | Chapte  | er Summary                                         | 132 |

| Chapte   | r 8. Ma | apping TL Functions of a Small Number of Variables | 135 |

| 8.1      |         | inary Observations                                 | 136 |

| 8.2      |         | uting Boolean Functions Using Threshold Gates      |     |

| 8.3      |         | ple Design Technique                               |     |

| 8.4      |         | esign Examples                                     |     |

| 8.5      |         | ing the TL Network to neuron-MOS                   |     |

| 8.6      | Future  | Work                                               | 143 |

| 8.7      |         | er Summary                                         |     |

| Chaptei  | r 9. Su | mmary and Conclusions                              | 149 |

| 9.1      |         | Conclusions                                        | 150 |

|          | 9.1.1   | Review of Threshold Logic                          |     |

|          | 9.1.2   | Review of Threshold Logic Circuits                 |     |

|          | 9.1.3   | Capacitive Threshold Logic Circuits                |     |

|          | 9.1.4   | Threshold Logic Addition                           |     |

|          | 9.1.5   | Threshold Logic Multiplication                     | 151 |

|          | 9.1.6   | Optical and GaAs Threshold Logic                   |     |

|          | 9.1.7   | Mapping Threshold Logic Functions                  |     |

| 9.2      | Recom   | nmendations for Future Work                        | 152 |

| 9.3      | Summ    | ary of Original Contributions                      | 152 |

| 9.4      | Conclu  | usion                                              | 154 |

| Bibliogr | aphy    |                                                    | 155 |

| Biograp  | hy      |                                                    | 163 |

### **Abstract**

This Thesis focuses on the area of high speed very large scale integration (VLSI) complementary metal oxide semiconductor (CMOS) circuit design using threshold logic (TL) techniques. The work described in this document contributes three major advances on high speed TL based CMOS circuit design: (i) the development and experimental verification of novel high speed TL gate circuit topologies; (ii) a method for delay modelling of sense-amplifier based TL gates and (iii) novel TL based networks for the implementation of high speed arithmetic circuits. In this Thesis, the basics and previous work in threshold logic are reviewed, including theoretical results for TL based networks used in arithmetic and TL gate circuit design techniques. Novel floating gate based TL circuit implementations based on precharged sense-amplifiers employing charge recycyling are described and experimentally verified. A new weight-shared circuit technique is proposed which significantly reduces the area cost. Based on the theory of Logical Effort, a model for the Charge Recycling Threshold Logic (CRTL) gate is developed and experimentally verified. This model is used to evaluate and compare a number of CRTL based circuits, demonstrating its significant reduced delay compared to conventional static and dynamic CMOS logic. New parallel counters are proposed and partial product reduction trees based on these counters for use in parallel multipliers are shown to be significantly faster than previously published schemes. The 64-bit prefix-8 adder presented here is the fastest 64-bit adder published to date. The contributions in this Thesis are an important step towards alleviating the issues faced in present day VLSI arithmetic design and demonstrate for the first time the significant benefits offered by TL compared to conventional logic circuit techniques. The methodologies introduced are shown to lead to increased circuit compactness and reduced power dissipation which are of particular interest for future smart sensor technology and will potentially impact on future portable electronics systems for a range of applications from mobile personal communications through to aerospace systems.

# **Statement of Originality**

#### **Declaration**

| NAME: PETER CELINS                               | KI PROGRAM: PhD                                                                                                                                     |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| university or other tertiary institution and, to | accepted for the award of any other degree or diploma in any the best of my knowledge and belief, contains no material                              |

|                                                  | on, except where due reference has been made in the text.  eposited in the University Library, being made available for loan the Copyright Act 1968 |

| oma processpyrig, carajectic me processor or m   |                                                                                                                                                     |

| SIGNATURE:                                       | DATE: 27/09/2007                                                                                                                                    |

## Acknowledgments

This work was carried out with the support of many people to whom I am indebted. Firstly I want to thank my supervisor, Professor Derek Abbott (Director of the Centre for Biomedical Engineering, School of Electrical and Electronic Engineering; The University of Adelaide) for encouraging me to work on my own ideas from the beginning and providing the funding and support for numerous conferences and collaborative research trips.

Thanks go to my friends and colleagues from the University of Adelaide School of Electrical and Electronic Engineering: Sam Mickan, Leonard Hall, Greg Harmer, Andrew Allison, John Salerno, Greg Sherman, Said Al-Sarawi, Kiet To, Troy Townsend and Tony Sarros. In particular I would like to acknowledge the collaboration of Tony and Said on the SEED based TL work presented in Chapter 7 and Troy on the multiplier work presented in Chapter 6.

I would like to thank my many colleagues and friends abroad—Jose F. López at the University of Las Palmas in Spain, Dmitry Cheresiz, Sorin Cotofana and Stamatis Vassiliadis at the Delft University of Technology in the Netherlands, Sunay Shah at Oxford, Bart Rylander at the University of Portland, and Vojin Oklobdzija at the University of California, Davis.

A special thanks to Shaghik Atakaramians for assisting with the Latex presentation for this thesis.

I would like to gratefully acknowledge the financial support of the University of Adelaide Postgraduate Scholarship, Research Abroad Scholarship, Australian Research Council, Delft University of Technology Research Fellowship, IEEE SA Section Travel Scholarship, SPIE Student Travel Grant, Sir Ross and Sir Keith Smith Fund Scholarship, and the D. R. Stranks Travelling Fellowship.

Lastly, I would like to sincerely thank Theresa, my parents and Tom for their tremendous support, encouragement and generous patience.

This thesis survived a few parties, a startup, two rounds of VC funding and the birth of my beautiful son Aydan.

## **Conventions**

This thesis it typeset using the LATEX2e software. WinEdt build 5.4 was used as an effective interface to LATEX. Harvard style is used for referencing and citation in this thesis. Australian English spelling is adopted, as defined by the Macquarie English Dictionary.

## **Publications**

- [1] **Peter Celinski**, Derek Abbott, and Jose F. López, "Novel Extension of neu-MOS techniques to neu-GaAs," *Proc. of SPIE MICRO/MEMS 99*, vol 3893 Gold Coast, Australia, pp. 169-175, December 1999.

- [2] **Peter Celinski**, Said Al-Sarawi, and Derek Abbott, "A Delay Model for neuron-MOS and Capacitive Threshold Logic," *Proc. 7th IEEE International Conference on Electronics, Circuits & Systems*, Lebanon, pp. 932-935, December 2000.

- [3] **Peter Celinski**, Gregory D. Sherman, and Derek Abbott, "Implementation of Arbitrary Boolean Functions in Threshold Logic," *Proc. SPIE International Symposium on Smart Electronics and MEMS*, **vol. 4236**, Melbourne, Australia, December 2000.

- [4] **Peter Celinski**, Jose F. López, and Derek Abbott, "Novel Extension of neu-MOS techniques to neu-GaAs," *Microelectronics Journal* (Elsevier), vol 31, no 7, pp. 577-582, 2000.

- [5] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "Complementary neu-GaAs structure," IEE Electronics Letters, vol 36, no 5, pp. 424-425, March 2000.

- [6] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "A Low Power, High Speed Threshold Logic and its Application to the Design of Novel Carry Lookahead Adders," Proc. SPIE International Symposium on Smart Electronics and MEMS, pp. 258-265, Adelaide, Australia, December 2001.

- [7] Peter Celinski, Gregory D. Sherman, Jose F. López, and Derek Abbott, "A Mapping Technique For the Synthesis of Linear Threshold Networks to Implement Boolean Functions," Advances in Neural Networks and Applications, Nikos Mastorakis, editor, World Scientific Engineering Society, pp. 224-228 2001.

- [8] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "Low Power, High Speed Charge Recycling Threshold Logic Gate," *IEE Electronics Letters*, vol 37, no 17, pp. 1067-1069, August 2001.

- [9] Peter Celinski, Troy Townsend, Jose F. López, Said Al-Sarawi, and Derek Abbott, "A Compact Parallel Multiplication Scheme Based on (7,3) and (15,4) Self-Timed Threshold Logic Counters," Proc. 2nd WSEAS International Conference on Instrumentation, Measurement, Control, Circuits and Systems, pp. 2641-2645, Mexico, May 2002.

- [10] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "A Compact (m,n) Parallel Counter Circuit Based on Self Timed Threshold Logic," Proc. 2nd WSEAS International Conference on Instrumentation, Measurement, Control, Circuits and Systems, pp. 2601-2605, Mexico, May 2002.

- [11] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "A Family of Low Depth, Threshold Logic, Carry Lookahead Adders," Proc. 2nd WSEAS International Conference on Instrumentation, Measurement, Control, Circuits and Systems, pp. 1981-1983, Mexico, May 2002.

- [12] **Peter Celinski**, Sorin D. Cotofana, and Derek Abbott, "Generalized, Compact (m,n) Counters for High Speed Multipliers," *Proc. SPIE International Symposium on Smart Materials, Nano-, and Micro-Smart Systems*, pp. 205-213, Melbourne, Australia, December 2002.

- [13] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "Low Depth Carry Lookahead Addition Using Charge Recycling Threshold Logic," Proc. IEEE International Symposium on Circuits and Systems, pp. 469-472, Phoenix, USA, May 2002.

- [14] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "Compact Parallel (m,n) Counters Based on Self Timed Threshold Logic," *IEE Electronics Letters*, vol 38, no 13, pp. 633-635, June 2002.

- [15] Peter Celinski, Jose F. López, Said Al-Sarawi, and Derek Abbott, "Low depth, low power carry lookahead adders using threshold logic," *Microelectronics Journal* (Elsevier), vol. 33, No. 12, pp. 1071-1077, 2002.

- [16] **Peter Celinski**, Derek Abbott, and Said Al-Sarawi, "Level sensitive latch," US Patent number **6,542,016**, April 2003.

- [17] Peter Celinski, Sorin D. Cotofana, Jose F. López, Said Al-Sarawi, and Derek Abbott, "State-of-the-Art in CMOS Threshold Logic VLSI Gate Implementations and Applications," Proc. SPIE VLSI Circuits and Systems Conference, vol 5117, pp.53-63 Spain, May 2003 (invited).

- [18] **Peter Celinski**, Sorin D. Cotofana, and Derek Abbott, "A-DELTA: A 64-bit High Speed, Compact, Hybrid Dynamic-CMOS Threshold-Logic Adder," *Proc. 7th International Work Conference on Artificial and Natural Neural Networks*, (IWANN), pp. 73-80, Spain, 2003.

- [19] Peter Celinski, Sorin D. Cotofana, and Derek Abbott, "Area Efficient, High Speed Parallel Counter Circuits Using Charge Recycling Threshold Logic," Proc. IEEE International Symposium on Circuits and Systems, pp. 233-236 Bangkok, Thailand, May 2003.

- [20] Peter Celinski, Sorin D. Cotofana, and Derek Abbott, "A Logical Effort Based Delay Model of Charge Recycling Threshold Logic Gates," Proc. ProRISC Workshop on Circuits, Systems and Signal Processing, pp. 43-48, Veldhoven, Netherlands, November 2003 (keynote presentation).

- [21] Troy Townsend, Peter Celinski, Said Al-Sarawi, and Michael J. Liebelt, "Hybrid Parallel Counters Domino and Threshold Logic," Proc. IEEE Computer Society Annual Symposium on VLSI Emerging Trends in VLSI Systems Design (ISVLSI'04), pp. 275-276, Lafayette, Louisiana, February, 2004.

- [22] Peter Celinski, Said Al-Sarawi, Derek Abbott, Sorin D. Cotofana, and Stamatis Vassiliadis, "Logical Effort Based Design Exploration of 64-bit Adders Using a Mixed Dynamic-CMOS/Threshold-Logic Approach," Proc. IEEE Computer Society Annual Symposium on VLSI Emerging Trends in VLSI Systems Design (ISVLSI'04), pp. 127-132, Lafayette, Louisiana, February, 2004.

- [23] **Peter Celinski**, Sorin D. Cotofana, and Derek Abbott, "Delay Evaluation of High Speed Data-path Circuits Based on Threshold Logic," *Proc. of 14th International Workshop on Power and Timing Modeling, Optimization and Simulation* (PATMOS); Santorini, Greece, pp. 899-906, September 2004.

- [24] Said Al-Sarawi, Peter Celinski, and Tony Sarros, "Data Converters," Australian Patent Office, Application Number 2004906742, November 2004.

[25] Tony Sarros, Said Al-Sarawi, **Peter Celinski**, and Kerry A. Corbett, "Optical Threshold Logic Analog to Digital Converters Using Self Electro Optic Effect Devices," *Proc. of SPIE MSN & MSS*, **vol. 5649**, Sydney, Australia, pp. 227-236 December 2004.

# **List of Figures**

| 1.1  | Model of the Threshold Logic Gate                                                                                                          | 4     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2.1  | Model of the Threshold Logic gate                                                                                                          | 10    |

| 2.2  | Example networks that implement (a) 3-input AND, (b) 4-input MA-JORITY and (c) 2-input XOR                                                 | 12    |

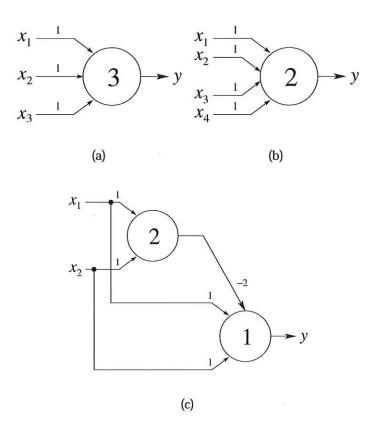

| 3.1  | Single-ended voltage mode threshold gates                                                                                                  | 24    |

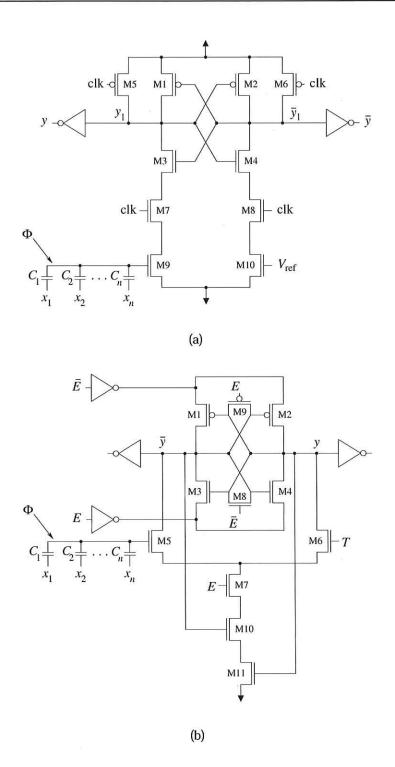

| 3.2  | Differential voltage mode threshold gates including (a) Latched $\nu$ MOS and (b) Charge Recycling Threshold Logic                         | 31    |

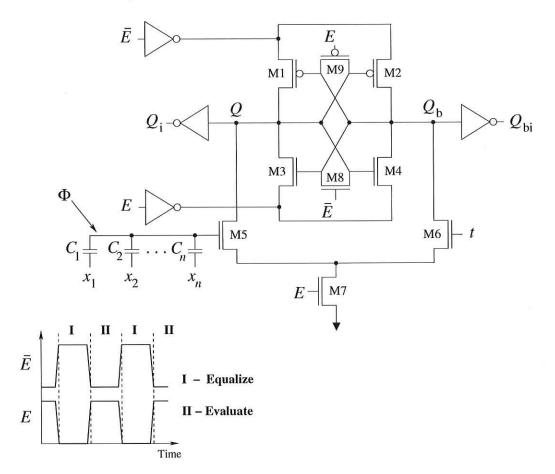

| 3.3  | Current mode threshold gates including (a) Latched Comparator Threshold Logic (LCTL) and (b) Equalized Current Mode Threshold Logic (ECMT) | L) 32 |

| 3.4  | Differential Current-Switch Threshold Logic                                                                                                | 33    |

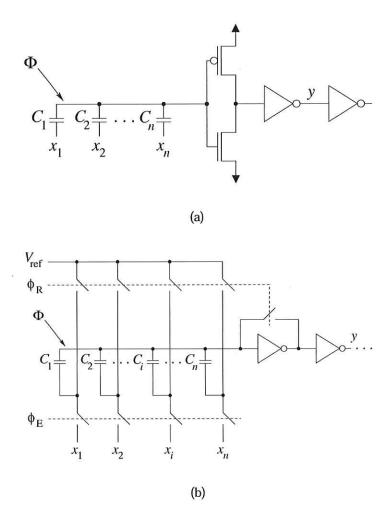

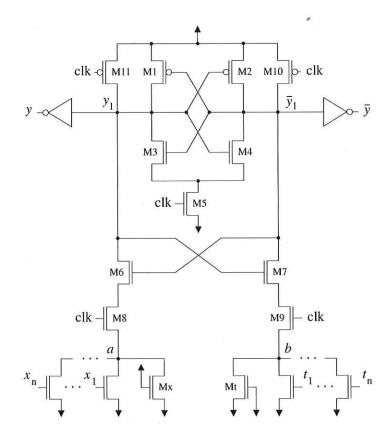

| 4.1  | Charge Recycling Threshold Logic (CRTL) Gate circuit                                                                                       | 43    |

| 4.2  | Layout of the CRTL circuit of Fig 4.1 in a 2P/4M 0.35 $\mu m$ process                                                                      | 44    |

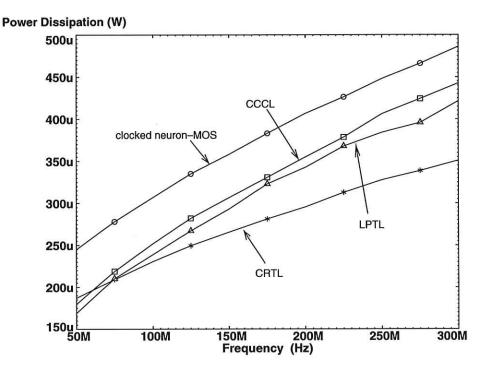

| 4.3  | Power Dissipation vs. Frequency comparison of the CRTL gate in a $0.35$                                                                    |       |

|      | $\mu$ m process                                                                                                                            | 45    |

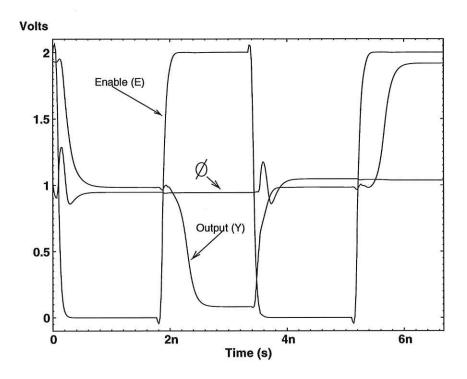

| 4.4  | Input, Enable and Output analog waveforms                                                                                                  | 46    |

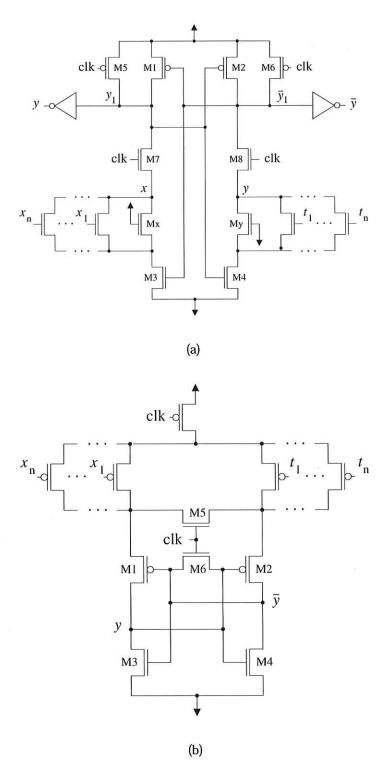

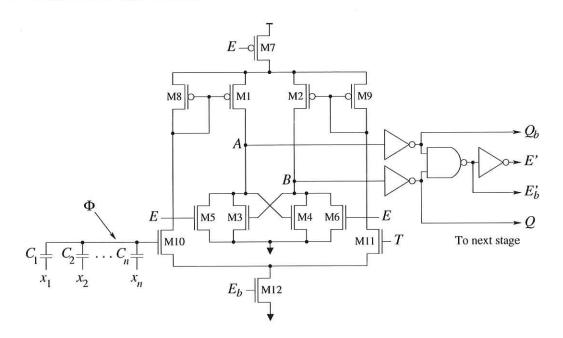

| 4.5  | The Self-Timed Threshold Logic gate structure circuit                                                                                      | 47    |

| 4.6  | Static CMOS 4-bit carry generate circuit                                                                                                   | 55    |

| 4.7  | Dynamic-CMOS 4-bit carry generate, domino circuit                                                                                          | 56    |

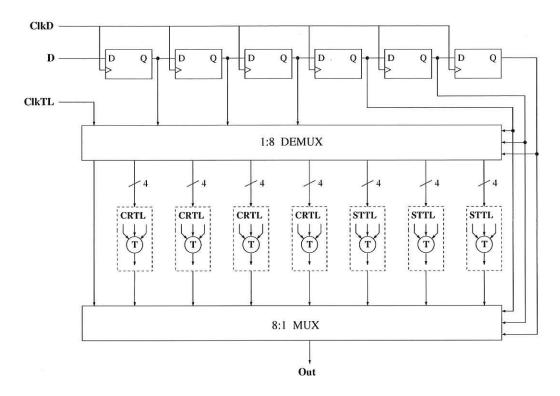

| 4.8  | Schematic of test chip for experimental functionality verification and delay measurements                                                  | 59    |

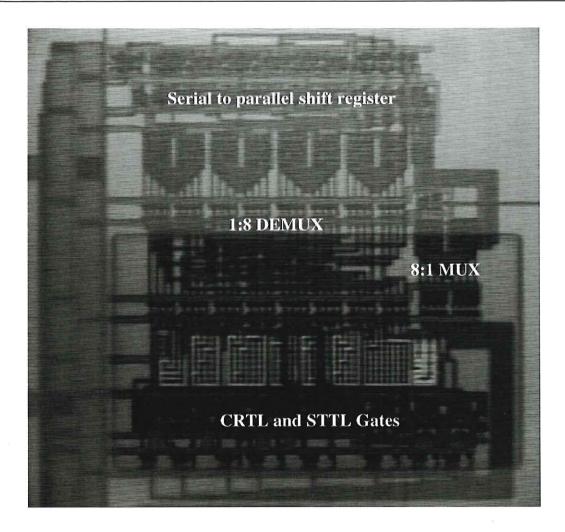

| 4.9  | Micrograph of fabricated test chip for experimental functionality and delay measurements in a 3.3 V, 0.35 $\mu m$ AMS CMOS process         | 60    |

| 4.10 | TL gates layouts and micrographs                                                                                                           | 62    |

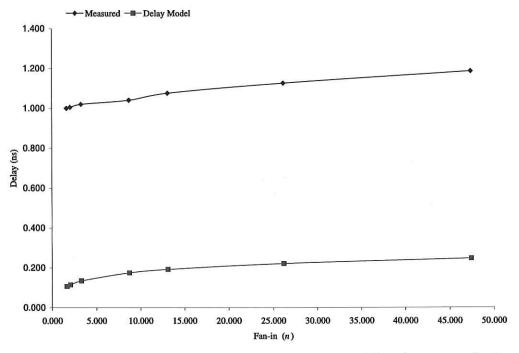

| 4.11 | Plot of measured and predicted CRTL gate delay, $d_{E 	o Qi}$ , vs. fan-in, $n$                                                            | 63    |

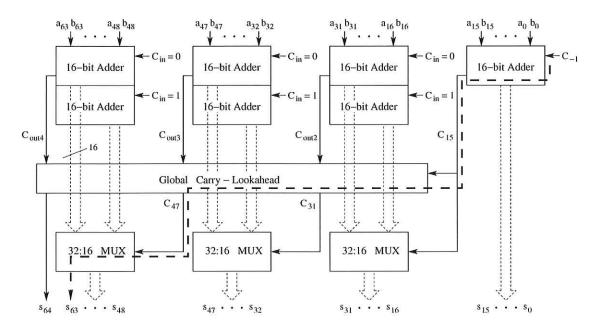

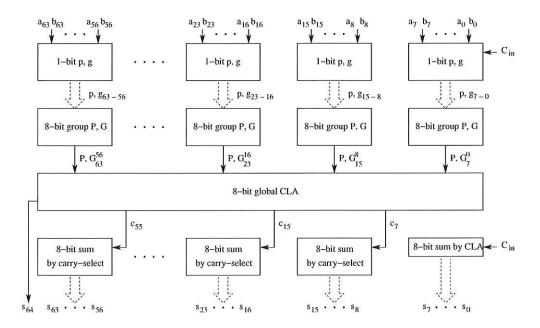

| 5.1  | Proposed 64-bit adder block diagram                                              |

|------|----------------------------------------------------------------------------------|

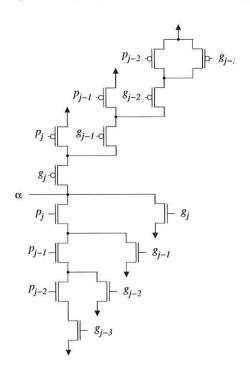

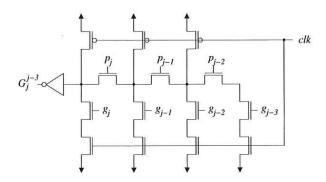

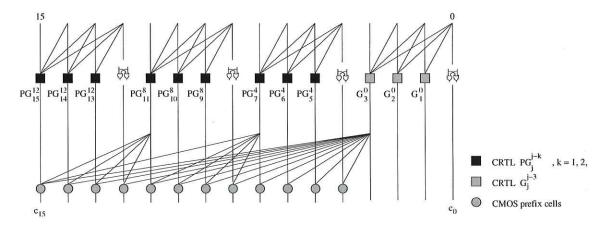

| 5.2  | 16-bit adder carry prefix-tree schematic                                         |

| 5.3  | Static-CMOS prefix cell                                                          |

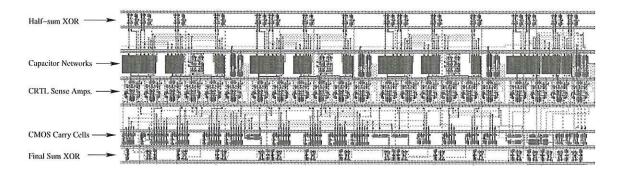

| 5.4  | Dynamic-CMOS circuits                                                            |

| 5.5  | 16-bit Adder Layout                                                              |

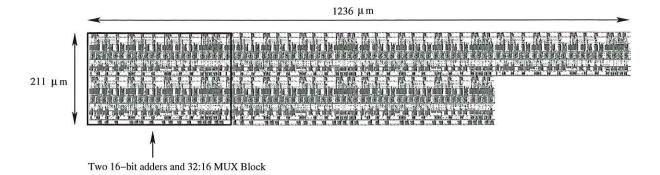

| 5.6  | 64-bit Adder Layout                                                              |

| 5.7  | 64-bit adder block diagram                                                       |

|      |                                                                                  |

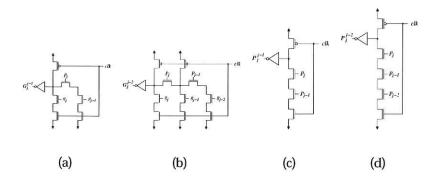

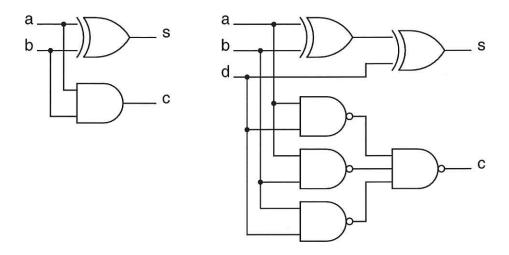

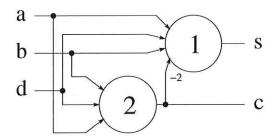

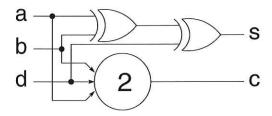

| 6.1  | Standard 2:2 and 3:2 CMOS counter circuits                                       |

| 6.2  | Kautz 3:2 counter circuit consisting of two threshold gates 89                   |

| 6.3  | Hybrid 3:2 counter circuit consisting of two XOR gates and one three-            |

|      | input threshold gate with unity weights and a threshold of $2  \dots  \dots  90$ |

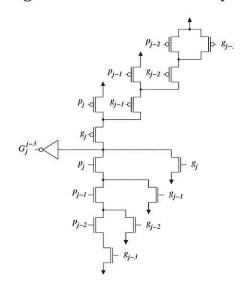

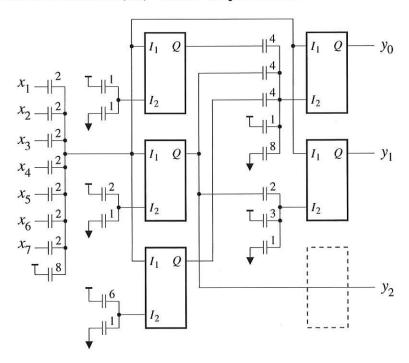

| 6.4  | Kautz 15:4 counter circuit                                                       |

| 6.5  | Minnick 15:4 counter circuit                                                     |

| 6.6  | The (7,3) counter truth table and the Minnick TL network 95                      |

| 6.7  | Minnick counter networks                                                         |

| 6.8  | Kautz counter networks                                                           |

| 6.9  | Hybrid counter networks                                                          |

| 6.10 | The $(1,2,X)$ hybrid 15:4 counter circuit consisting of XOR gates and a          |

|      | threshold logic network                                                          |

| 6.11 | Symmetric 6 to 3 reduction circuit using standard 3:2 counters 107               |

| 6.12 | Circuit diagram of the proposed STTL Modified Minnick (7,3) counter . 108        |

| 6.13 | Circuit diagram of the proposed CRTL Minnick scheme based (15,4)                 |

|      | counter                                                                          |

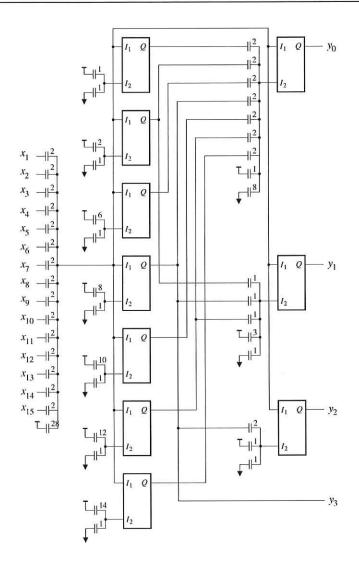

| 6.14 | Simulation results of the STTL Modified Minnick (7,3) counter 110                |

|      |                                                                                  |

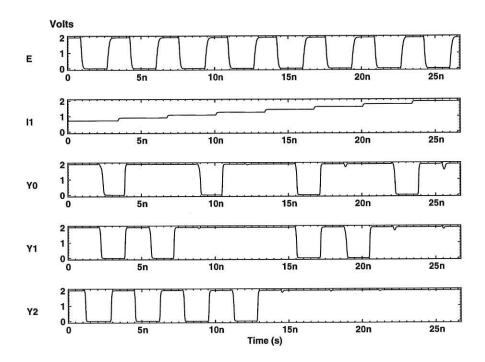

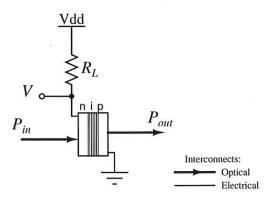

| 7.1  | SEED device                                                                      |

| 7.2  | Resistor-SEED (R-SEED) network in which a resistor is connected in se-           |

|      | ries with a SEED                                                                 |

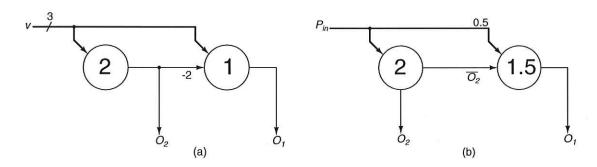

| 7.3  | Networks for performing the calculations in Equation 7.3                           |

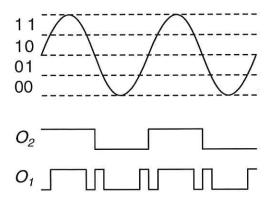

|------|------------------------------------------------------------------------------------|

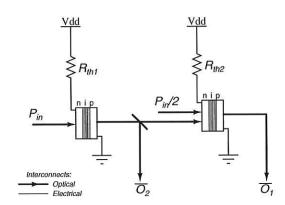

| 7.4  | Digital output of a 2-bit A/D converter from a sinusoidal waveform 122             |

| 7.5  | 2-bit optical threshold logic ADC                                                  |

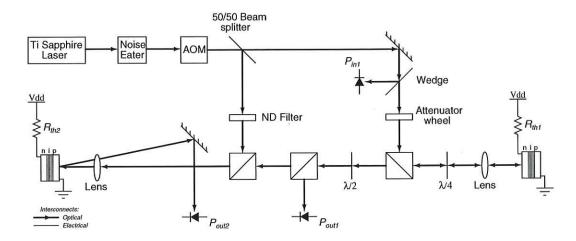

| 7.6  | Experimental setup for a 2-bit optical threshold logic ADC 123                     |

| 7.7  | Threshold R-SEED results                                                           |

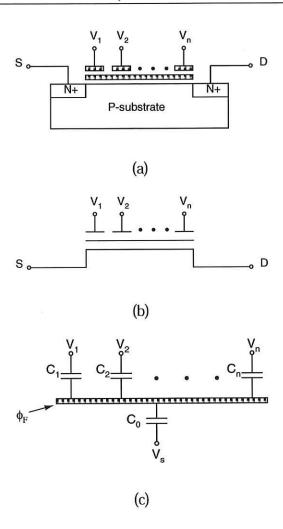

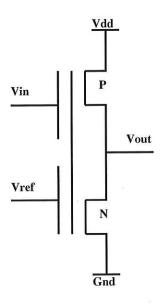

| 7.8  | Introducing neu-MOS                                                                |

| 7.9  | Basic neu-GaAs inverter structure                                                  |

| 7.10 | Neu-GaAs inverter structure simulation results                                     |

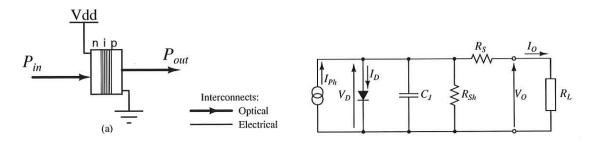

| 7.11 | Conventional GaAs and neu-GaAs full adder designs                                  |

| 7.12 | Switching of $c_3$ during the HSPICE simulation                                    |

| 7.13 | $C_{\text{out}}$ and $C_{\text{in}}$ Simulation for a neu-GaAs full adder          |

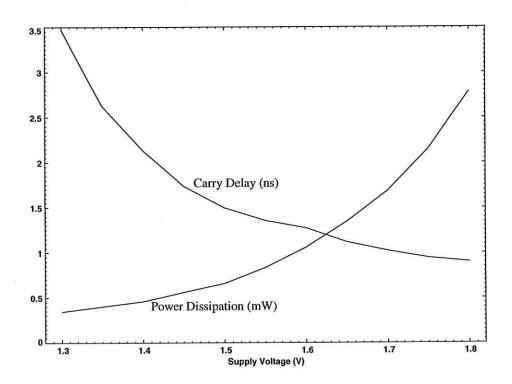

| 7.14 | Delay and power dissipation vs. supply voltage for a 4-bit neu-GaAs RCA133         |

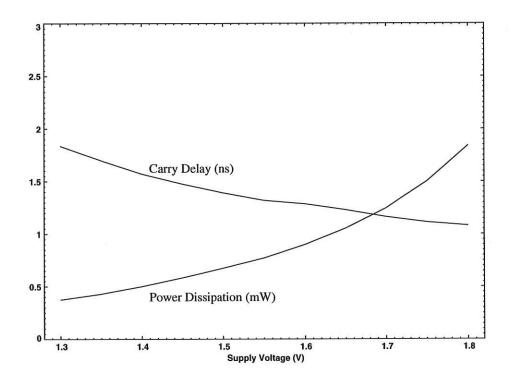

| 7.15 | Delay and Power Dissipation vs Supply Voltage for a 4-bit conventional             |

|      | GaAs RCA                                                                           |

|      |                                                                                    |

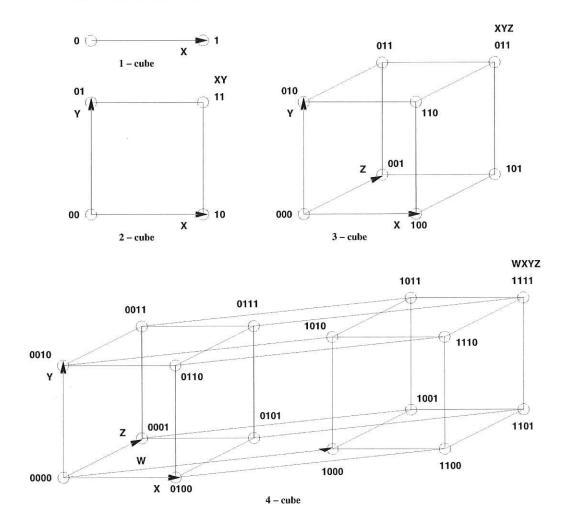

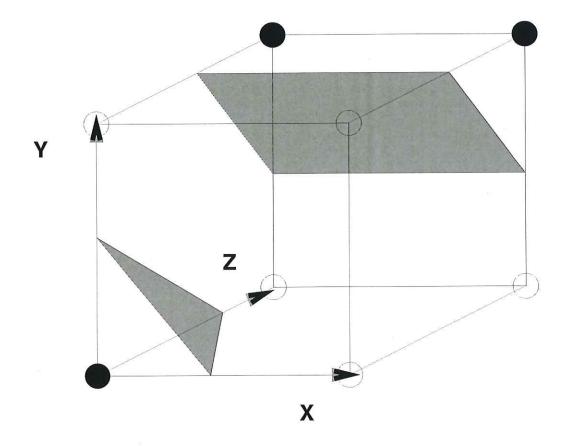

| 8.1  | N-Dimensional cubes shown for 1, 2, 3 and 4 dimensions                             |

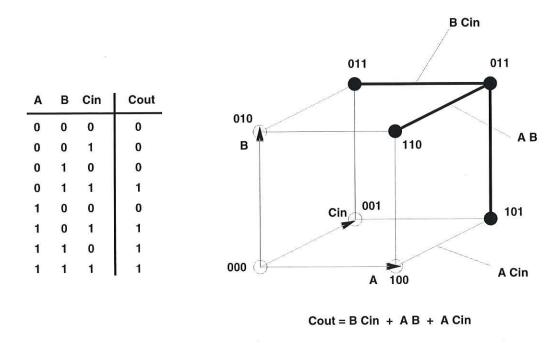

| 8.2  | Full adder carry-out function shown on a 3-cube and the three adjacency            |

|      | planes (edges) corresponding to the three product terms                            |

| 8.3  | An example of a function requiring two threshold gates in the first (in-           |

|      | put) layer                                                                         |

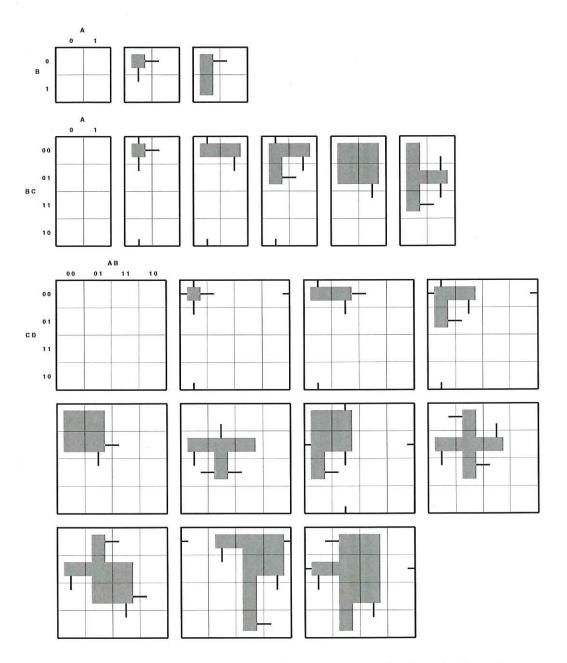

| 8.4  | All of the Karnaugh map shapes (up to isomorphism) and selected or-                |

|      | thogonal edges for possible cut-complexes in 2, 3 and 4-dimensions $145$           |

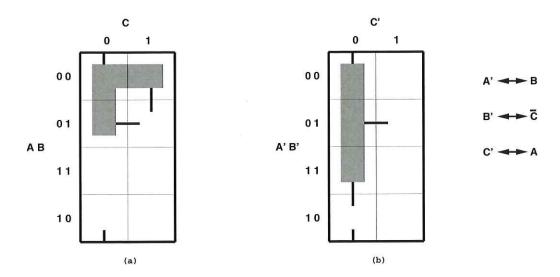

| 8.5  | (a) Original Shape on Karnaugh map. (b) A shape isomorphic to the                  |

|      | shape shown in (a)                                                                 |

| 8.6  | (a) Karnaugh map and minimum threshold cover for $Y=ar{A}+Bar{C}$ (weight          |

|      | of shape = 6) (b) Corresponding minimally weighted cut-complex (with               |

|      | re-assigned inputs) and selected orthogonal edges (weight of shape = 5) 146        |

| 8.7  | The AON and threshold logic implementations of $Y = \bar{A} + B\bar{C}$ 146        |

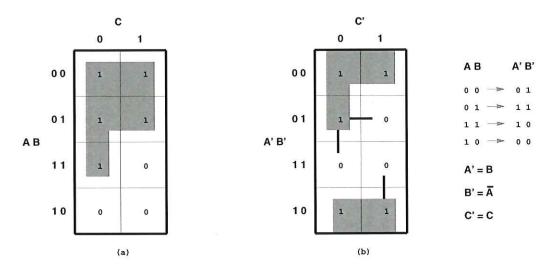

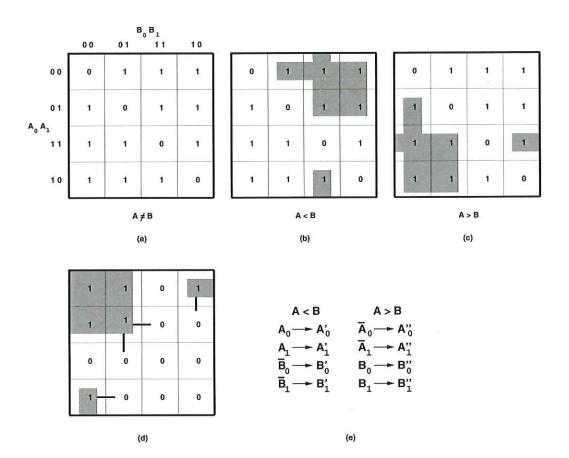

| 8.8  | (a) Karnaugh map for $Y \equiv (A_1 A_0 \neq B_1 B_0)$ , (b) The minimum threshold |

|      | cover for $A < B$ , (c) The minimum threshold cover for $A > B$ , (d) The          |

|      | minimally weighted cut-complex and selected orthogonal edges, (e)                  |

|      | The required input re-assignment for both (b) and (c) to obtain (d) 147            |

#### List of Figures

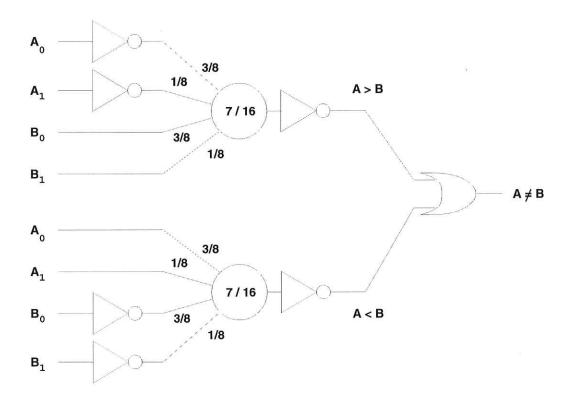

| 8.9  | The threshold logic implementation of $Y \equiv (A_1 A_0 \neq B_1 B_0) \ldots \ldots$ | 148 |

|------|---------------------------------------------------------------------------------------|-----|

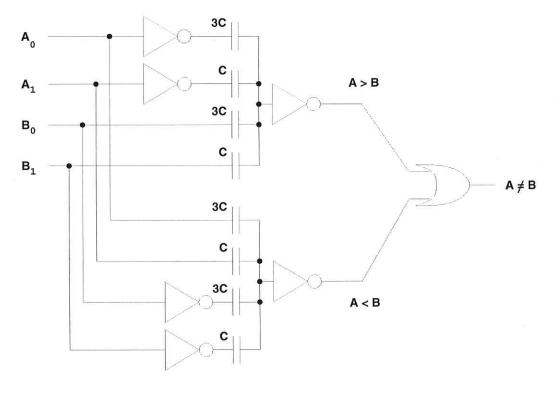

| 8.10 | The neuron-MOS implementation of $Y \equiv (A_1 A_0 \neq B_1 B_0) \ldots \ldots$      | 148 |

|      | ·                                                                                     |     |

| 9.1  | Model of the Threshold Logic Gate                                                     | 150 |

## **List of Tables**

| 2.1 | Summary of theoretical constructive results on threshold logic addition                     |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | including network depth, gate count, maximum weight and maximum                             |    |

|     | fan-in                                                                                      | 17 |

| 2.2 | Block Save Addition (BSA) hardware requirements for the partial prod-                       |    |

|     | uct reduction to two partial sum-words in depth-2                                           | 19 |

| 2.3 | Partial Product Reduction using Hierarchical Block Save Addition (HBSA)                     |    |

|     | and Telescopic Sums with Gate Sharing (TSGS)                                                | 19 |

| 3.1 | Summary of Reported TL Gate Delay Results                                                   | 34 |

| 3.2 | Summary of Reported TL Gate Power Dissipation Results                                       | 35 |

| 3.3 | Summary of Reported TL Gate Applications                                                    | 36 |

| 3.4 | Summary of Reported TL Gate Applications (continued)                                        | 39 |

| 4.1 | Delay parameters of the 0.35 $\mu$ m, 3.3 V, 4M/2P process at 75°C                          | 53 |

| 4.2 | Extracted CRTL gate logical effort, $g$ , parasitic delay, $p$ , parameters $\dots$         | 53 |

| 4.3 | Minimum-delay domino-CMOS AND tree designs                                                  | 57 |

| 4.4 | Static CMOS AND tree designs                                                                | 57 |

| 4.5 | 4-bit carry generate, $G_j^{j-3}$ , and (7,3) counter $c_{\text{out}}$ FO4 delay comparison |    |

|     | with CRTL for path electrical effort $H = 1$ and $10 \dots \dots \dots \dots$               | 58 |

| 4.6 | CRTL and STTL gates implemented on the test chip, the weight values,                        |    |

|     | threshold range and occupied chip area                                                      | 63 |

| 4.7 | Residual floating gate voltage ( $\phi_{ m res}$ ), measured threshold (all data inputs     |    |

|     | $x_i$ set to 0), calculated $n_{ m eff}$ and measured $n_{ m eff}$                          | 63 |

| 5.1 | Summary of 64-bit TL adder results including network depth, gate count,                     |    |

|     | maximum weight and maximum fan-in                                                           | 66 |

| 5.2 | MODCVS and CRTL 4-bit adder comparison                                                      | 70 |

| 5.3 | Normalized Logical Effort (LE) parameters of various gates                                  | 79 |

| 5.4 | Comparison of high speed 64-bit adders showing that the pproposed                           |    |

|     | Prefix-8 adder has significantly lower delay compared to previously pub-                    |    |

|     | lished results                                                                              | 80 |

|     |                                                                                             |    |

#### List of Tables

| 6.1 | Static CMOS 3:2 counter—logical effort analysis                         | 87  |

|-----|-------------------------------------------------------------------------|-----|

| 6.2 | Domino 3:2 counter—logical effort analysis                              | 88  |

| 6.3 | A comparison of 3:2 counters (for homogeneous circuits)                 | 91  |

| 6.4 | A comparison of 3:2 counters (for heterogeneous circuits)               | 92  |

| 6.5 | Comparison of saturated counters                                        | 103 |

| 6.6 | Comparison of the various designs for saturated (3,2), (7,3) and (15,4) |     |

|     | counters                                                                | 104 |

| 6.7 | Counter comparison (0.35 $\mu m$ 2P/4M process) for Boolean logic (BL), |     |

|     | Charge-Recycling Threshold Logic (CRTL and Shared-capacitor CRTL        |     |

|     | (SCRTL) implementations                                                 | 111 |

| 6.8 | The PPRT latency comparison (in terms of delay parameter $\phi$ )       | 114 |

| 6.9 | Partial product reduction tree area estimates                           | 115 |

|     |                                                                         |     |

| 7.1 | Composite HSPICE parameters                                             | 129 |

| 7.2 | Simulation Results for a 4-bit RCA                                      | 132 |

## Chapter 1

"It is clear to me that we will develop silicon neural systems, and that learning how to design them is one of the greatest intellectual quests of all time."

— Carver Mead

HIS chapter introduces Threshold Logic and outlines the motivation for the work in this Thesis. The structure of the Thesis and the contents of the Chapters are outlined, and the original contributions are summarized.

#### 1.1 Context and Technology

Arithmetic operations, including addition and multiplication, are critical operations performed by microprocessors and digital signal processors. Consequently, the design of high speed and low power adder and multiplier circuits are key requirements in building a high performance computer. The computer designer's task is to find a good solution in the vast design space which spans from the process technology, circuits, architecture, software up to the algorithm level. In addition to computation speed, increasingly important is the design for low power dissipation and low cost.

Complementary metal-oxide silicon (CMOS) has now been the dominant underlying technology for building processors and related components for almost three decades (Pucknell and Eshraghian 1988, Weste and Eshraghian 1995). Rapid improvements in the speed and density of CMOS transistors has seen the clock frequency of microprocessors double every two years and they are expected to reach around 12 GHz by 2010 (SIA 2001). The clock frequency of a clocked microprocessor chip is the most important design parameter in the quest for higher performance. The minimum clock cycle time is often set by the adder delay in a processor. Adders are also used in floating-point arithmetic units, arithmetic logic units, memory addressing and program counter updates. Multipliers are important in many computational problems and complete multiplication units have been integrated in state-of-the-art digital signal processors and microprocessors.

Gordon Moore observed in 1965 that the number of transistors per unit of chip area had doubled every year since the integrated circuit was invented and he predicted that this trend would continue (Moore 1965). This rate has slowed down in processors, however memory density has continued to approximately double every 18 months and provides the current definition of Moore's Law. As the technology nears physical scaling limits, alternative fabrication technologies and techniques will need to be used in order for this trend to continue.

As process technology feature sizes continue to shrink, high speed digital VLSI circuit designers are increasingly faced with the challenging issues of, among others, power dissipation, signal integrity and design complexity. Threshold Logic based circuits are a potential candidate for alleviating these design issues.

Chapter 1

#### 1.2 Threshold Logic

The realization that human brains are far superior to computers in solving many problems including combinatorial optimization and image and speech processing, despite the building blocks being several orders of magnitude slower, has led to significant interest in the field of artificial neural networks. This Thesis considers the Boolean model of an artificial neuron, namely the linear Threshold Logic (TL) gate, that computes a neural-like Boolean function of binary inputs. The main issues in the study of networks (circuits) of TL gates include the estimation of their computational capabilities and limitations and the comparioson of their properties with those of traditional Boolean logic circuits based on AND, OR and NOT (AON) gates. There is strong evidence that TL circuits are more efficient than AON circuits in implementing a number of important functions including integer addition, multiplication and division (Beiu *et al.* 2003).

Threshold Logic has been studied since the 1960's (Minnick 1961, Winder 1963, Sheng 1965, Dertouzos 1965, Hu 1965, Lewis and Coates 1967, Sheng 1969). It is a possible alternative or complementary design technique to traditional Boolean logic due to the greater computational capability of TL gates. There has been a resurgence in TL research in recent years in the VLSI design community. Whereas the theoretical development of TL is mature, satisfactory CMOS implementations of TL gates and circuits based on these gates have only recently been developed.

Significant questions remain, concerning factors such as performance improvement and silicon area reduction, which have not been solved by such theoretical studies. For decades, TL gates have offered the promise of higher functional (computational) density over traditional logic using AON gates, leading to reduced gate count and therefore smaller logic networks and faster circuits, however, few practical designs have been demonstrated.

The computational power of the threshold logic network design style lies in the intrinsically more complex functions implemented by such gates when compared to conventional Boolean logic gates. This potentially allows circuit realizations, which require fewer threshold gates than standard logic gates (Muroga 1971). It is well known that an arbitrary Boolean function can be realized by a network of threshold gates and there are many examples where the number of gates required is considerably less than when conventional logic is used. In contrast, there are also functions where there are no savings.

More recently, a number of theoretical results have shown that TL networks with the number of levels polynomially bounded can implement functions that require networks with unbounded levels of standard logic gates (Impagliazzo *et al.* 1997). In particular, important functions like multiple-addition, multiplication, division and sorting can be implemented by polynomial-size threshold circuits of small constant depth.

Threshold gates operate on the so-called majority or threshold decision principle, where the gate's output value depends on whether the weighted arithmetic sum of its input values exceeds a threshold. Conventional simple logic gates, such as AND and OR gates, are special cases of threshold gates, and Boolean logic may be considered a sub-set of threshold logic. However, the usefulness of threshold logic as a design alternative is determined by the availability of efficient threshold gate implementations, where efficiency is measured in terms of delay, power dissipation and silicon area, or a combination of these.

With regard to silicon implementations, of particular importance is that threshold gates are more sensitive than conventional gates to transistor mismatch and noise. The sensitivities depend on the particular circuit implementation, and there is frequently a trade-off between increased logic capability and robustness.

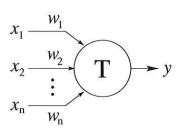

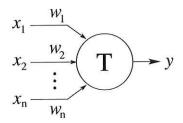

A threshold logic gate is functionally similar to a hard limiting neuron without learning capability. The gate has n binary inputs  $x_1, x_2, \ldots, x_n$ , a set of corresponding n real number weights  $w_1, w_2, \ldots, w_n$  and a single binary output y, as shown in Fig. 1.1.

Figure 1.1. Model of the Threshold Logic Gate. The gate shows the outputs y after a thresholding operation T that sums inputs  $x_1$  to  $x_n$  after multiplication by weights  $w_n$ .

The output y is given by (all operators algebraic):

$$y = \begin{cases} 1, & \text{if } \sum_{i=1}^{n} w_i x_i \ge T \\ 0, & \text{otherwise.} \end{cases}$$

(1.1)

A device that implements this theoretical model must compute the linear weighted sum of the binary inputs, store the threshold value and compare the weighted sum Chapter 1 Introduction

to this threshold. The various gate implementations proposed differ in the way they implement the weights, threshold and comparison. They rely on representing each distinct weighted sum of inputs and the threshold level by an analogue voltage or current and will be explored in Chapter 2.

A TL gate can be programmed, either statically (hard wired at design time) or dynamically, to realize many distinct Boolean functions by adjusting the threshold T and/or the weights  $w_i$ . For example, an n-input TL gate with unit weights,  $w_i = 1$  and threshold T = n will realize an n-input AND gate. The output of this gate is logic 1 if and only if all inputs are 1. By setting T = n/2 and leaving the weights unchanged, the gate computes a majority function. This versatility means that TL offers a significantly increased computational capability over conventional AND-OR-NOT logic.

Significantly reduced area and increased circuit speed can therefore *potentially* be obtained, especially in applications requiring a large number of input variables, such as computer arithmetic. For example, to implement the 8-input MAJORITY function (5-or-more-out-of-8) using conventional 2-input AND and OR gates requires a network of 47 gates of depth 6. The same function is readily implemented using a single 8-input threshold gate with unit weights and threshold equal to 5 (T=5).

A small number of practical circuit examples have emerged since the mid 1990's, illustrating the potential of TL to reduce circuit area, interconnect (wiring) and to lower power dissipation when compared to conventional logic. The most advanced circuits presented to date consist of simple arithmetic components (Celinski *et al.* 2003c), including full-adders, compressors, parallel population counters, single high fan-in majority/OR/AND gates, Muller-C elements, 4-bit adders and embedded TL flip-flops.

Despite the resurgence of research interest in threshold logic, there remain a number of unresolved issues in the approaches proposed to date. This Thesis aims to address these issues:

- The TL gate designs proposed previously have had a high power dissipation relative to conventional CMOS logic.

- The TL gate designs proposed previously have a high delay relative to conventional CMOS logic.

- The TL gate designs occupy a large area relative to conventional CMOS logic.

- No large scale TL based circuit designs (complete arithmetic blocks) have been demonstrated that offer advantages over conventional CMOS logic.

- The silicon area savings and performance improvement, which result from the use of threshold gates for realizing a large scale logic design, have not previously been determined.

- The extent to which the theoretical advantages of TL (i.e. the exponential to polynomial reduction in gate count for common functions, such as PARITY), offset by practical implementation issues, including limited precision of weights.

The main aim of this Thesis is to demonstrate, using novel TL gate implementations and based on a large scale design, the advantages of the threshold logic circuit design paradigm over conventional CMOS logic in terms of improved power dissipation, speed performance and area efficiency.

#### 1.3 Thesis Overview and Organization

Chapter 1 introduces threshold logic. Chapter 2 reviews the literature on threshold logic gate circuit implementations, and theoretical results related to the implementation of important arithmetic functions using threshold gate networks.

Novel contributions to threshold logic circuit design are presented in Chapter 4, including two new threshold gate designs, their performance evaluation and test chip measurement results. The application of these gates to the design of adder circuits is described in Chapter 5. In Chapter 6, the focus is on parallel counters and their application to the design of multiplier circuits. Chapter 7 shows how threshold logic techniques may be applied to technologies other than CMOS, including Gallium Arsenide and Self-Electro-Optical (SEED) devices. Chapter 8 includes a discussion of a mapping technique developed to aid in the implementation of logic functions using threshold gates.

Chapter 8 concludes the Thesis with a summary of the outcomes and conclusions, and recommendations for future work in threshold logic.

Chapter 1

#### 1.4 Original Contributions

For many years, research in linear threshold logic has focussed on two areas, namely computational circuit complexity and hardware implementation, with surprisingly little overlap between the two. This Thesis aims to establish a connection between the theory and implementation of threshold logic circuits. Establishing this connection will lead to solutions for practical problems and inspire new theoretical questions raised as a result of implementation issues.

The original contributions in this Thesis in the area of threshold logic technology lie in (i) threshold gate circuit techniques and (ii) threshold logic network design for important arithmetic operations, including addition and multiplication. The originality of these contributions is evidenced by the list of patents, journal and conference publications on Pages xix to xxii.

The work in this Thesis proposes two original CMOS threshold gate circuit topologies, Charge Recycling Threshold Logic (CRTL) and Self-Timed Threshold Logic (STTL). These gates exhibit superior delay performance and lower power dissipation compared to any previously proposed threshold gate. The development of CRTL and STTL was carried out in collaboration with Dr. José F. López at the Research Institute for Applied Microelectronics at the University of Las Palmas de G.C., Spain, and test chips were designed in cooperation with the Microelectronic Circuits and Analogue Devices Research Group in the Department of Engineering Science at the University of Oxford. The CRTL and STTL gates were experimentally verified, and a new weight-sharing circuit technique was proposed, which greatly reduces the circuit area cost of CRTL and STTL based circuits and may be applied to other TL gate designs.

The work presented here has also led to the development of a new, patented level sensitive latch for use in the design of high-speed, compact flip-flop circuits with low internal power dissipation and clock load as well as new, patented analog-to-digital converters based on optical Self-Electro-Optic Devices (SEEDs).

Following the development of CRTL and STTL, a delay modelling technique is proposed, based on the principles of Logical Effort (Sutherland and Sproull 1991), for the systematic evaluation and design for minimal delay of CRTL based circuits. The method developed is applicable to other sense-amplifier based TL gates.

To demonstrate the advantages of the threshold logic design paradigm on a non-trivial circuit problem, two new hybrid CRTL/CMOS-domino adder designs are developed.

The prefix-8 adder design is shown to be over 1 FO4 delay faster than any other 64-bit CMOS adder design proposed to date that does not require multiple non-overlapping clock phases. The adders were developed in collaboration with Assoc. Prof. Sorin Cotofana from the Computer Engineering Group at the Delft University of Technology in the Netherlands.

New parallel counters networks and multiplier circuits are developed, and the proposed partial product reduction schemes are shown to be significantly faster than previously published implementations.

The adder and multiplier circuits shown in this Thesis are the first published largescale designs based on threshold logic which demonstrate conclusively the advantage of threshold logic over conventional CMOS in arithmetic application.

The original contributions of this Thesis offer benefits to high performance and low power VLSI processor design and to potential applications of threshold logic in compact low power, portable, wireless devices. Portability is important for aerospace applications, smart sensors and personal communication systems.

## Chapter 2

# Threshold Logic Arithmetic

HE focus of this chapter is the review of significant, recent developments in threshold logic arithmetic. The theoretical results in threshold logic addition and multiplication are reviewed and summarized, providing a context for the original contributions in these areas developed later in the Thesis.

#### 2.1 Neural Computation

It is believed that the computational power of neural systems is related to their adaptive behaviour, and for this reason the majority of research in the field of neuromorphic analog VLSI is related to implementing neurons that learn or adapt (Holler *et al.* 1989, Hasler *et al.* 1995). It has also been demonstrated that the elementary function performed by neurons, namely the sum of weighted inputs followed by thresholding, is in itself, without learning, highly useful. The capability of such building blocks has been extensively studied and the computational complexity theory of circuits is well established. However, there has been little work reported in the literature on the link between theoretical results in threshold logic and work on improved silicon implementations particularly relating to the polynomial network size using TL versus the exponential circuit size using conventional AON logic required to compute useful Boolean functions.

Threshold networks have been shown to be particularly efficient in implementing various important arithmetic functions. For example, integer multiplication can be implemented by a polynomial size threshold circuit of constant depth. This means that to implement the threshold circuit to compute the multiplication of two *n*-bit integers, polynomially many (in *n*) threshold gates are required. In contrast, using conventional AON logic gates requires exponentially many gates.

#### 2.2 Threshold Logic vs. Conventional Logic

The model of the threshold gate introduced in Chapter 1, is repeated for convenience in Fig. 2.1.

Figure 2.1. Model of the Threshold Logic gate. The gate shows the outputs y after a thresholding operation T that sums inputs  $x_1$  to  $x_n$  after multiplication by weights  $w_n$ .

The Boolean function computed by such a gate is called a threshold function and it is specified by the gate threshold T and the weights  $w_1, w_2, \ldots, w_n$ , where  $w_i$  is the weight

associated with the  $i^{th}$  input variable  $x_i$ . It has been shown (Muroga 1971) that any linear threshold function can be implemented with integer weights. The threshold function implemented by the model shown in Fig. 9.1 can be written in a more compact form using the sgn notation:

$$y = \operatorname{sgn}\left\{\sum_{i=1}^{n} w_i x_i - T\right\},\tag{2.1}$$

where the sgn function is defined as follows, sgn(x) = 1 if  $x \ge 0$  and sgn(x) = 0 if x < 0.

A threshold logic *network* will be considered an acyclic graph, in which each connection is associated with a weight and in which each node calculates the step activation function defined by Equation 2.1. A threshold logic *circuit* will be considered to be the transistor level CMOS implementation of a network, which consists of one or more threshold gates.

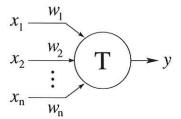

As an example, using the notation of Equation 2.1, the 3-input AND, 4-input MAJOR-ITY and 2-input XOR functions may be written as in Equations 2.2-2.4 and Figs. 2.2(a)-(c) show the networks that implement the corresponding functions,

$$AND(x_1, x_2, x_3) = sgn(x_1 + x_2 + x_3 - 3)$$

(2.2)

$$MAJ(x_1, x_2, x_3, x_4) = sgn(x_1 + x_2 + x_3 + x_4 - 2)$$

(2.3)

$$XOR(x_1, x_2) = sgn\{x_1 + x_2 - 2 \cdot sgn(x_1 + x_2 - 2) - 1\}.$$

(2.4)

A device that implements the theoretical model in Fig. 9.1 must compute the linear weighted sum of the binary inputs, store the threshold value and compare the weighted sum to this threshold. The gates discussed in later sections follow this paradigm, but they differ in the way they implement the weights, threshold and comparison.

A fair question to ask is whether there is a justifiable reason for using threshold gates, given that any Boolean function can be systematically implemented by AND, OR and NOT (AON) gates. The reason is that for many important functions, including XOR, the number of AON gates grows exponentially with the number of inputs to the function (Wegener 1991). On the other hand, using threshold gates the number of gates is linear in the number of input bits. In general, a depth-2, AON circuit implementation of the n-bit XOR function requires at least  $2^{n-1} + 1$  gates, and only n + 1 TL gates. The

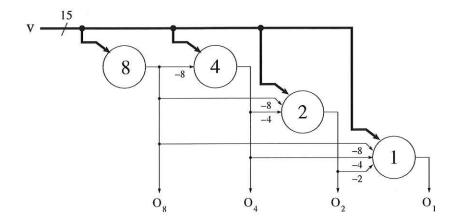

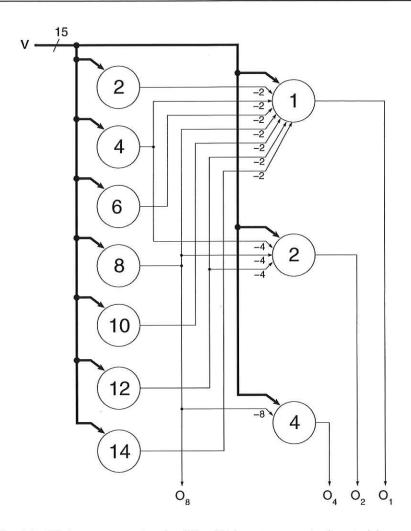

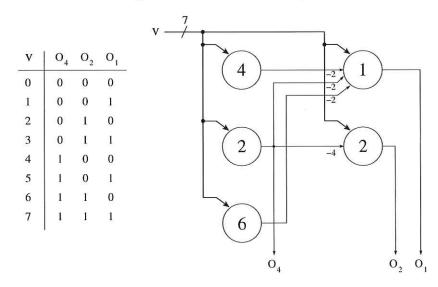

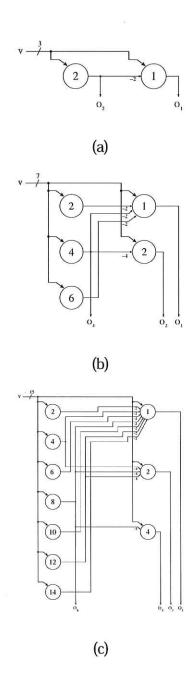

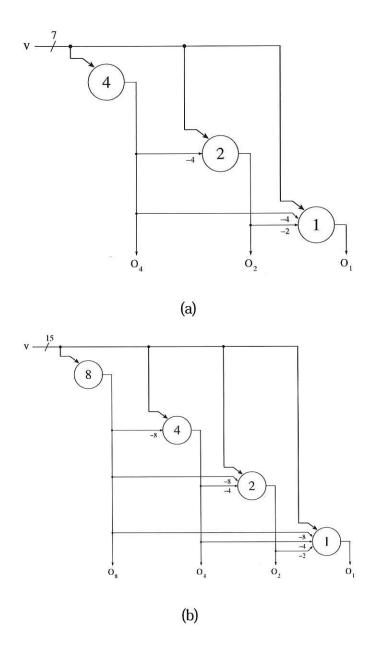

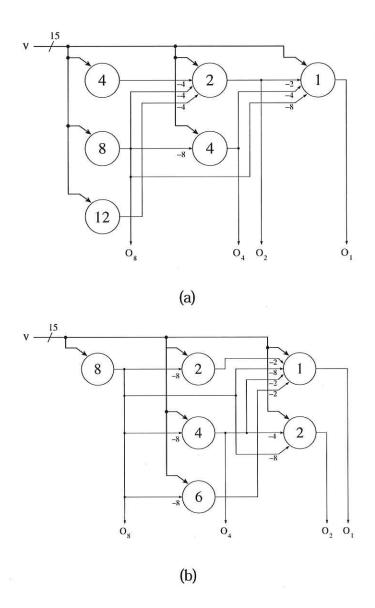

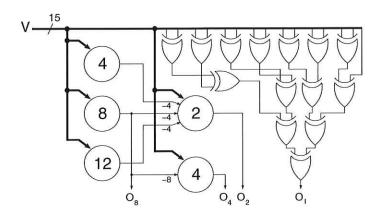

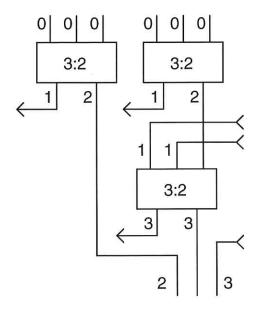

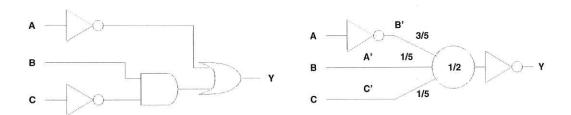

Figure 2.2. Example networks that implement (a) 3-input AND, (b) 4-input MAJORITY and (c) 2-input XOR. The binary logic inputs are denoted by  $x_i$  and the binary output of each gate is denoted by y. The weights and their values for each input are denoted by the number beside each gate input and the gate thresholds are given by the number inside the circles. The XOR gate is an example of a two-level threshold logic network.

power of TL based circuits is evident when we observe that for any single AON gate there is an equivalent TL gate, but the reverse does not hold.

Even though TL circuits are computationally more powerful, the gate implementations, as will be discussed in the following sections, are more complex and therefore may potentially require more area and dissipate more power. The central question to ask is to what extent are the theoretical advantages of TL, i.e. the exponential to polynomial reduction in gate count, offset by the practical implementation issues. The answer to this question depends on the complexity of the function to be implemented —typically the greater the number of inputs to the gate the greater the advantage of employing TL.

From a practical perspective, it is insufficient to contend with polynomial bounds on weights and gate number, as the absolute numbers may still be prohibitively large for leading to an efficient or even feasible implementation from a reliability perspective. Hardware implementations use a finite number of bits for weight storage (whether programmable or hard-wired) and this translates to a limited precision for the weights. The precision of the implementation is directly related to its cost, usually in circuit area and therefore increased capacitance leading to increased power dissipation. Increasing the precision requires that the TL gate be able to reliably distinguish a smaller quantity, either voltage or current, typically in a noisy circuit environment.

If the weighted sum is in the form of a voltage on a capacitor, a higher precision leads to a larger area of that capacitor (as capacitor mismatch is inversely related to area) and a greater amount of energy required to charge the capacitor. More importantly, the ability of a sense-amplifier , which implements the thresholding operation, to resolve the small voltage difference is dominated by the input-referred offset voltage. This in turn is related to transistor mismatch in the sensing circuit, which is inversely related to transistor area, leading to larger transistor requirements.

It is instructive to determine whether there is an inherent advantage of TL gates that can reliably handle a large number of inputs. We assume that the size of an n-input TL gate is approximately proportional to n. Under this assumption, it can easily be shown that a TL gate implementing an n-input AND gate can be replaced by a tree of 2-input AND gates of which the size is also approximately proportional to n, since the size of the tree is proportional to the number of 2-input AND gates, which is approximately n.

However, this scenario changes when we consider a general *n*-input threshold function and construct a network of two-input TL gates to implement the same function. It turns out that the size of this tree is *at least* proportional to  $n^2$  (Mead 1989), an order of magnitude larger than the single gate. This can be understood by comparing the information content carried by the signal nodes within the 2-input network and the analog nature of the summation node of the single TL gate. Within the 2-input network, the intermediate discrete gate outputs carry less information than the intermediate analog nodes and hence a larger network is required to compensate for this lost information by providing a larger number of discrete signal nodes. In addition to allowing a smaller circuit size for implementing a given threshold function, high fan-in TL gates lead to networks with reduced depth and hence lower delay.

## 2.3 Threshold Logic Addition and Multiplication

In the last decade, significant progress has been made in the theory of arithmetic circuit design based on threshold logic. In this section, recent constructive results (i.e. where the reported method prescribes how to select the weight values and how to construct the network) for the addition and multiplication of two binary integers are summarized. The main issues to consider relate to the network depth (delay), maximum required weight values and gate fan-in. Despite the resurgence of activity in this area during the last decade, there have been very few implementations. The earliest examples are the *Mark I Perceptron* built by Rosenblatt (1958), Widrow's *Memistor* (1960) and the DONUT computer (Coates and Lewis 1964). Recent threshold logic based circuit implementations may be found in the floating point co-processor of MIPS R2010 (Johnson 1988), the SUN Sparc V9 (Lev *et al.* 1995) and the Itanium 2 microprocessor in 2002 (Naffziger *et al.* 2002).

#### 2.3.1 Addition Networks

The addition of two n-bit binary numbers,  $X = x_{n-1}, x_{n-2} \dots x_0$  and  $Y = y_{n-1}, y_{n-2} \dots y_0$ , is defined as the unsigned sum,  $S = s_n, s_{n-1}, s_{n-2} \dots s_0$ , of X added to Y. There are many well known techniques for performing addition (Ling 1981, Brent and Kung 1982, Knowles 1999, Beaumont-Smith and Lim 2001). The sum bits  $s_i$  may be computed using  $s_i = x_i \oplus y_i \oplus c_{i-1}$  for  $i = 0, 1, \dots, n-1$ , and  $s_n = c_n$ . The carry bits are  $c_i = (x_i \cdot y_i) + (x_i \cdot c_{i-1}) + (y_i \cdot c_{i-1}), c_{-1} = 0$ . Alternatively, the sum bits,  $s_i$  may be written as  $s_i = (x_i \cdot y_i \cdot c_{i-1}) + [\bar{c}_i \cdot (x_i + y_i + c_{i-1})]$  and this expression may be implemented using a single TL gate. The addition operation essentially reduces to computing the carries,  $c_i$ , from which the sum bits are computed in the final stage of the process.

To date there have been two approaches in the study of TL based adders, theoretical and practical. The theoretical approach is concerned with the computational circuit complexity, and this may be divided into two categories. The first is the set of results that establish existence of solutions and upper and lower bounds on the various parameters such as network depth and size. The second set includes results that are constructive and provide a method of determining the weights and interconnection of TL gates, and is of particular interest to finding efficient circuit implementations.

Theoretical research has also focused on the weights, or more precisely on the capabilities of TL networks with restricted weights. Particular classes of functions are amenable to physically realizable implementations using gates with low fan-in, small weights and in shallow depth and polynomially sized networks. This class includes addition and multiplication.

The existence of a depth-2 adder of polynomial size is well known (Siu and Bruck 1990). It was followed by the first constructive depth-2 majority gate based adder (i.e. using TL gates with weights of -1, 0 or +1) of size  $O(n^4)$ , first published in 1991 and commonly available in (Alon and Bruck 1994). Table 2.1 provides a more detailed summary of these results relating to network depth, TL gate count, maximum weight size and maximum gate fan-in, adapted from (Beiu 2003).

The chronilogically ordered list below summarizes the notable result on the depth, weight dynamic range and network size for the addition operation.

- 1991 depth-3 of size  $n^2/2 + 7n/2 1$  (Siu et al. 1991)

- 1991 depth-7 of size  $O(n\log n)$  (Siu et al. 1991)

- 1993 to 1994 depth-5 of size O(nlogn) (Beiu et al. 1993, Beiu et al. 1994b, Beiu et al. 1994a)

- 1994 depth-4 to  $3 + \log n$  of size 7n to  $2n\log n + 5n$  (Beiu 1994, Beiu et al. 1994a)

- 1994 depth-3 of size 5*n* with exponential weights (Beiu 1994, Beiu *et al.* 1994a)

- 1995 to 1996 depth-3 of size  $6n + 2\lceil n/\lceil n\rceil\rceil$  with exponential weights (Cannas 1995, Vassiliadis *et al.* 1996)

- 1996 depth 3 of size  $O(n^2/k \log n)$  for any  $1 \le k \le n/\log n$  with polynomial weights (Vassiliadis *et al.* 1996)

- 1999 depth-2 of size  $n^2 + 2n$  with exponential weights (Beiu 1999)

- 1999 depth-3 of size  $n\sqrt{n} + 4n$  and weights  $2^{1\sqrt[4]{n}}$  (Beiu 1999)

- 1999 depth-2 of size 2n with exponential weights  $2^n$  (Ramos and Bohórquez 1999)

- 1999 depth-3 of size 4n with weights  $2^{\sqrt{n}}$  (Ramos and Bohórquez 1999).

The above results show the tradeoffs in terms of adder depth vs. size and the related weight size. The progressive improvements in small depth adders have reduced the

size of depth-2 networks from  $O(n^4)$  with constant weights to O(n) with exponential weights. In depth-3 and and depth-4, the size has been reduced to O(n) with exponential weights. These results will be used in Chapter 4 to develop an efficient TL 64-bit CMOS adder implementation.

Although network size and weight magnitude may not grow exponentially with the adder width, the best schemes for shallow depth addition still require polynomially increasing weights. This may lead to *absolute* values for network size (TL gate count), weights and fan-in to be prohibitively large for a feasible CMOS implementation, frequently by an order of magnitude. Network depth alone is also insufficient to evaluate the likely delay or to compare delay of implementations, largely because in a circuit implementation the true delay depends on technological constraints such as wire loading and fan-out.

Table 2.1. Summary of theoretical constructive results on threshold logic addition including network depth, gate count, maximum weight and maximum fan-in. The symbol n denotes the operand width, c denotes a constant,  $w_{\max}$  denotes the value of the maximum weight in the network,  $\delta$  denotes an arbitrary parameter constraint and  $\lceil \rceil$  denotes the ceiling operator (lowest integer greater than). Adapted from Beiu et al. [2003].

| Year         | Depth                                            | # Gates                                                               | W <sub>max</sub>                 | Fan-in <sub>max</sub>                                 |  |

|--------------|--------------------------------------------------|-----------------------------------------------------------------------|----------------------------------|-------------------------------------------------------|--|

| Siu & Bruck  | 2                                                | $n^c$                                                                 |                                  | -                                                     |  |

| 1990         |                                                  |                                                                       |                                  |                                                       |  |

| Alon & Bruck | 2                                                | $O(n^4)$                                                              | {-1,0,+1}                        | $n^4$                                                 |  |

| 1991         |                                                  |                                                                       |                                  |                                                       |  |

| Siu et al.   | 3                                                | $(n^2+7n-2)/2$                                                        | {-1,0,+1}                        | 2n                                                    |  |

| 1991         | 7                                                | $O(n\log n)$                                                          | {-1,0,+1}                        |                                                       |  |

| Beiu et al.  | 5                                                | $O(n \log n)$                                                         | 2 <sup>n</sup>                   | 2 <i>n</i>                                            |  |

| 1994         |                                                  |                                                                       |                                  |                                                       |  |

| Beiu         | $3+\lceil \frac{\log n}{\log \delta - 1} \rceil$ | $5n + 2n \lceil \frac{\log n}{\log \delta - 1} \rceil$                | $2^{\delta/2}$                   | δ                                                     |  |

| 1994         | 4                                                | 7 <i>n</i>                                                            | $2^n$                            | 2n                                                    |  |

|              | d                                                | 2dn - n                                                               | $2^{\frac{d-\sqrt[3]{n}}{2}}$    | $2 \sqrt[d-3]{n}$                                     |  |

|              | $3 + \frac{\log n}{\log(\log w_{\max})}$         | $5n + \frac{2n\log n}{\log(\log w_{\max})}$                           | W <sub>max</sub>                 | 2log w <sub>max</sub>                                 |  |

| Beiu         | $2+\lceil \frac{\log n}{\log \delta - 1} \rceil$ | $3n + 2n \lceil \frac{\log n}{\log \delta - 1} \rceil$                | $2^{\delta/2}$                   | δ                                                     |  |

| 1994         | 3 5 <i>n</i>                                     |                                                                       | 2 <sup>n</sup>                   | 2 <i>n</i>                                            |  |

|              | 4                                                | 7 <i>n</i>                                                            | $2^{\sqrt{n}}$                   | $2\sqrt{n}$                                           |  |

|              | d                                                | 2dn - n                                                               | $2^{\frac{d-2\sqrt{n}}{2}}$      | $2\sqrt[d-2]{n}$                                      |  |

|              | $2 + \frac{\log n}{\log(\log w_{\max})}$         | $3n + \frac{2n\log n}{\log(\log w_{\max})}$                           | $w_{ m max}$                     | $2\log w_{\max}$                                      |  |

| Vassiliadis  | 3                                                | $6n+2\lceil n/\lceil \sqrt{n}\rceil\rceil$                            | 2 「√п                            | $2\lceil \frac{n}{\lceil \sqrt{n} \rceil} \rceil + 3$ |  |

| et al. 1996  |                                                  |                                                                       |                                  | 1 41                                                  |  |

| Beiu         | $1+\lceil \frac{\log n}{\log \delta -1} \rceil$  | $\frac{n\delta}{2} + 2n \lceil \frac{\log n}{\log \delta - 1} \rceil$ | $2^{0.7\delta}$                  | δ                                                     |  |

| 1999         | d                                                | $n\sqrt[d-1]{n} + 2n(d-1)$                                            | $2^{1.4} \sqrt[d-1]{n}$          | $2\sqrt[d-1]{n}$                                      |  |

|              | $1 + \frac{\log n}{\log(\log w_{\max}^{0.7})}$   | $\frac{2n\log n}{\log(\log w_{\max}^{0.7})} + O(n)$                   | $w_{ m max}$                     | 1.4logw <sub>max</sub>                                |  |

| Ramos &      | d                                                | $2(d-1)n-2(d-3)\sqrt[d-1]{n^{d-2}}$                                   | $2^{\frac{d-1}{\sqrt{n^{d-2}}}}$ | $2\sqrt[d-1]{n^{d-2}}+1$                              |  |

| Bohórquez    | $1 + \frac{\log n}{\log(\log w_{\max})}$         | $\frac{2n\log n}{\log(\log w_{\max})} + O(n)$                         | w <sub>max</sub>                 | $2\log w_{\max} + 1$                                  |  |

| 1999         |                                                  |                                                                       |                                  |                                                       |  |

#### 2.3.2 Multiplication Networks

Multiplication is closely related to addition. The product of two n-bit numbers requires the computation of the sum of n 2n-bit numbers that form the rows of the partial products matrix. Siu and Bruck (1990) showed, based on considerations of multi operand addition, that the product of two n-bit numbers can be computed in depth-4 using a polynomially sized (in n) network with polynomially bounded weights.

The multiplication operation consists of three steps. In the first stage of the multiplier, the partial product bits are generated, typically using AND gates. In the second stage, the matrix of partial products is reduced to two numbers which are simply added in the third stage.

The second stage is by far the most expensive in terms of the number of gates and fan-in per gate. Although it is theoretically possible to implement the second stage using a depth-2 network, the excessive hardware requirements render conventional approaches prohibitive. Lauwereins and Bruck (1991) observed that a depth-2 implementation using Block Save Addition (BSA) (Siu and Bruck 1990) of the second stage of a  $32\times32$ -bit multiplier requires gates with fan-in  $\geq 1000$ , and over 20 million connections. In BSA, the partial product columns of n numbers are divided into column-blocks of  $\log n$  bits. The sum of one column-block is therefore at most  $2\log n$  bits wide and hence overlaps only the column-block to which it belongs and at most one adjacent column-block. As a result, the even and odd column-block sums do not overlap and the sums of the even and odd column-blocks are concatenated to two partial sumwords. Siu and Bruck (1990) proved that the sum of a column-block of n numbers  $\log n$  bits wide can be determined in a depth-2 polynomially bounded network. Table 2.2 (Lauwereins and Bruck 1991) lists the number of gates and fan-in requirements for common multiplier widths using the BSA scheme.

In order to reduce the hardware requirements, Lauwereins and Bruck (1991) described two minimizations, while maintaining the depth-2 strategy for the second stage. While this resulted in significant wiring and gate savings, practical implementation based on this method for word lengths beyond 16 bits is still not feasible. To reach a practical hardware solution, Lawereins explored trading off cost for an increase in delay, based on a Hierarchical Block Save Addition (HBSA) approach. Instead of performing the entire reduction of the partial product bits in a single step using a depth-2 network, the *n* partial product rows are broken down into blocks of numbers, and each block is reduced to two numbers in one reduction step, and the process is repeated until

Table 2.2. Block Save Addition (BSA) hardware requirements for the partial product reduction to two partial sum-words in depth-2. The table shows that the number of TL gates and the maximum gate fan-in are very high for a 32×32 multiplier.

| Multiplier Width | # TL Gates | Max Fan-In |  |

|------------------|------------|------------|--|

| 4×4              | 272        | 16         |  |

| 8×8              | 1,950      | 64         |  |

| $16 \times 16$   | 16,448     | 256        |  |

| 32×32            | 133,250    | 1024       |  |

Table 2.3. Partial Product Reduction using Hierarchical Block Save Addition (HBSA) and Telescopic Sums with Gate Sharing (TSGS). The table shows a significant reduction in the number of gates required compared to the BSA approach.

| Multiplier Width | # TL Gates - HBSA | # TL Gates - TSGS | Max Fan-In |

|------------------|-------------------|-------------------|------------|

| 4×4              | 88                | 40                | 16         |

| 8×8              | 310               | 144               | 64         |

| 16×16            | 1264              | 464               | 256        |

| 32×32            | 4966              | 1820              | 1024       |

two numbers remain. Based on a block size of 8, the  $32\times32$ -bit multiplication second stage now requires approximately 5300 gates with maximum fan-in of 24 (Lauwereins and Bruck 1991). Further optimizations, based on the observation that certain bits in the partial product reduction steps are constantly zero, reduce the gate number by approximately a factor of two. It was also observed that compared to carry save addition (CSA) using various reduction schemes, the delay of the HBSA is significantly lower for the same fan-in requirement.