# INVESTIGATION INTO METHODS AND ANALYSIS OF COMPUTER AIDED DESIGN OF VLSI CIRCUITS

J. A. NOONAN B. E.(Hons.)

A thesis submitted for the Degree of Master of Engineering Science

$\mathbf{in}$

The Department of Electrical and Electronic Engineering, The University of Adelaide.

### TABLE OF CONTENTS

| Table of Contents  | i) |

|--------------------|----|

| Synopsis           | r) |

| Declaration        | V) |

| Acknowledgements(v | i) |

## CHAPTER I

## IC TECHNOLOGIES AND DESIGN

| 1.1 Introduction to IC's and a VLSI Technology Choice | 1.1   |

|-------------------------------------------------------|-------|

| 1.2 The VLSI Design Philosophy                        | . 1.8 |

| 1.3 Australian MPC's 1                                | 1.13  |

| 1.4 Summary1                                          | 1,17  |

### CHAPTER II

## LOW LEVEL CAD TOOLS FOR VLSI CIRCUIT DESIGN AND ANALYSIS

| 2.1 Mask Level Design of IC's using MPC's                  | 2.1  |

|------------------------------------------------------------|------|

| 2.2 Embedded Layout Languages                              | 2.3  |

| 2.3 Interactive Mask Level Geometry Editors                | 2.4  |

| 2.3.1 Hierarchical Design Philosophies of Geometry Editors | 2.10 |

| 2.3.2 Further Analysis of Geometry Editors                 | 2.12 |

| 2.4 Design Rule Checkers                                   | 2.16 |

| 2.4.1 Hierarchical Design Rule Checking                    | 2.17 |

| 2.4.2 Technology Independent Design Rule Checking          | 2.19 |

| 2.4.3 Design Rule Checking Input and Output                | 2.22 |

| 2.4.4 DRC Conclusions                                      | 2.23 |

| 2.5 Circuit Extractors                                     |      |

| 2.6 Electrical Rule Checkers                               | 2.27 |

| 2.7 Simulators                                             | 2.28 |

| 2.7.1 Circuit Simulators                                   | 2.28 |

| 2.7.2 Timing and Logic Simulators                          | 2.30 |

| 2.8 MAGIC                                                  | 2.32 |

| 2.9 Conclusions                                            | 2.33 |

|                                                            |      |

## CHAPTER III

## HIGHER LEVEL CAD TOOLS

| 3.1 Introduction to Symbolic Level Design on a Virtual Grid, VIVID |  |

|--------------------------------------------------------------------|--|

| 3.1.1 A Better Circuit Description Language (ABCD)                 |  |

| 3.1.2 Higher Level Graphic Circuit Editing (ICE)                   |  |

| 3.1.3 Circuit Extraction and Simulation                            |  |

| 3.1.4 Compaction to a Standard Mask Description                    |  |

| 3.1.5 Mask Level Layout Description                                |  |

| 3.1.6 Master Technology File System | 3.17 |

|-------------------------------------|------|

| 3.1.7 VIVID Summary                 | 3.18 |

| 3.2 Design Levels                   |      |

| 3.3 Programmable Logic Arrays PLA's | 3.23 |

| 3.4 Display Tools                   | 3.29 |

| 3.5 A System Level Simulator        | 3.31 |

| 3.6 Conclusions                     | 3.32 |

### CHAPTER IV

# nMOS DESIGN USING MASK LEVEL CAD TOOLS AND TWO MPC PROCESSES

| 4.1 Introduction                               | 4.1  |

|------------------------------------------------|------|

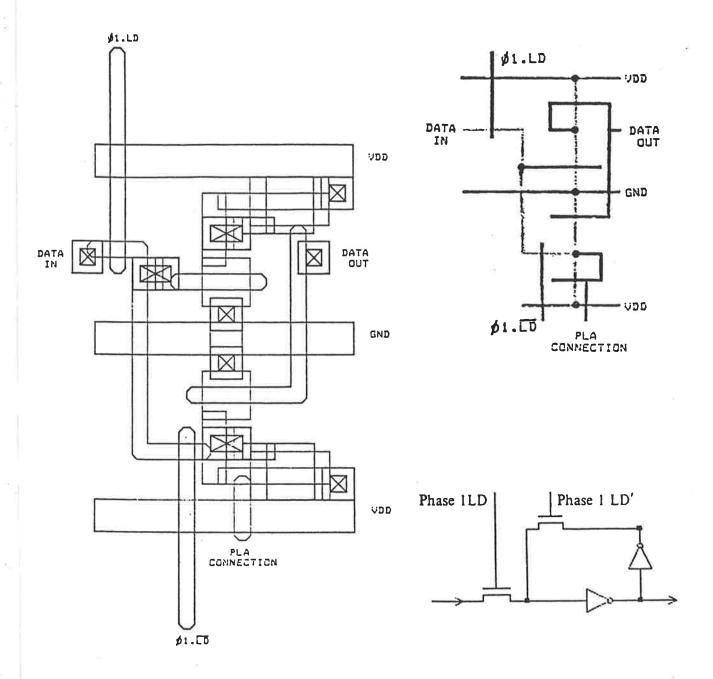

| 4.2 The Signature Analyser                     | 4.2  |

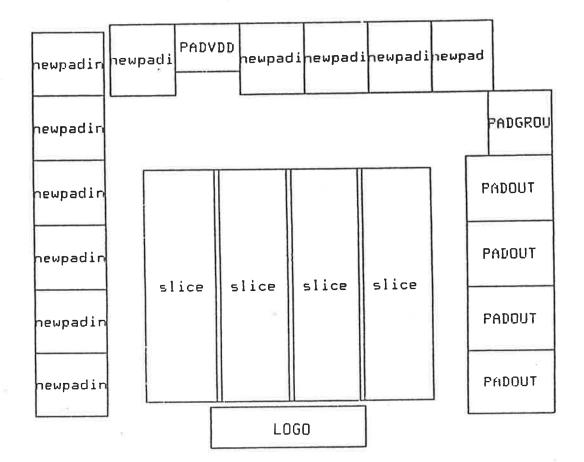

| 4.2.1 Problem Definition and Floorplanning     | 4.4  |

| 4.2.2 Stick Diagrams in Mixed Notation         | 4.6  |

| 4.3 Design, Layout and Checking                | 4.8  |

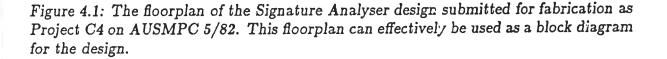

| 4.3.1 Leaf Cell Layout                         | 4.9  |

| 4.3.2 Pad Allocation and Positioning           | 4.12 |

| 4.3.3 Design Rule Checking                     | 4.16 |

| 4.3.4 Circuit Extraction                       |      |

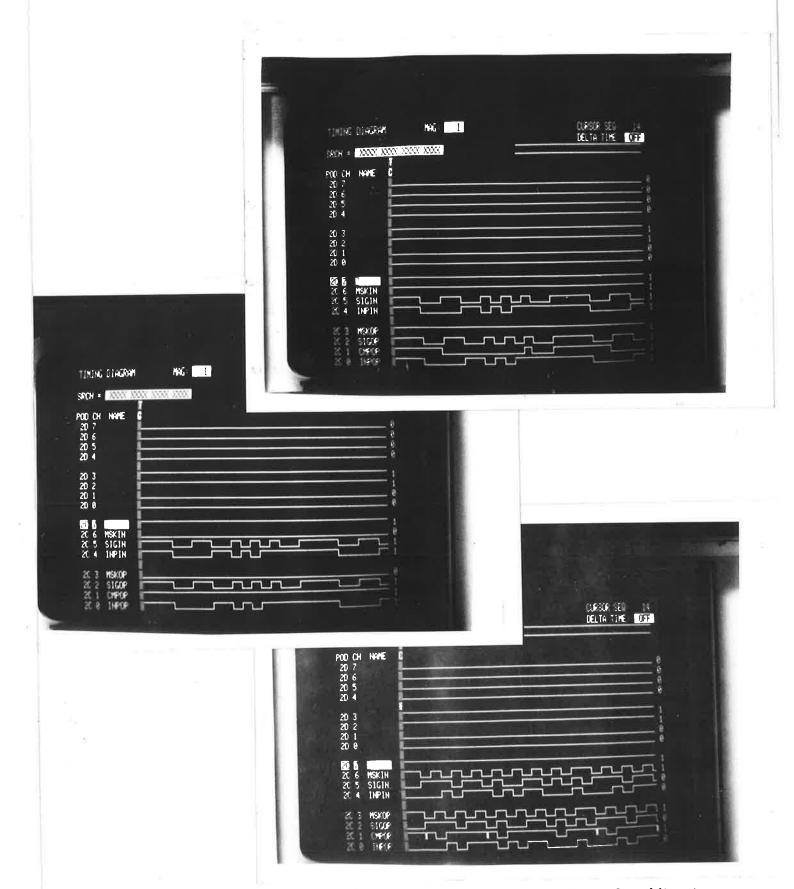

| 4.3.5 Simulation                               | 4.23 |

| 4.4 IC Testing                                 |      |

| 4.4.1 Fabrication Process Testing              |      |

| 4.4.2 Design Functional Verification Tests     | 4.36 |

| 4.4.2.1 Regular Bit Pattern Tests              | 4.38 |

| 4.4.2.2 Pseudo-Random Bit Pattern Tests        |      |

| 4.5 Analysis of CSIRO MPC Efforts              |      |

| 4.6 Control Unit for a Four Bit Microprocessor | 4.46 |

| 4.7 Analysis of JMRC MPC Efforts               |      |

| 4.8 Conclusions                                |      |

| 4.0 Conclusions                                |      |

## Chapter V

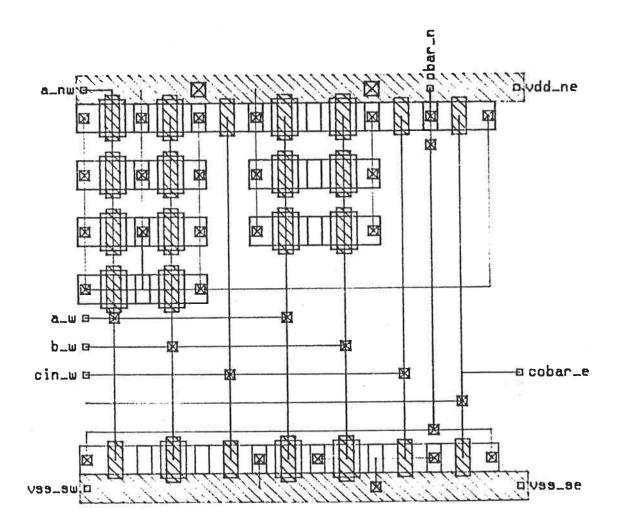

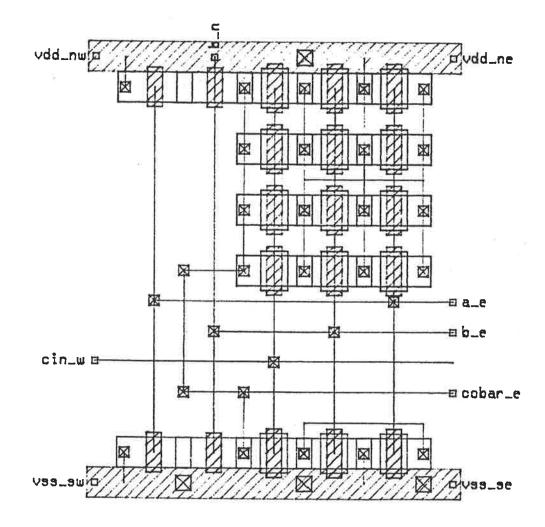

## A CMOS ADDER DESIGN USING HIGHER LEVEL TOOLS

| 5.1 Introduction                                         |

|----------------------------------------------------------|

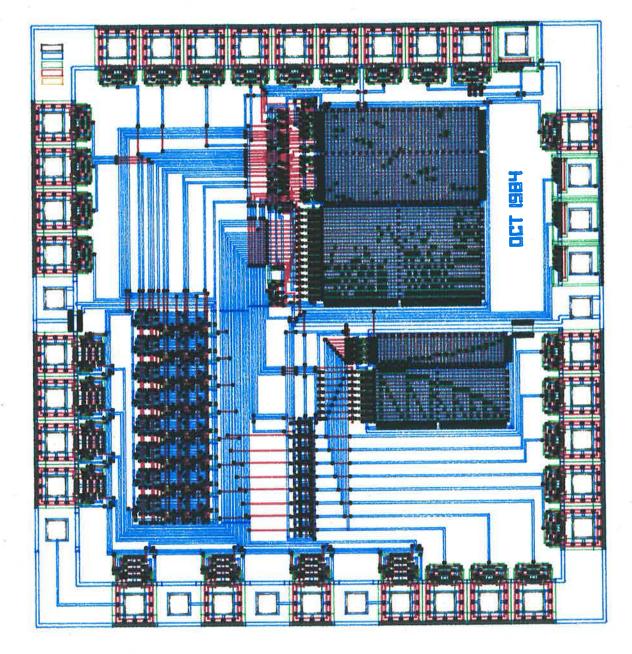

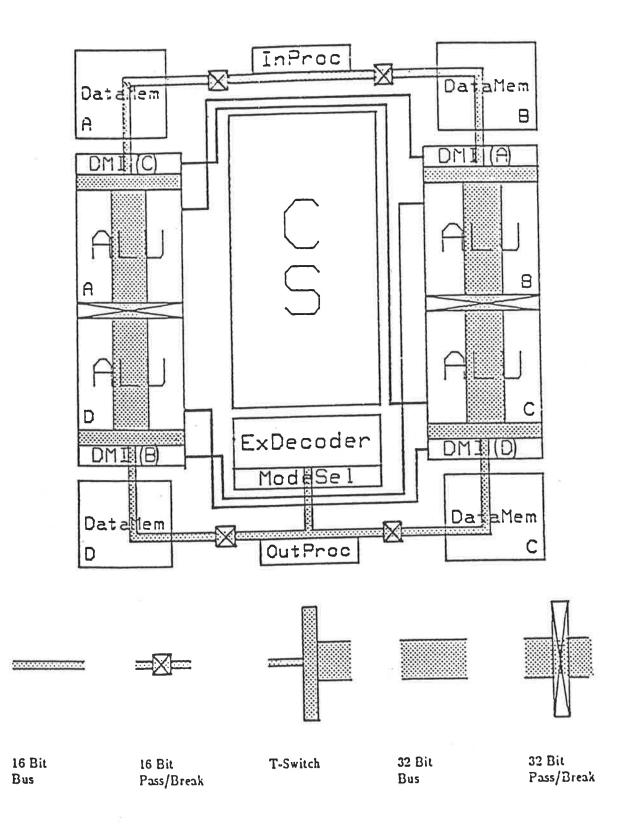

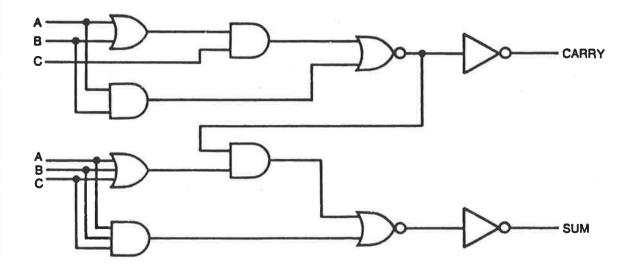

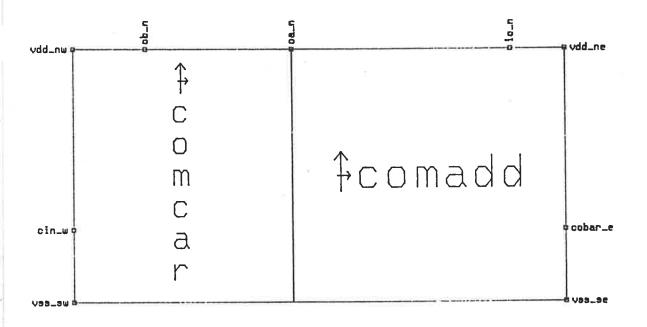

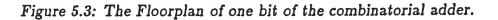

| 5.2 A CMOS Adder Design                                  |

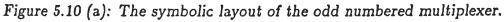

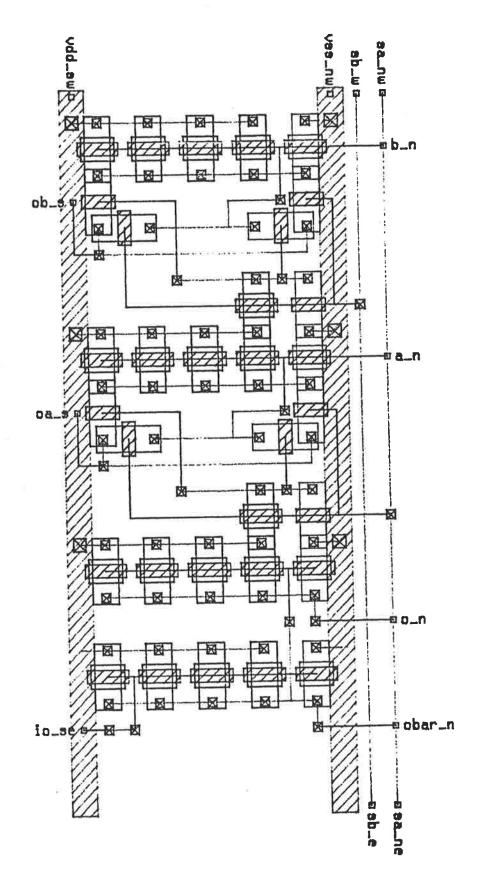

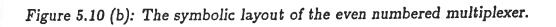

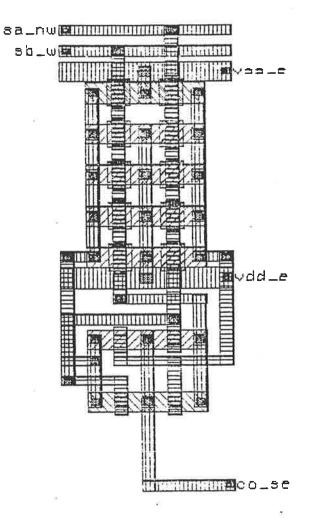

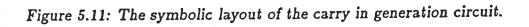

| 5.3 Symbolic Layout of the Combinatorial Adder           |

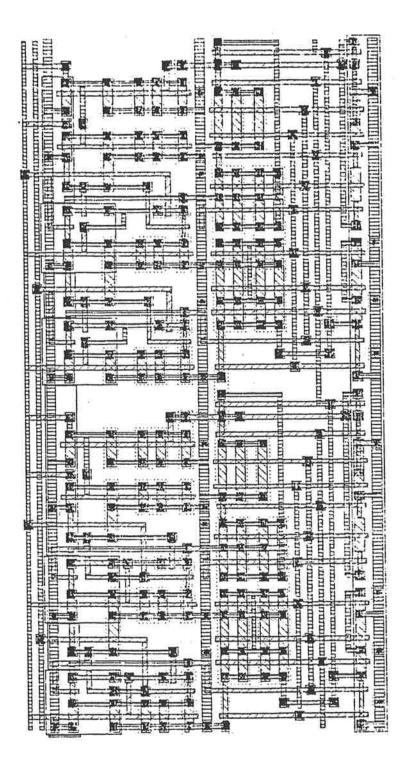

| 5.4 High Level Extraction and Simulation5.20             |

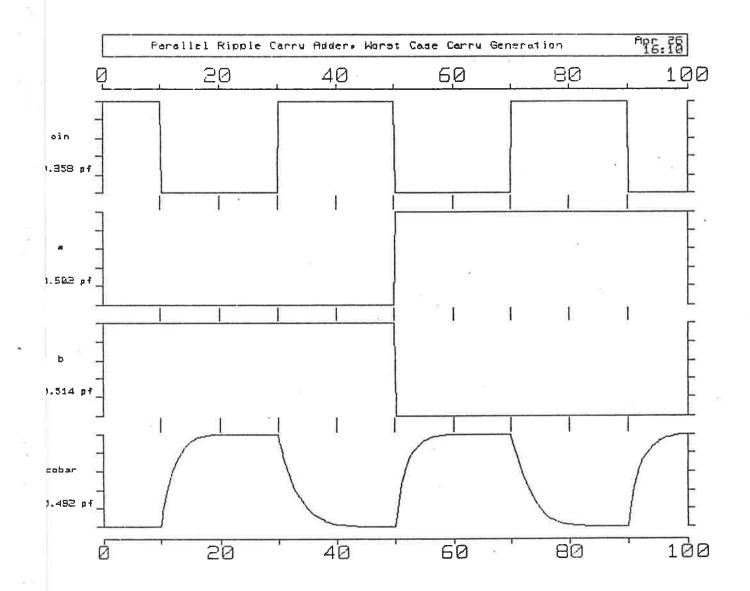

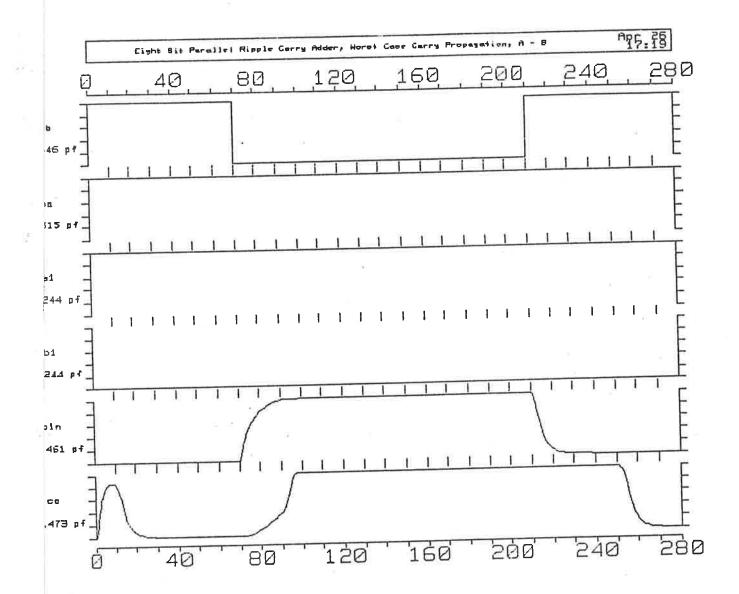

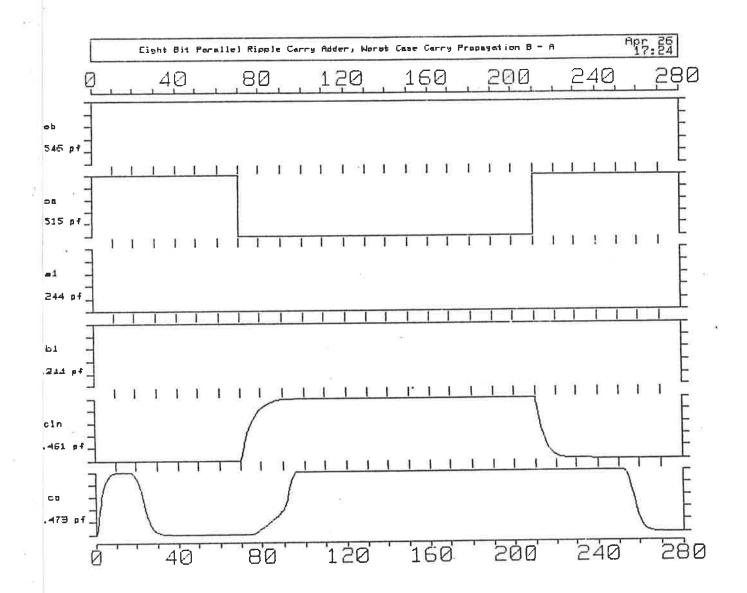

| 5.4.1 Simulation of the Carry Generation Stage           |

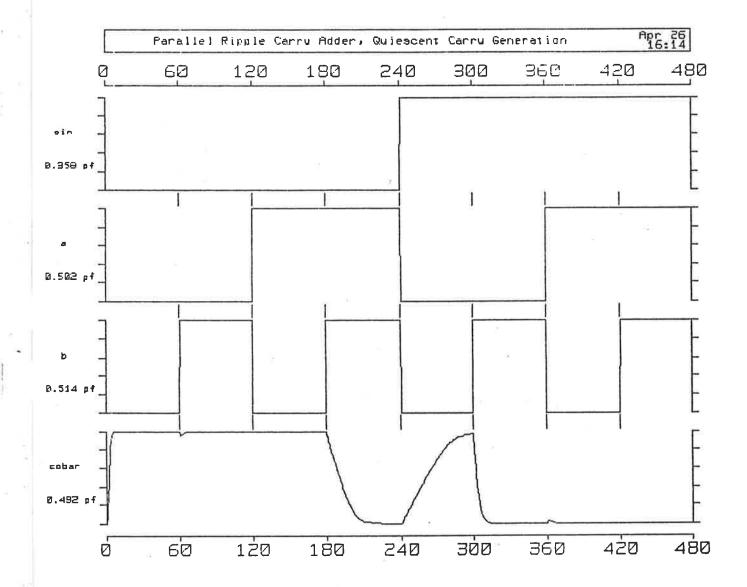

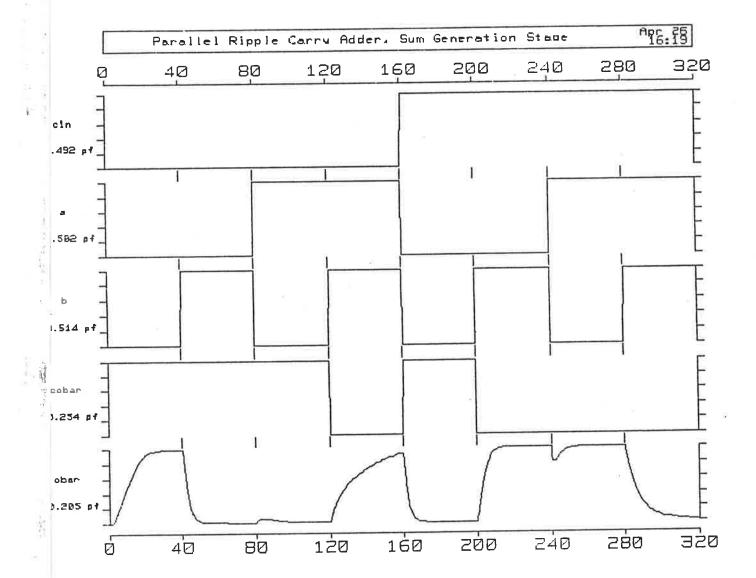

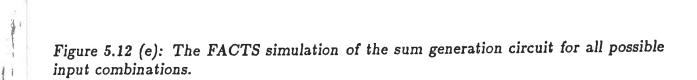

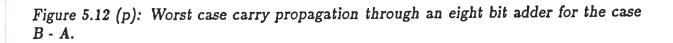

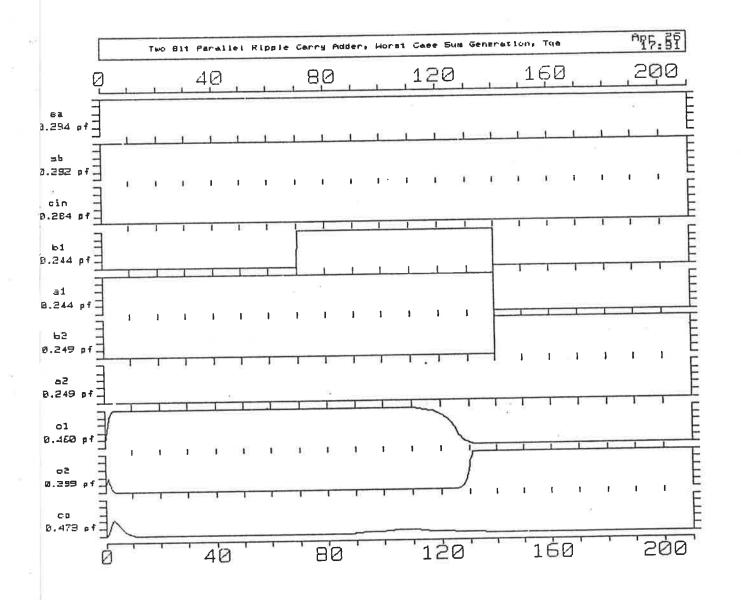

| 5.4.2 Simulation of the Sum Generation Stage             |

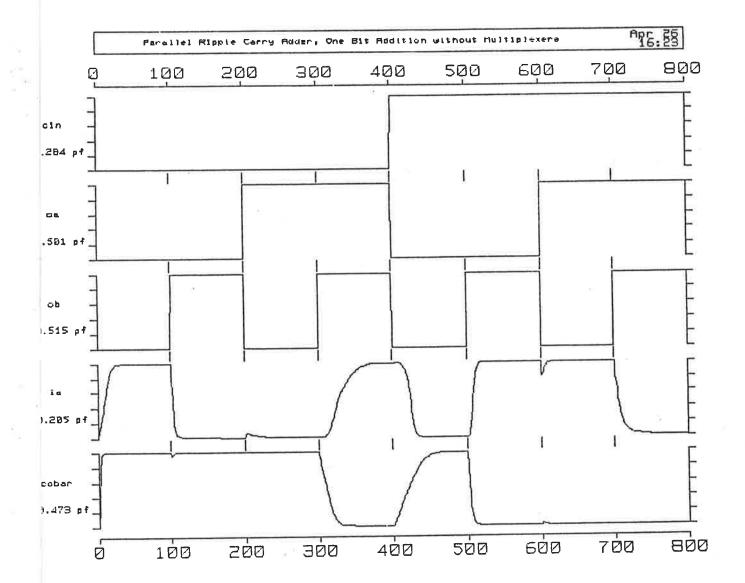

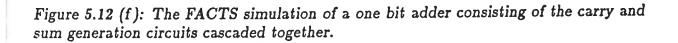

| 5.4.3 Simulation of a One Bit Adder 5.29                 |

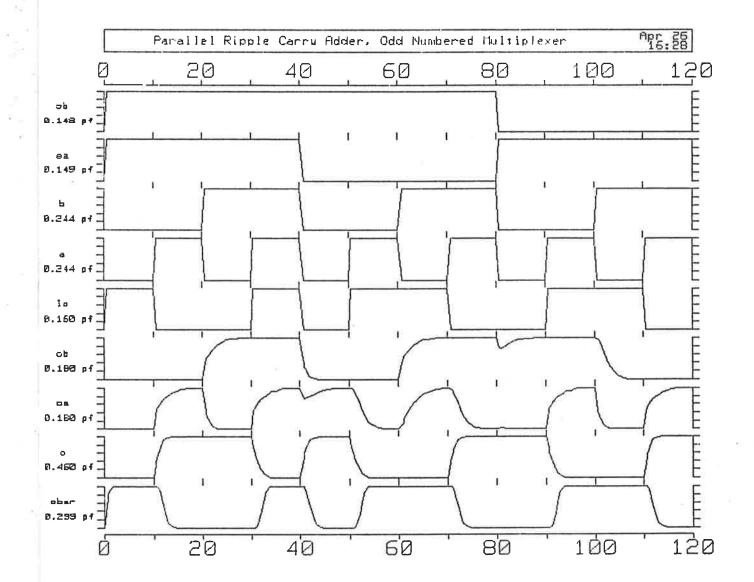

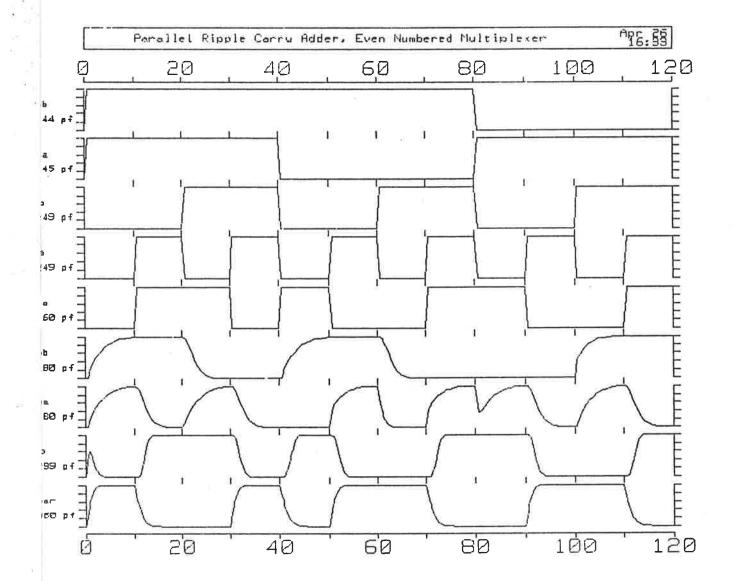

| 5.4.4 Simulation of the Odd and Even Multiplexers        |

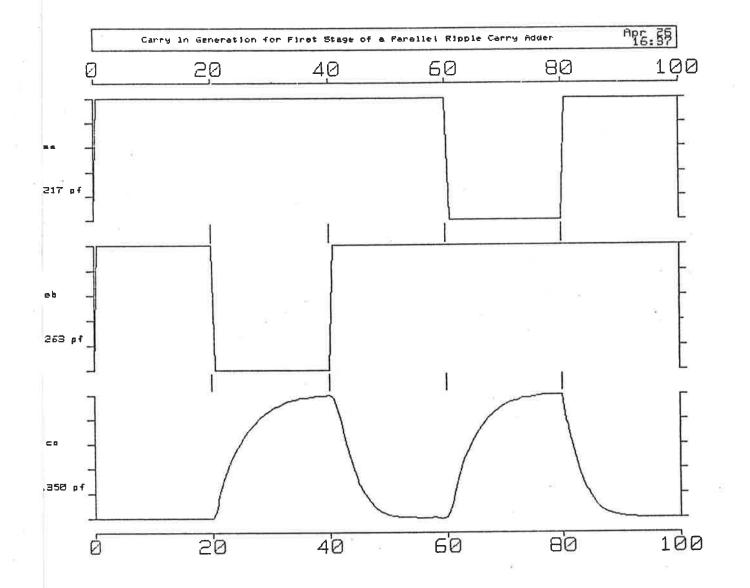

| 5.4.5 Simulation of the Carry In Generation Circuit 5.35 |

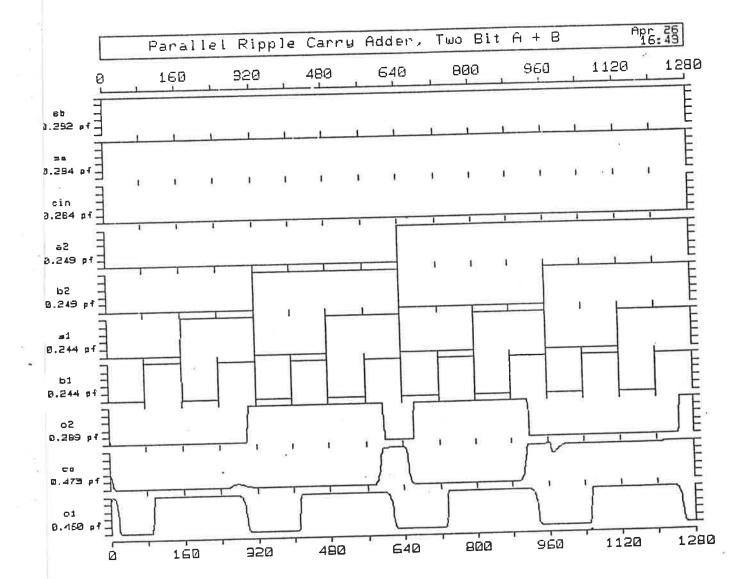

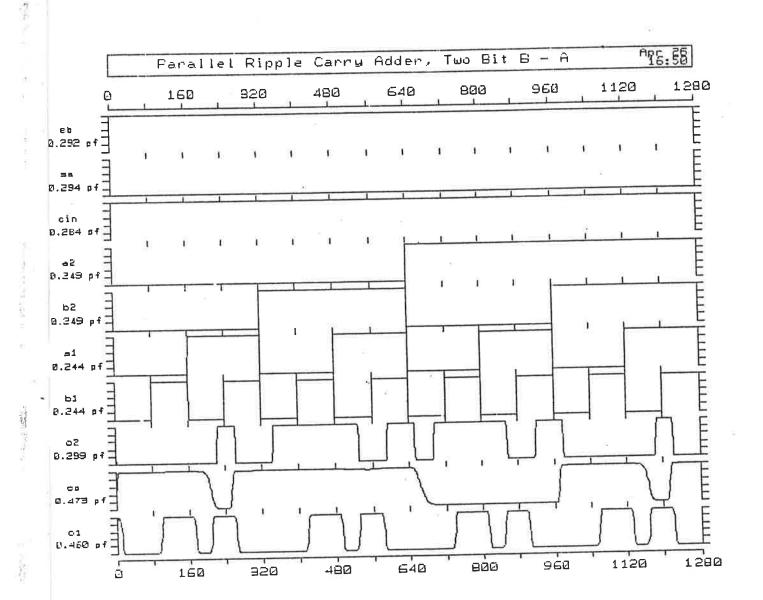

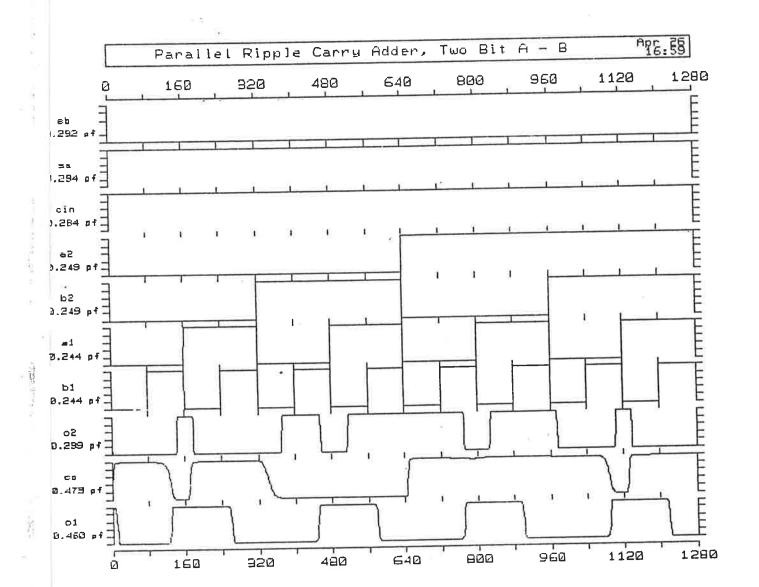

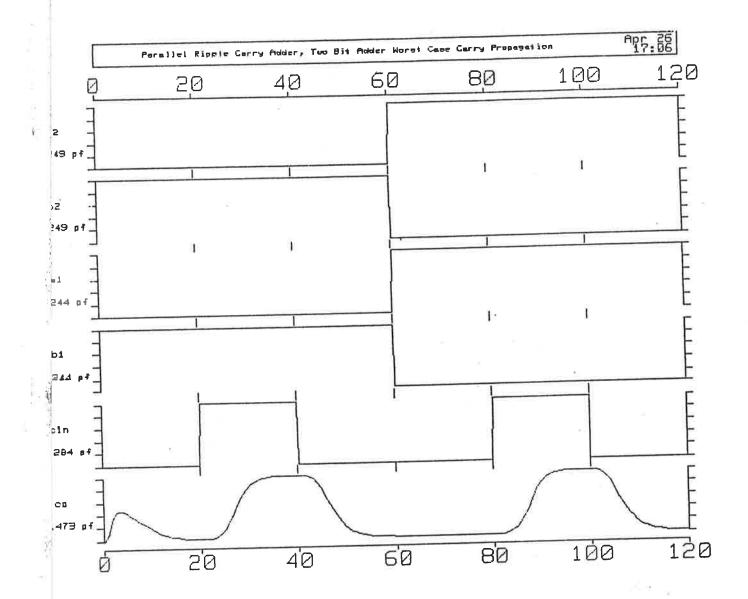

| 5.4.6 Simulation of a Two Bit Adder                      |

| 5.4.7 Simulation of an Eight Bit Adder                   |

| 5.5 Compaction and Mask Level Verification               |

| 5.6 CMOS MPC Fabrication and Conclusions                 |

## CHAPTER VI

## ANALYSING THE PAST AND LOOKING INTO THE FUTURE

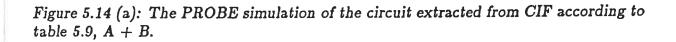

| 6.1 Mask Level Tools       6.1         6.2 Symbolic Level Tools       6.3         6.3 CMOS MPC's       6.6         6.4 Higher Level Tools of the Future       6.7         6.4.1 CADRE       6.7         6.4.2 Silicon Compilation       6.10 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCES                                                                                                                                                                                                                                   |

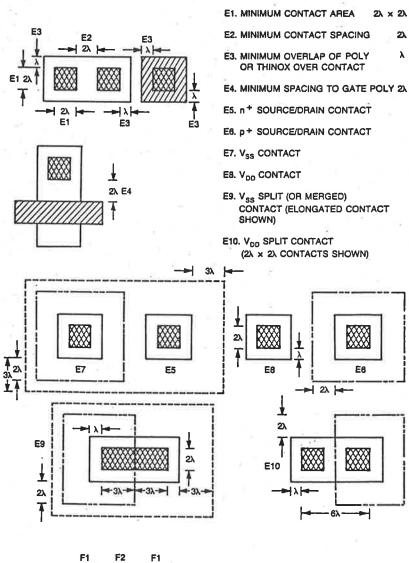

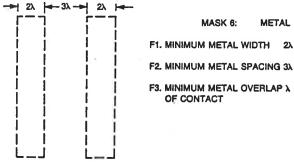

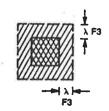

| APPENDIX A: Mead and Conway nMOS $\lambda$ Based Design Rules                                                                                                                                                                                |

| APPENDIX B: BELLE1 ManualB.1                                                                                                                                                                                                                 |

| APPENDIX C: ROWAN Technology File                                                                                                                                                                                                            |

| APPENDIX D: BELLE and CIF for the Signature AnalyserD.1                                                                                                                                                                                      |

| APPENDIX E: Weste and Eshraghian CMOS Design RulesE.1                                                                                                                                                                                        |

| APPENDIX F: CIF, LLAMA and ABCD Descriptions of a CMOS CircuitF.1                                                                                                                                                                            |

#### Synopsis

This thesis analyses a range of Computer Aided VLSI design tools that have been developed at the University of Adelaide. The work reviews different IC technologies and summarises some of the overall philosophies behind the development of VLSI CAD tools. In addition, Multi Project Chip processes and their relationship to various CAD tools is examined and thoughts offered on the merits of full custom IC design as opposed to semi-custom design techniques. The work for this thesis has been completed over a four and a half year period beginning in early 1982, when MPC processes were first introduced to Australia. As a result, the comments made on VLSI design software and MPC processes are strongly associated with the problems experienced with these topics in the Australian environment.

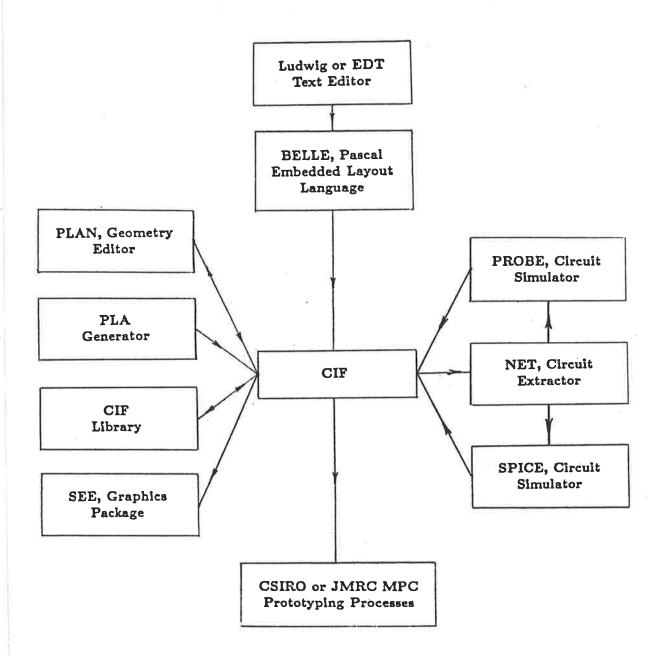

An investigation of a mask level CAD tool set is made and a summary of the tools comprising the complete set, by comparison with some early generation tools that originated from other universities such as USC Berkeley and MIT, is then offered. The work also investigates a symbolic level CAD tool set, the VIVID system, which originated from the Microelectronics Center of North Carolina to run under the UNIX operating system. VIVID was developed for the VMS operating system by ongoing research at the University of Adelaide. In addition, other tools that are generally classified as higher level tools than either mask or symbolic level tools are also discussed for the purposes of comparing the directions of tool development.

The thesis presents a detailed analysis of the tools discussed by presenting one complete nMOS MPC design experience in detail (including testing of the fabricated product), and providing information on a second design experience for the purposes of comparison of the layout tools discussed. The results of this work also allow comparison of two different Australian MPC processes using the nMOS technology as both designs discussed were fabricated using different MPC processes.

A similar account of a detailed design experience using the CMOS technology in conjunction with the symbolic level tools is presented and new Australian CMOS MPC process foreshadowed. This experience, considered with the earlier mask level design experiences, provides the basis for some final comparitive results to be made between the relative efficiency of designing IC's with low level and high level tools. As a result, the work finally presents conclusions regarding the future development of VLSI CAD tool sets with particular reference being made to Silicon Compilation.

The thesis tries to draw an analogy between levels of VLSI CAD tool sets and levels of languages used to program computers in an effort to indicate possible future directions for development of these tools. In particular, the thesis examines reasons why the symbolic level tools may prove to be the first step on the way towards making true Silicon Compilation a reality.

Two different IC technologies, nMOS and CMOS, are used to allow the close analysis and investigation of these tool sets. A number of circuits have been fabricated using the tools and Australian MPC processes and the simulated and tested results of the designs are used to verify the conclusions regarding the tools.

#### Declaration

This thesis contains no material which has been accepted for the award of any other degree or diploma in any university, and to the best of my knowledge and belief, contains no material previously published or written by any other person, except where due reference is made in the text.

v

J. A. Noonan

#### Acknowledgements

In the production of this thesis I must thank my supervisor, Dr. Kamran Eshraghian, for providing the boundless enthusiasm he constantly brims with. This enthusiasm has served as a source of encouagement to continue on with a very complex task. I also owe a great debt of thanks to Mr. Michael Liebelt who provided the highest quality technical assistance and at times helped me to solve seemingly insurmountable problems, not the least of which was the proof reading of this thesis. Thanks also must be offered to Theo Kermanidis for assisting with the proof reading. I would also like to say what a pleasure it has been working with the Electrical and Electronic Engineering Department staff and researchers at Adelaide University.

Finally, I would like to thank Andrew Trevorrow for his patience and assistance in helping me create this thesis using Donald Knuth's TEX typesetting system. I will find it hard ever to use pencil and paper again.

J. A. Noonan.

## CHAPTER I

## IC TECHNOLOGIES AND DESIGN

### 1.1 Introduction to IC's and a VLSI Technology Choice

Since the invention of the first transistor by Bardeen, Brattain and Shockley in December 1947 at Bell Telephone Laboratories, Murray Hill,  $N.J.^{[1][3]}$ , Microelectronics has progressed rapidly. Perhaps the best example of this progress is indicated by the attempts to classify the progress in computer technology.

Computers have so far been classified into four distinct generations, with the beginnings of a fifth currently being researched<sup>[2]</sup>. The first four generations are all characterised by their basic building blocks, (1) the vacuum tube, (2) the transistor, (3) the Integrated Circuit (IC) and (4) the Large Scale Integrated (LSI) or Very Large Scale Integrated (VLSI) Circuit. The fifth generation on the other hand is characterised rather by advances in software, in particular advances in Artificial Intelligence (AI)<sup>[2]</sup>.

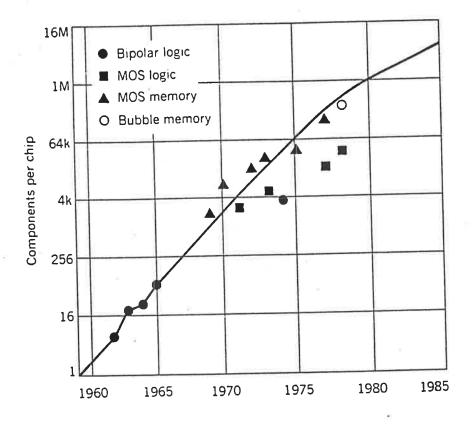

Integrated Circuits are combinations of basic circuit elements, such as diodes, transistors, capacitors and resistors interconnected on a common substrate or base material. They are fabricated by various processing techniques allowing simultaneous formation of large numbers of these devices. Development of the planar process techniques and IC's did not begin until 1958, 10 years after the invention of the transistor<sup>[3]</sup>. With these first IC's came the realisation of their potential and rapid development followed<sup>[3,1]</sup>. G. E. Moore, President of INTEL Corp., produces excellent plots of statistics which indicate accurately the precise extent of these developments. Fig 1.1 relates the number of components per chip to time since the beginning of the semiconductor industry, which is one simple measure of IC development.

The varying scales of integration are themselves classified into four categories. The invention of the IC in 1958 heralded *Small Scale Integration* (SSI- fewer than 100 transistors per chip) and the first commercial IC's entered the market in 1960 with a Minimum Feature Size of  $25\mu m^{[4]}$ . Minimum Feature Size has progressively shrunk to the Medium Scale Integrated (MSI- less than 1000 transistors per chip)  $10\mu m$ , the early Large Scale Integrated (LSI- less than 10,000 transistors per chip)  $5\mu m$ , and now onto the Very Large Scale Integrated (VLSI- greater than 10,000 transistors per chip)  $1\mu m$  and expected sub micrometer levels<sup>[5]</sup>.

Figure 1.1: Gordon Moore, President of INTEL Corp., has produced much graphical evidence to support his predictions. Here is a plot he produced of Number of Components per Chip vs Time Since the Beginning of the Semiconductor Industry, produced in 1979.

Minimum Feature Size is commonly quoted as it is an indication of the sophistication of a particular technology. This measure describes the minimum width of any of the mask level geometries for a particular technology, see Appendix A. It is expected that the maximum scale of integration will be reached when Minimum Feature Size reduces to approximately the 0.1  $\mu m$  level using currently favoured IC technologies<sup>[71]</sup>.

Introduction

A number of different types of IC structure exist. These include Thin-Film and Thick-Film IC's, Monolithic IC's, and Hybrid IC's. The advances in integration to the VLSI level have all been made using monolithic IC's.

Monolithic IC's begin with an extremely pure monolithic (single crystal) semiconductor base, which could be Germanium, Silicon, or Gallium-Arsenide, but is usually Silicon. This base is exposed to a number of chemical deposition, etching, and diffusion phases, patterned by photolithographic masking techniques. The result of this complex sequence of materials-processing steps is a layered, three dimensional circuit atop and within the monolithic base. The specific structural features required for IC's include the basic circuit elements, transistors, diodes, capacitors, resistors as well as isolation and interconnection. The PN junction is the basis of operation of all semiconductor devices with the two most important active devices being, (1) the Metal-Oxide Semiconductor (MOS) or Insulated Gate Field Effect Transistor (FET) and (2) the Bipolar Junction Transistor (BJT).

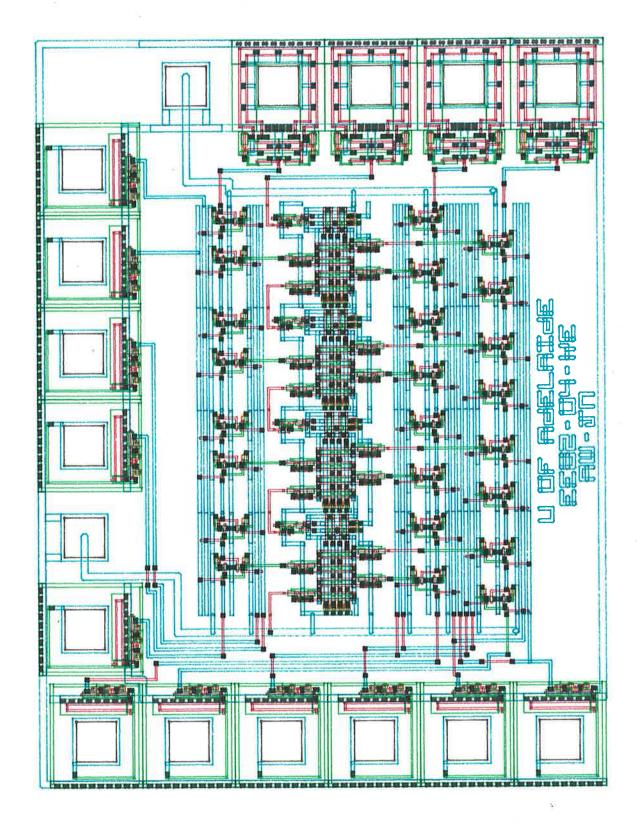

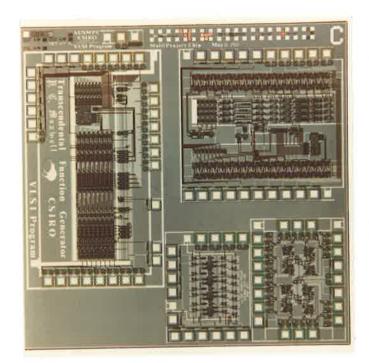

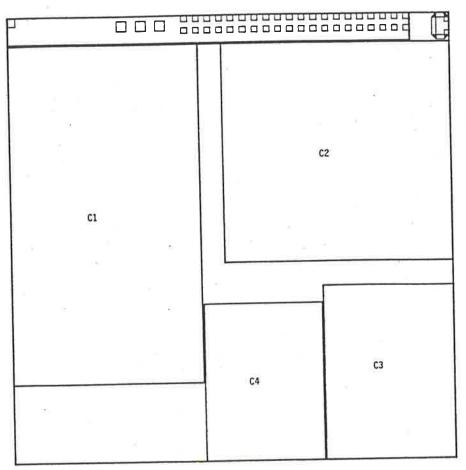

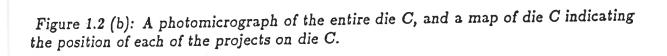

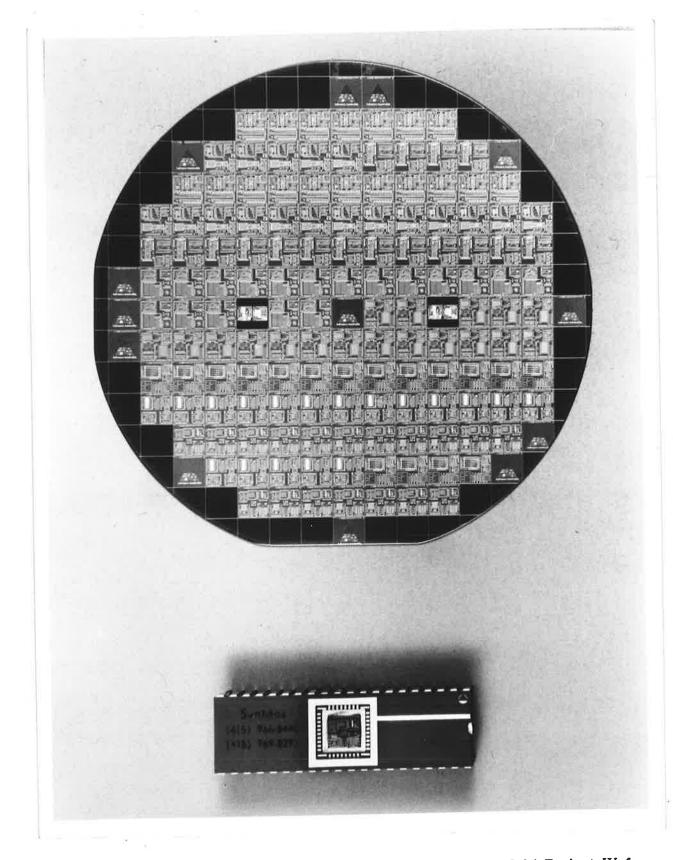

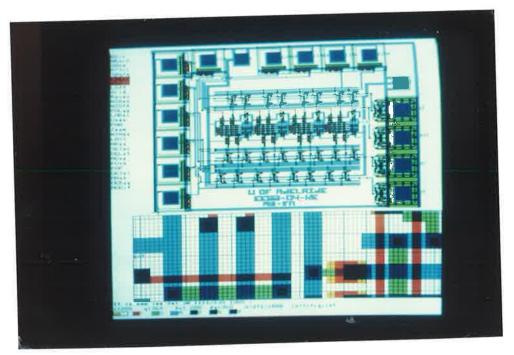

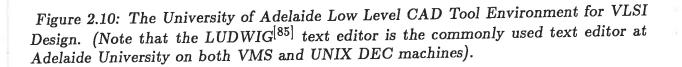

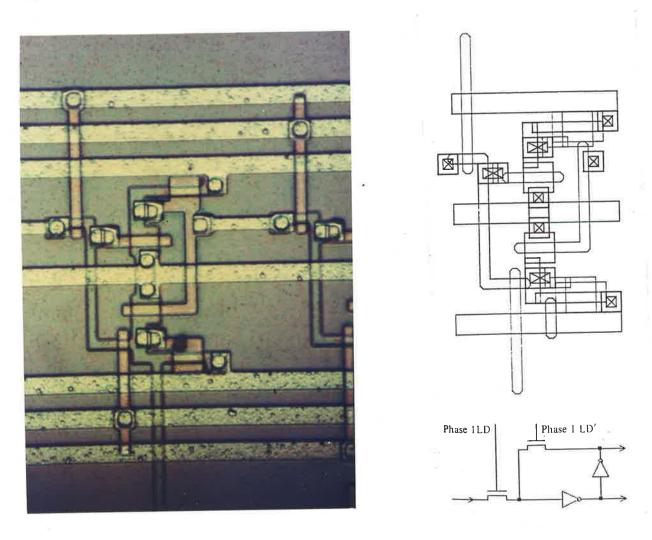

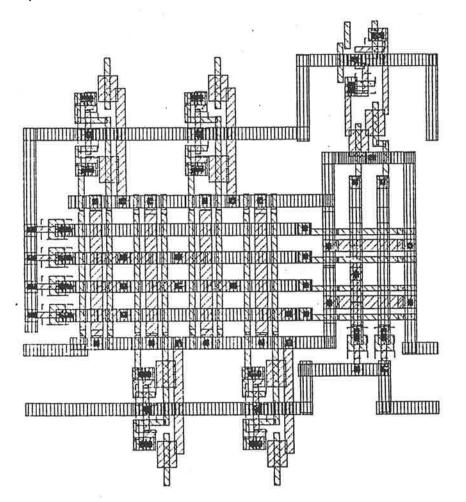

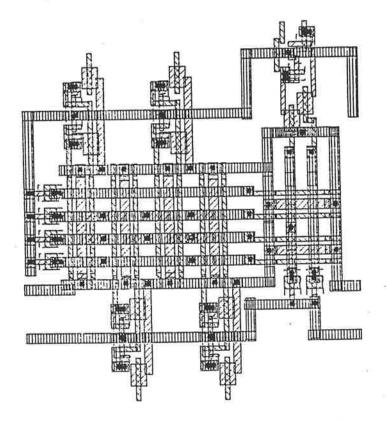

The mask patterns, see Fig. 1.2, forming IC layouts are prepared in arrays of squares with dimensions typically in the order of 5mm by 5mm. This array of mask patterns is designed to cover the whole area of a semiconductor wafer with a diameter in the order of 3 to 4 inches. The individual squares are referred to as dice (chips). Each die (chip) carries the designed circuit and can be separated and packaged individually to perform its required function, see Fig. 1.3.

There are many different technologies available for use in fabricating monolithic IC's. Bipolar or MOS technologies, Transistor Transistor Logic (TTL), Integrated Injection Logic ( $I^2L$ ), Emitter-Coupled Logic (ECL), n-channel or p-channel MOS (nMOS, PMOS), Complementary MOS (CMOS), or Silicon On Insulator (SOI) MOS IC's to name some of the more common technologies. The circuits that can be designed using these technologies are advantageous because of their low power consumption, small physical size and resultant low weight and cost<sup>[9]</sup>. Not all of these are suitable for VLSI design. Factors that must be considered in choosing a particular

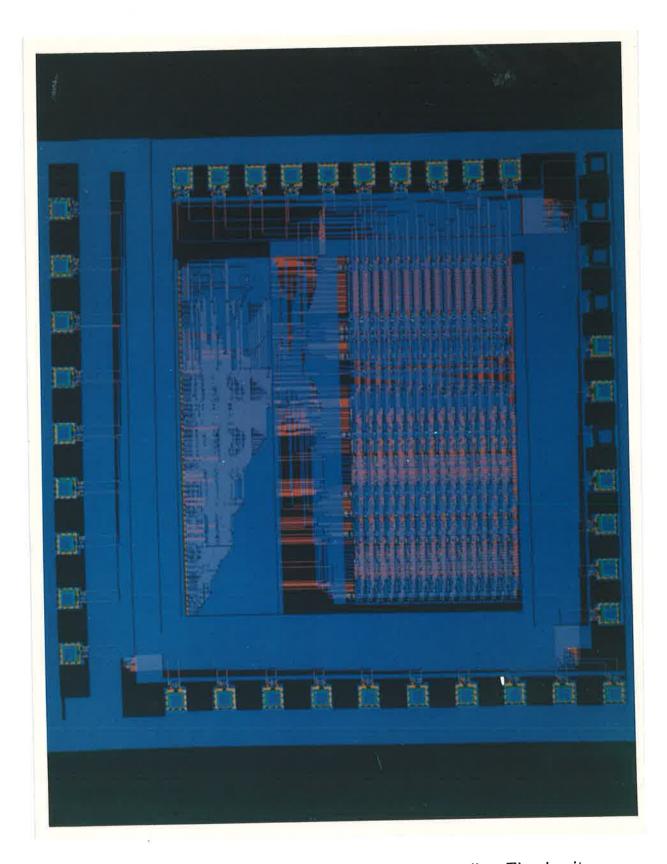

Figure 1.2 (a): A computer generated plot of the mask level layout of project C4, an nMOS MPC design fabricated on AUSMPC May 1982. C4 implies project number 4 on die C. Included is a photomicrograph of project C4 on die C.

Figure 1.3 (a): A photograph of the 4 inch AUSMPC May 1982 Multi Project Wafer and a 40 pin package with the lid off, exposing the bonded die. The bonded die can actually be recognised as die H on the wafer, using the map in Fig. 1.3 (b) and the photograph of the wafer above.

Figure 1.3 (b): A map of the 4 inch AUSMPC May 1982 wafer and a close up of an unbonded version of project C4.

technology for design are circuit density, circuit functionality, power consumption and performance, topological properties of the circuit for interconnection, suitability for total system implementation, and availability of processing facilities<sup>[8]</sup>.

These points considered, the MOS technologies, in particular nMOS and CMOS are attractive. MOS devices are particularly well documented and easy to design, as long as the designer uses a set of design rules and stays away from the smallest geometries feasible<sup>[7]</sup>. With a relaxed set of design rules, the performance of standard MOS circuit blocks are as predictable as TTL circuits<sup>[7][8]</sup>. Finally, both nMOS and CMOS circuits can be fabricated in Australia. As a result, the two monolithic IC technologies used to illustrate the *Computer Aided Design* (CAD) systems discussed in this text will be nMOS and CMOS. It should be understood at this point however that while these CAD systems are discussed in relation to these two technologies, most of the CAD tools are easily modified to handle new technologies as they become available.

## 1.2 The VLSI Design Philosophy

Just as programming was done throughout the 1950's by small groups of highly qualified people solving problems in their own style, IC design in the 1970's was still done by small groups of "layout wizards"<sup>[7][12]</sup>. The advances in computer technology have however introduced powerful aids for design, and with the passage of time IC processing techniques are beginning to become reasonably standardised. As a result, IC design is very quickly becoming a routine engineering step in the development of a special purpose system<sup>[7]</sup>.

As IC process technology has moved from the LSI to the VLSI generation, new problems for the circuit designer have rapidly emerged. These problems can perhaps be most conveniently grouped under the one heading, Complexity Management<sup>[5][11][12]</sup>. An excellent understanding of these problems can be gained by considering a layman's analogy as presented by Moralee<sup>[5]</sup> relating geographical feature sizes to circuit feature sizes.

This analogy relates a 1km square street map of London to the complexity involved in a 1mm square die size,  $25\mu m$  feature size SSI chip. Moralee then indicates that a typical LSI 5mm square die with a  $5\mu m$  feature size, is of similar complexity to a 25km square street map of London, or almost the whole of the Greater London area covered by the A-Z book of maps. While it is possible for anyone to hold in their minds the details of a 1km square street map of London, only a London taxi driver could ever be expected to keep mental track of a street network 625 times the size.

The LSI designer is faced with a similar daunting task if he is to know his circuit layout. The VLSI designer however is confronted by die sizes of around 1cm square with feature sizes of around 1 $\mu$ m which translates to a map covering a 250km square, or a map which would fill 100 volumes of the A-Z book of maps and cover most of the southern half of England. Even this scale of complexity is dwarfed by the expected mature VLSI devices of the late 1980's with die sizes of 2cm square and feature sizes of 0.25 $\mu$ m, or a map of a street network which would be 2000km square, covering practically the whole of central and western Europe. Obviously, a "layout wizard" becomes lost at the LSI stage of design and only new design philosophies developed specifically to handle such complexity will provide solutions to the problems presented by LSI and VLSI design.

Mudge<sup>[11]</sup> indicates clearly some paths towards the solution of this complexity problem by the implementation of a structured design methodology, using a coordinated design team aided by sophisticated (CAD) tools. Sequin<sup>[12]</sup> provides a much more detailed scientific analogy to the VLSI design complexity problem. This analogy was touched on by Mudge<sup>[11]</sup> also. Sequin relates in detail the VLSI design complexity problem to the complexity problem faced by software engineers when unstructured programs started to grow to lengths in excess of 10,000 lines of code. The software complexity problem was alleviated by developing and adopting suitable design methodologies, structuring techniques and documentation styles. Many of the lessons learned from this work are also applicable in the VLSI system design domain, although the VLSI designer faces even more problems than encountered in the software design domain. Sequin<sup>[12]</sup> concisely sums up the VLSI design process with his three conceptual concerns:-

1 Functional design: guaranteeing proper behaviour.

2 Implementation: finding a suitable structure.

3 Optimization: fine tuning the physical arrangement.

It is important to note that these three steps in the design process may need to be iterated through a number of times to guarantee that the high level design decisions made in step 1 can be implemented with the available medium in 2.

Design methodologies are continually being developed to fit these steps in the design process. Sequin proposes that the more innovative methodologies so far developed result in design systems primarily produced by people with a strong background in Computer Science<sup>[12]</sup>. It is important to note that these innovative design systems in some cases also owe their origins to people with backgrounds at least as strong in Electrical Engineering<sup>[13]</sup>, as in the case for Weste and Ackland's **MULGA** system and subsequently developed symbolic layout<sup>[13,1][14]</sup> systems.

The trend in the development of these methodologies centres around a desire to design fully custom developed IC's as opposed to semi-custom devices. However, because of the restrictions on the sets of design rules that can be used with such design systems, it is found that the standard processes commonly used for fabricating custom chips for remote designers can involve as much as a two-generation (factor of four) deficiency in performance <sup>[11]</sup> as compared to the leading edge processes used by "in house" designers. Subsequently, as Sequin<sup>[12]</sup> indicates, when rising development costs for VLSI systems become comparable to the fabrication costs of tens of thousands of devices, a faster development cycle at the expense of a less efficient implementation becomes an attractive alternative for many systems. Hence the increasing popularity of gate arrays and other semi-custom alternatives to LSI and VLSI design such as Standard Cell systems.

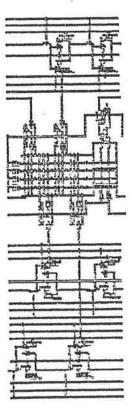

Semi-custom as opposed to Full Custom design offers a "TTL Databook" type approach to system design using gates and library cells. Generally semi-custom IC design limits the number of layers processed by the designer in order to reduce the complexity faced by the designer. In the case of gate arrays, a pre-processed wafer is reconfigured using only a few mask levels. In the case of Standard Cell systems, apart from the reduced number of layers being processed, pre-defined and pre-laid out function blocks are used, further decreasing the design complexity faced by the designer. These pre-defined blocks are connected using routing and placement routines. Both of these approaches to VLSI design allow the designer to customize an underlying matrix of cells. In the case of gate arrays, these cells are basic, while more complex cells up to the MSI scale, are used in the case of Standard, or Library cell systems<sup>[14.1][14.2]</sup>. In both the Standard Cell and Full Custom VLSI design methodologies, an entirely new, full set of masks are produced to process an uncommitted wafer, however, Standard Cell design remains less efficient than full custom design in terms of circuit density and performance<sup>[13,1][14,2]</sup>. The ultimate VLSI design methodology will revolve around a single tool which will comprise many other tools. That tool will be a Silicon Compiler. A Silicon Compiler will take a high level system description and automatically translate it into correct circuit implementations in a particular technology. According to Sequin<sup>[12]</sup>, such tools are still in their infancy and it should not be expected that correct, economically viable solutions for arbitrary systems for all combinations of input parameters will be found before the end of this century. However, early Silicon Compilation tools based on the full custom approach to VLSI design as applied to highly constrained architectures are showing promise, notably Macpitts<sup>[14.3]</sup>. Fig 1.4 gives a Macpitts example and is inserted at this point to briefly introduce the characteristics of such tools to the reader. Weste<sup>[48]</sup> explains that most current Silicon Compilers are still characterised by a fixed floor plan. This leaves such tools with no ability to deal with the complexity involved in contemporary full custom IC's. It is expected that, in the future, silicon compilers will synthesise floor plans and circuits in the same manner as a human designer [48].

Figure 1.4: A circuit generated by the Macpitts Silicon Compiler. The circuits generated by current Silicon Compilers are still quite restricted and these tools cannot yet be considered completely versatile as far as Custom IC Design is considered. The code used to describe the circuit above is given in the following three pages.

```

(program frisc 16

(def * power)

(def * ground)

(def * phia)

(def * phib)

(def * phic)

(def reset signal input *)

(def read signal output *)

(def write signal output *)

(def interrupt-request signal input *)

(def interrupt-acknowledge signal output *)

(def address port tri-state *)

(def data port i/o *)

(def p register)

(def s register)

(def m register)

(def a register)

(def b register)

(def i register)

(process cpu 2

reset-cpu

(setq address 0)

(par (setq address 0) (signal read))

(par (setq address 0) (signal read) (setq p data))

(setq address 1)

(par (setq address 1) (signal read))

(par (setq address 1) (signal read) (setq s data))

instruction-fetch

(cond ((not (eq? i 1 (3 2 1 0)))

(setq i (> > i 4))

(cond (( = 0 i) (go instruction-fetch))

((eq? i 2 (3 2 1 0)) (call constant))

((eq? i 3 (3 2 1 0)) (call get-s))

((eq? i 4 (3 2 1 0)) (call set-s))

((eq? i 5 (3 2 1 0)) (call get-m))

((eq? i 6 (3 2 1 0)) (call load))

((eq? i 7 (3 2 1 0)) (call store))

((eq? i 8 (3 2 1 0)) (call goto))

((eq? i 9 (3 2 1 0)) (call if))

((eq? i 10 (3 2 1 0)) (call end))

((eq? i 11 (3 2 1 0)) (call mark))

((eq? i 12 (3 2 1 0)) (call call))

((eq? i 13 (3 2 1 0)) (call return))

((eq? i 14 (3 2 1 0)) (call add))

((eq? i 15 (3 2 1 0)) (call increment))

(t (setq i (> > i 8))

((eq? i 0 (7 6 5 4)) (call nand))

((eq? i 1 (7 6 5 4)) (call subtract))

((eq? i 2 (7 6 5 4)) (call shift)))))

```

```

interrupt

(call push)

(call push)

(par (setq b m) (setq a p) (setq m (+ s 1)) (setq address 2))

(par (setq address 2) (signal interrupt-acknowledge))

(par (setq address 2)

(signal interrupt-acknowledge)

(setq p data)

(go instruction-fetch))

constant

(call push)

(setq address p)

(par (setq address p) (signal read))

(par (setq address p) (signal read) (setq a data) (setq p (+ p 1)) (return))

get-s

(call push)

(par (setq a s) (return))

set-s

(par (setq s a) (call pop))

(go pop)

get-m

(call push)

(par (setq a m) (return))

load

(setq address a)

(par (setq address a)(signal read))

(par (setq address a)(signal read) (setq a data) (return))

store

(par (setq address b) (setq data a))

(par (setq address b) (setq data a) (signal write))

(par (setq address b) (setq data a) (go pop))

goto

(par (setq p a) (go pop))

if

(par (cond ((<0 b) (setq p a))) (call pop))

(go pop)

end

(go pop)

mark

(call push)

(par (setq m (+ s 2)) (setq a m) (return))

call

```

```

(par (setq p a) (setq a p) (return))

return

(par (setq p b) (setq b a) (setq s m) (call pop))

(par (setq m b) (setq b a) (go pop))

add

(par (setq b (+ b a)) (go pop))

increment

(par (setq a (+ a 1)) (return))

nand

(par (setq b (word-nand b a)) (go pop))

subtract

(par (setq b (- b a)) (go pop))

shift

(par (setq a (> > a)) (return))

push

(par (setq address (setq s (+ s 1))) (setq data b))

(par (setq address s) (setq data b) (signal write))

(par (setq address s) (setq data b) (setq b a) (return))

pop

(par (setq address s) (setq a b))

(par (setq address s) (signal read))

(par

(setq address s) (signal read) (setq s (- s 1)) (setq b data) (return))))

```

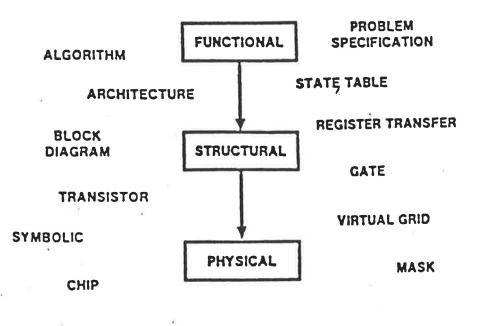

In conclusion, the VLSI design philosophy should take into account all the problems faced by the large software system designer, and many more. Additional problems faced by the VLSI designer are mainly based on the two-dimensional nature of IC's and the need for physical interconnections between modules. The design methodologies introduced in this thesis will be based on two different levels of the design philosophy. The first will be the lowest level, mask level layout description, analogous to machine code in the software domain. The second methodology introduced will be a higher level, symbolic level description, analogous to assembler code in the software domain.

## 1.3 Australian MPC's

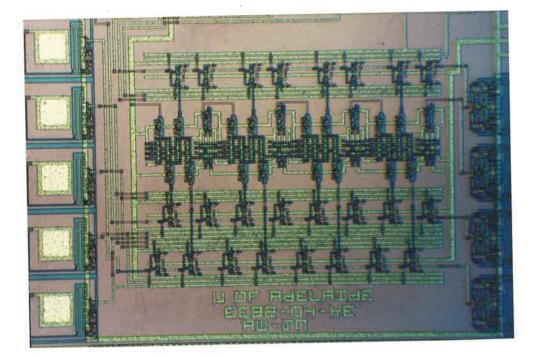

A Multi-Project Chip (MPC) is a chip containing more than one independent circuit design, with each design being considered an independent project. Usually there will be a number of independent MPC's all on the one wafer resulting in the term Multi-Project Wafer (MPW), see Fig's 1.2 (a) and (b) and Fig's 1.3 (a) and (b).

According to Bell<sup>[15]</sup>, the structured design methodology introduced by Mead and Conway<sup>[8]</sup> specifically to handle the design of VLSI systems, required as an integral part of its plan a new implementation methodology for fabrication of IC's. The previously existing method of fabrication of one design per fabrication run could not economically handle the large number of designers trained by the Mead and Conway method. This new methodology still had to rely on existing Foundry services that had the equipment and knowledge to build wafers, but not to handle all the designs. The designer needs only to know that the implemented and packaged chips will be received. This idea is consistent with the intention that the complex design problem be partitioned into manageable blocks.

The work done by Mead and Conway detailing the structured design methodology used in the generation of MPC's based on mask level layouts of nMOS designs, in conjunction with the book produced by Hon and Sequin<sup>[7]</sup>, presented the excellent doc-

Australian MPC's

umentation required as an integral part of the methodology. By actually documenting the techniques involved in approaching a complex task such as VLSI design as well as documenting a set of tools based on this methodology, these researchers have now made it feasible for research organisations such as universities to participate in the design and construction of computing systems totally in silicon. According to Mudge<sup>[11]</sup>, the last time universities could economically compete with systems designers was in the second (transistor) generation.

Simply put, the Mead and Conway methodology for design of VLSI systems requires a structured approach to the mask level design of nMOS circuits using a relaxed set of design rules where mask generation, fabrication and packaging are handled by a **Silicon Broker** or **Foundry**<sup>[19]</sup> which will ultimately return fabricated designs to the designer with a fast turnaround time, at a relatively low cost. The methodology has been used in the US and in Australia for separate MPC fabrication runs and has been shown to work successfully<sup>[15]-[18]</sup>. Most significantly, the designers creating such systems come from diverse scientific disciplines and have already produced significant designs. A good example of some useful designs proven on MPC runs are Richard Lyon's Optical Mouse Chip<sup>[20]</sup> (US MPC run), and a High Speed Digital Correlator designed by J. G. Ables and A. J. Hunt<sup>[21]</sup> (CSIRO Aust. MPC run).

The first Australian MPC effort was initiated by the Commonwealth Scientific and Industrial Research Organisation (CSIRO) VLSI group, an organisation funded federally by the Australian Government, and commenced in earnest with a course given by Dr. K. Eshraghian and Dr. D. Pucknell of Adelaide University<sup>[22][17]</sup> in Adelaide in February 1982. The results of the first and some subsequent MPC efforts can be seen in Mudge and Clarke's reports<sup>[17][18]</sup>. Over the period of the existance of the CSIRO's VLSI Group, mid 1981 to late 1984, 8 successful MPC runs, using both  $5\mu m$  and  $4\mu m$ minimum feature size, were completed. Fig. 1.5 (a) shows a flowchart of the implementation system used by the CSIRO for their MPC effort. Prompted by CSIRO's efforts, the Joint Microelectronics Research Center (JMRC) and Amalgamated Wireless

DESIGN

Design Community:

Designers at .Universities & Other Educational Institutions .CSIRO Divisions .Industry .Government Labs Project coordinators: Project coordinators (one per State) act as an interface from a State's MPC Community to the VLSI Program. COMMUNICATION CSIRONET - IMPLEMENTATION SYSTEM CSIRO VLSI Program, Adelaide Meeting of constraints, Coordination, Logistics, Checking, Merging of designs, interface with various vendors in Australia and U.S. CIF to MEBES: format conversion for electron beam mask SynMos, Mountain View making: Micromask, Santa Clara Mask Making: AMI, Idaho & Comdial, Sunnyvale Wafer Fabrication: Philips, Adelaide & Promex, Palo Alto Packaging: Packaged Chips Returned to Designers

Figure 1.5: The Flowchart of the CSIRO AUSMPC prototyping process. This process was successfully completed 8 times before finishing in 1984. The above flowchart is copied from the CSIRO AUSMPC 5/82 Designer's Manual.

Summary

Australasia (AWA) in Sydney set up their own MPC facility and have also been successful in multiple MPC runs. Fig. 1.5 is very similar to the flowchart for the implementation system used by JMRC. The main differences arise in the Communication block where  $ACSNET^{[73]}$  is used in preference to CSIRONET, and in the Implementation System block where AWA was responsible for Mask Making, Wafer Fabrication and Packaging. Between 1982 and mid 1985, JMRC had successfully completed 10 MPC runs using an nMOS  $5\mu m$  minimum feature size process and in mid 1985 commenced efforts towards running a CMOS MPC. The University of Adelaide Dept. of Electrical and Electronic Engineering is also in the process of commencing CMOS MPC efforts. Both JMRC and Adelaide University CMOS MPC efforts would use AWA fabrication facilities initially.

Since February 1982 when the Mead and Conway VLSI design methodology was first introduced to Australian circuit designers, there have been numerous nMOS MPC efforts using  $5\mu m$  and  $4\mu m$  processes and the beginnings of CMOS MPC efforts resulting in hundreds of circuits being prototyped in silicon by remote designers with little or no experience in IC design, but with some experience in Computer Science or Electrical Engineering or preferably both. The number of organisations offering MPC runs is beginning to grow as is the number of organisations offering CAD tools for the design of these circuits. IC prototyping of circuits in Australia using MPC fabrication techniques is now a proven reality.

### 1.4 Summary

The intent of this thesis is to illustrate in detail that Australian Industry, Research and Design Centers and University Departments have the capability to allow designers to prototype their systems in silicon at an affordable price with a fast turn around as long as they have the appropriate Computer Aided Design facilities, both software and hardware. This aim will be realised by analysing the effectiveness of a range of different CAD tools as applied to the fabrication of IC's using the MPC process. This thesis provides examples of the MPC process as applied to the nMOS technology, and

Summary

applies the same techniques to indicate the viability of the MPC process as applied to the CMOS technology.

It will be shown that as new technologies become available, using well designed tools, minor modification only is necessary to prepare VLSI CAD tools for use. The protoypes detailed in this thesis have been fabricated by different facilities both in Australia and the US, indicating the versatility of this method of prototyping electronic circuits.

Different design methodologies will be used to show different approaches to the complex VLSI design problem, and a comparison of their performances will be made. Chapter II details the variety of tools used in mask level IC design and compares the operation of many currently used tools. Chapter III introduces higher level tools, based on a symbolic design methodology and compares them to the mask level tools. Chapter IV will provide a detailed account of two nMOS design experiences as a verification of the mask level tools and existing MPC implementation systems, while Chapter V will provide a similar account of a CMOS design experience with the higher level tools, and draw comparisons between the High Level and Low Level Tools.

Full custom as opposed to semi-custom tools will be considered. Semi-custom design methodologies, while prompting research into many useful CAD tools (eg. for automatic placement and routing), and providing economical solutions to certain design problems not yet handled by reasearch CAD tools and design methodologies, will eventually lose favour due to their inherent disadvantages with regard to functional device density and performance which has been shown to be an order of magnitude worse than full custom designs<sup>[14.1]</sup>.

As full custom CAD tools become more refined, as CAD software and hardware becomes less expensive, as standard IC fabrication processes become more commonly available in the US and Australia, and as communication networks become more common and accessible, CAD tools for VLSI circuit design similar to those described in this

Summary

thesis will be used by circuit designers as common practice in prototyping their designs. The methods of prototyping circuits as detailed in this thesis are not new but need to be described as an essential part of the design methodologies. Documentation is also provided on the various Australian MPC facilities and some design experiences. Most of the tools that are examined have been used by many designers for many MPC runs. Some tools are totally new and will soon be tested by fabricating and testing designs on more MPC runs. The tools in particular provide an insight to component parts of the ultimate tool of the future, the Silicon Compiler.

#### CHAPTER II

# LOW LEVEL CAD TOOLS FOR VLSI CIRCUIT DESIGN AND ANALYSIS

Because VLSI design is complex, designers think of their designs not in their full complexity, but rather as collections of parts which may be further decomposed into other parts. This hierarchical viewpoint both expresses the designer's understanding of his design and economises his thinking about it. All unnecessary information is suppressed, enabling the gate, module, subsystem or system of interest to be dealt with.

It is common to talk of these hierarchical divisions by discussing *Leaf Cells* as opposed to *Composition Cells*. A leaf cell contains mask level geometry and usually describes a fundamental block in a large system which may need significant replication or which may be placed in a cell library for use in several designs. Composition cells are groups of leaf cells or other composition cells, or both, which are combined to form larger system blocks. The information available within the composition cells commonly provides cell I/O connection positions and the layer on which the connection should be made, possibly some electrical characteristics of the cell and in some cases, peripheral mask level information<sup>[28]</sup>.

The Broker/Foundry accepts the intermediate form description of the design layout, merges the design with others on an MPC, and then converts the intermediate form of the merged MPC into a form that will drive the chosen patterning mechanism. Currently, design files are converted to Pattern Generator (PG) files for use by a maskmaking firm for driving an optical or Electron Beam pattern generator, which is the first step in maskmaking. By a series of photolithographic steps, a mask house will produce a set of masks which a commercial fabrication house will then use to pattern

silicon wafers. The remaining function of the Broker/Foundry is to have the wafers diced and packaged and yield tested before returning the chips to the designer.

A set of CAD tools should be able to represent the design in much the same way as does the designer. Thus the basis of a set of design tools should be a database representation of designs that is flexible, extensible and hierarchical. This chapter examines some tools and their different approaches to these design principles. For complete analysis of the tools, the ability to handle non-manhattan geometry will be used as one of the criteria for measuring each tool's versatility.

## 2.1 Mask level Design of IC's using MPC's

At the lowest level of programming, machine code, or bit information is loaded into a machine. At the lowest level of IC design, mask layouts are described by the designer. The mask level layout description of an IC design will conform to a set of relaxed design rules as described by Mead and Conway<sup>[8]</sup> (see Appendix A). To adequately describe mask level layouts of IC designs in such a way as to interface effectively with an MPC run, a number of stages must be methodically passed through (see Fig. 1.5).

At the mask level of IC design, the designer must first transform the circuit and topological level designs into a geometrical layout of the system. The design must be verified, so design checks discovering layout errors will be required, these checks will usually be carried out in an iterative manner until the layout is design rule error free. The result will be a design file that accurately describes the layout in a particular representative intermediate form which can be read by a Silicon Broker/Foundry. The intermediate form used by tools discussed in this thesis is the *Caltech Intermediate Form* (CIF<sup>[7]</sup>). Another intermediate form at a different design level will be introduced in Chapter III, however, the basic format that is able to be read by existing foundries is at the lowest design level, that of mask layout.

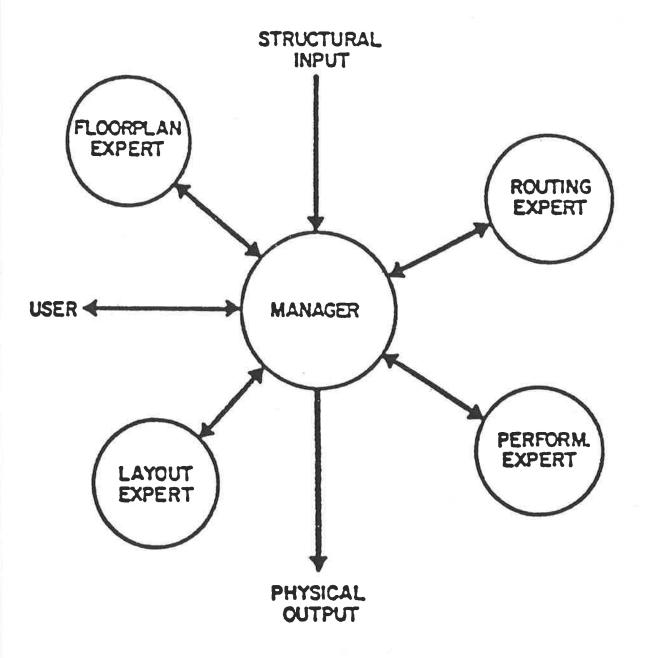

It is important to note that the design rules used with CIF are based on a length

unit,  $\lambda$ . This unit can be scaled up or down as required to match the minimum value of a fabrication facility's process. That is, the  $\lambda$  concept should produce process independent designs. The transit time for transistors, resistance per square and capacitance per unit area will all vary from one fabrication line to another, yet the  $\lambda$  based designs should function correctly if the designs are logically and electrically correct. The following work describes and makes some comparisons of a complete set of CAD tools that have been successfully and extensively used for the design and verification of IC's, at University of Adelaide.

### 2.2 Embedded Layout Languages

Mask level layout tools use high level languages run on general purpose computing systems to provide Mask Layout languages. These Layout Languages generally exploit the features of languages such as PASCAL or LISP to enable faster more efficient digitization of designs into machine readable form (CIF). Mead and Conway<sup>[8]</sup> provide an example of such a language. Other examples are **DPL**<sup>[23]</sup>, a LISP based Layout Language, **BELLE**<sup>[24]</sup> and **CELLE**<sup>[25]</sup>, PASCAL Embedded Layout Languages (see Appendix B). Fig. 2.1 shows an example of a Layout Language and its resultant layout. Such Layout Languages inherit the power of the full programming language in which they are embedded. High level programs can be written that call Layout Language functions and vice-versa. These languages take a symbolic description of mask level layout elements such as boxes, or wires at different mask levels, and process these low level descriptions to produce an intermediate form (in this case CIF) description of the mask layout.

The only CAD peripheral hardware requirements absolutely necessary for design using such languages are a text editing terminal, a plotter, and some means of transporting information from the computing system running the tools to the broker/foundry organising fabrication of the design. This could be done using for example, an electronic mail network, (eg. Australian networks,  $ACSNET^{[73]}$ , or  $CSIRONET^{[72]}$ ), magnetic

<sup>†</sup> ACSNET is a trademark of Sydney University

tape, or even removable disks. The software requirements are a compiler for the high level language used to embed the Layout Language, a text editor (the more versatile the better), and a plotting routine that can take the CIF output from the Layout Language and reproduce a hard copy for investigation.

Mask Layout Languages are programs used to digitize mask level descriptions of IC designs and therein lies a problem. A circuit designer normally considers systems in terms of, at worst, the fundamental electronic circuit components, transistors, capacitors, resistors and wires. The IC designer using a Layout Language however must manage the complexity of his circuit design as well as the non-trivial task of converting that circuit design to a detailed mask layout on paper, prior to digitization. This must necessarily be done on an absolute grid, preferably  $\lambda = 1$  grid spacing. Such digitization techniques are quite tedious and slow relative to higher level tools for IC design, although Mask level Layout Languages provide a more efficient digitization medium than digitizing using CIF, which is possible but not advisable.

The advantages of Mask Layout Languages derive from the power of the parent languages in which they are embedded. Once a significant number of designs have been digitized and verified, a database consisting of a library of these cells can be used in conjuction with the Layout Language for composition of systems.

It is important at this stage to indicate that most of the tools discussed in this thesis create or accept only Manhattan geometry at the mask level. This means that all mask geometry created or processed is parallel to the x or y axis, there are no diagonal lines used. This design restriction significantly reduces the complexity of the IC designs as well as the design of the tools used for their creation and analysis.

#### 2.3 Interactive Mask Level Geometry Editors

Geometry editors provide the ability to interactively manipulate pictorial representations of objects on a monochrome or colour video terminal. Sections of pictures can be inserted, deleted, moved, replaced, or operated on in much the same way as text

#### PROCEDURE dynshift;

```

CONST

```

| Diff_width       | Ξ  | 2; |  |

|------------------|----|----|--|

| Diff_spacing     | =  | 3; |  |

| Poly_width       | =  | 2; |  |

| Metal_width      | =  | 3; |  |

| Pol_Dif_spacing  | Ξ  | 1; |  |

| Pol_Dif_overlap  | =  | 2; |  |

| Impl_over_channe | 1= | 2; |  |

| Impl_to_channel  | =  | 2; |  |

| Cut_size         | =  | 2; |  |

| Cut_spacing      | =  | 2; |  |

| Cut_to_edge      | =  | 1; |  |

| Pwr_width        | Ξ  | 4; |  |

#### VAR

cell\_start: coordtype; cell\_width,cell\_length: integer; begin setsymno(9040); define('dyn\_shift'); cell\_width:=33; cell\_length:=48; Layer(Metal); box(0,0,cell\_width,pwr\_width); box(0,22,cell\_width,22+pwr\_width); box(0,44,cell\_width,44+pwr\_width); Layer(diffusion); box(14,14,20,20); box(14,6,17,15); box(16,6,30,8); box(14,28,20,34); box(14,33,17,42); box(16,40,30,42); wire(2,19,0); y(6); wire(2,0,35); x(6); y(10); x(14); box(15,22,19,26);

```

Layer(poly);

box(22,4,28,11);

box(17,9,20,13);

box(19,9,23,11);

box(17,35,20,39);

box(22,37,28,44);

box(19,37,23,39);

wire(2,13,17); x(26); y(37);

wire(2,12,12); y(-11);

wire(2,3,33); y(59);

wire(2,11,31); x(21);

Layer(Implant);

box(20,4,30,10);

box(20,38,30,44);

```

```

md(-1,34);

mp(28,34);

md(31,42);

md(17,27);

md(17,21);

md(31,6);

dp(17,11,0);

dp(8,32,0);

dp(17,37,0);

```

enddef; end; begin dynshift; setnoend; end;

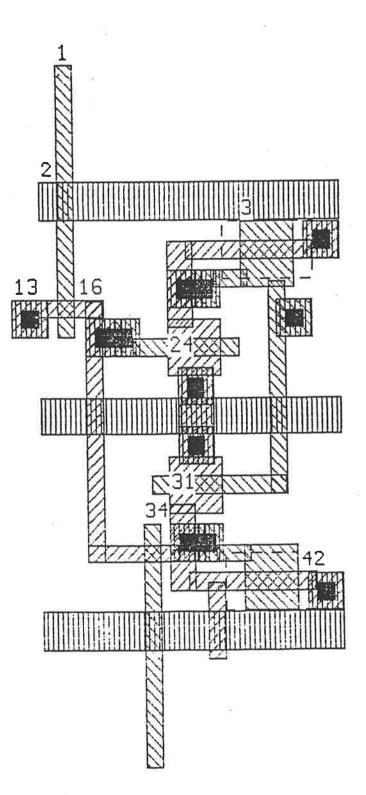

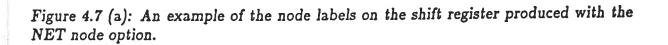

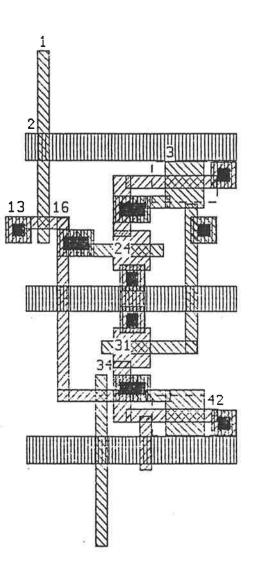

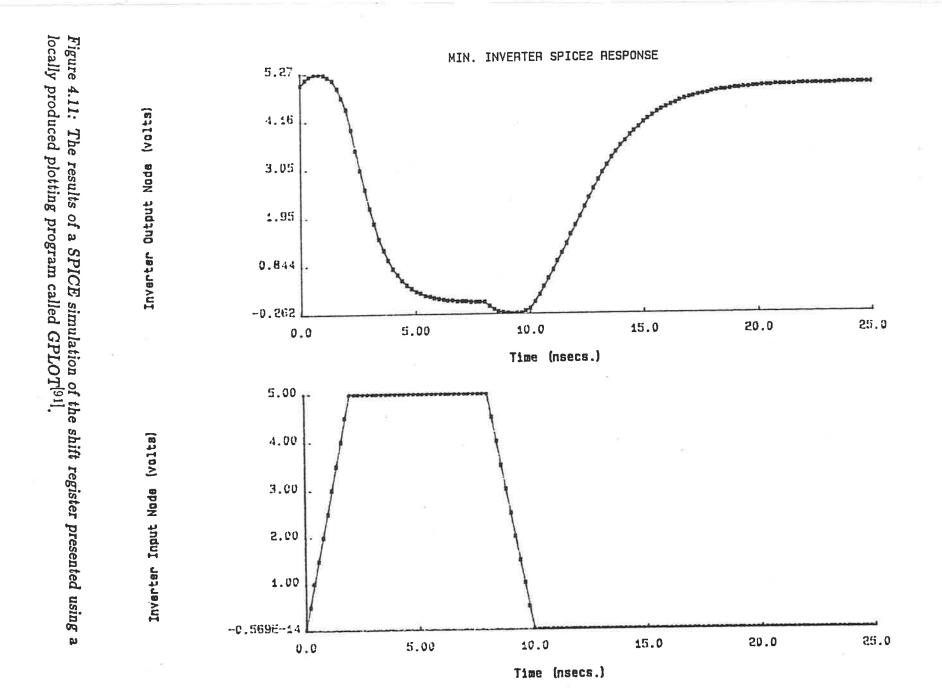

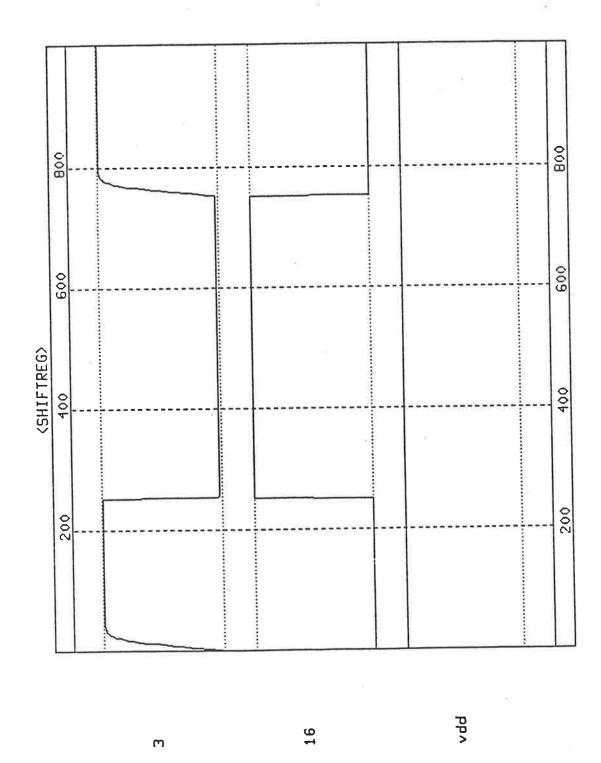

Figure 2.1 (a): A copy of the BELLE Layout Language used to describe the shift register cell designed for use in project C4, AUSMPC May 1982.

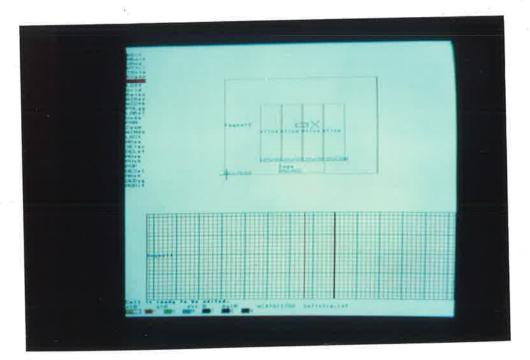

Figure 2.1 (b): A computer generated plot of the shift register cell described in Fig. 2.1 (a).

can be altered with a sophisticated text editor. Tools such as ICARUS<sup>[8]</sup>, **KIC**<sup>[27]</sup>, **CAESAR**<sup>[29]</sup>, **PLAN**<sup>[26]</sup>, **ET**<sup>[28]</sup> and **MAGIC**<sup>[29.1]</sup> are all examples of interactive, mask level, geometry editors.

The advantage in using a geometry editor as opposed to a Mask Layout Language is that the editor can contain all of the Layout Language functions and more. As well, the editor is able to provide visual evidence of the design developments and modifications interactively. The advantage this brings is that no detailed layout need be done on paper beforehand. Some *STICK* diagrams may be required for design guidelines, but even these may be unnecessary for an experienced user of a geometry editor.

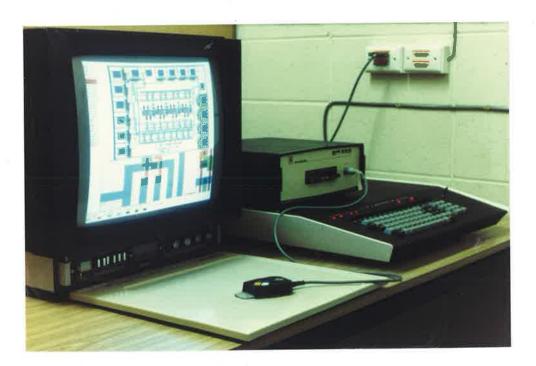

The hardware required to use these tools is the same as that for the Layout Languages, plus either a monochrome or colour interactive graphics terminal, or both, with some method of manipulating cross-hairs on the terminal. This may be done either via the terminal keyboard, or a bitpad, or an optical or mechanical mouse<sup>[20][30]-[34]</sup>. Some typical Workstations are shown in Fig. 2.2 (a), (b) and (c) running various geometry editors. (Workstation is the common noun used to describe the hardware used by a designer to run a complete set of VLSI design tools).

The software required for this type of tool is again similar to the Layout Language software in its philosophy. The differences between the two tools are that as well as performing the layout task that the Layout Language succeeds in achieving, the Geometry Editor also allows interactive editing of layout. The editing task is much more time consuming using a Layout Language and can only be completed using an additional software tool, a Text Editor.

Commonly the structure of a geometry editor provides for a subdivision of the program into a number of procedures corresponding to the number of functions provided by the editor menus. A versatile editor will drive more than one type of graphics device and so usually contains a number of procedures corresponding to the number of device drivers used by the editor. Generally, a Geometry Editor is a much more complex

Figure 2.2: (a) Above, an early model of a colour graphics workstation. An AED512 with a colour monitor and a bit pad showing some KIC output of project C4. (b) Below, a VISUAL 500 monochrome workstation<sup>[30]</sup>, showing some PLAN output of project C4. Note that the cross hairs in this case are controlled from the terminal keyboard.

Figure 2.2 (c): Another colour graphics workstation, a VECTRIX<sup>[37]</sup> with optical mouse for cross hair control. Note also the monochrome terminal alongside used for displaying additional menus and allowing the use of a text editor, or alternatively some other CAD Tool while viewing the circuit on the colour monitor. Also compare the bulky bitpad in (a) with the much more compact optical mouse shown here.

program than a Layout Language as it must perform the same geometry instantiations as a Layout Language, it must display them interactively on a graphics peripheral, and it must also incorporate an editing capability which a Layout Language does not have.

Just as Layout Languages produce CIF output, so do Geometry Editors, but usually not directly. The machine readable output format varies from editor to editor. Generally, it is similar to CIF, but not the same. Additional software must accompany the editor to translate from the editor output format to the desired intermediate form, in this case CIF. It is generally possible to translate from the intermediate form to the editor output format as well. For some tools, this second function tends not to be as useful, because the hierarchical features which are embedded in some of the editors are not translatable to cif. For example, PLAN does not have a routine to transfer from CIF to the PLAN output format because of the hierarchical restrictions imposed by PLAN on a designer.

#### 2.3.1 Hierarchical Design Philosophies of Geometry Editors

Hierarchical information is necessary to simplify the complex IC design task. The form this hierarchical information may take varies from editor to editor, but a simple comparison of KIC, PLAN, and ET, will provide an overview of different approaches to hierarchical IC design using geometry editors.

This comparison is based around innovations in hierarchical design strategies for geometry editors rather than a comparison of the effectiveness of one tool for VLSI design, with respect to another. The three editors named in this section each have very similar geometry manipulation functions and are at different stages of development. KIC was developed at the University of California, Berkeley<sup>[27]</sup>, originally started as a Master's thesis by Keller in 1981. PLAN<sup>[26]</sup> has been developed by a firm called Integrated Silicon Design (ISD), and originated from a project, RIDE<sup>[25.1]</sup> carried out by Dickinson. ET has also been developed at the University of Adelaide as the result of research work by Woloszczuk<sup>[28][28.1]</sup>.

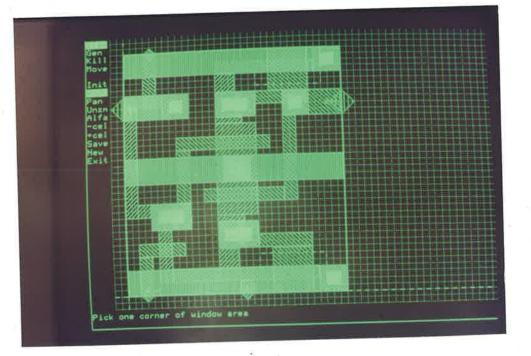

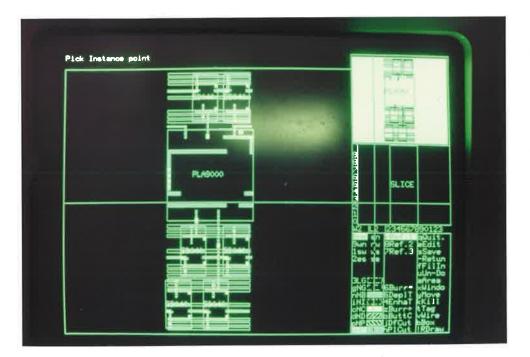

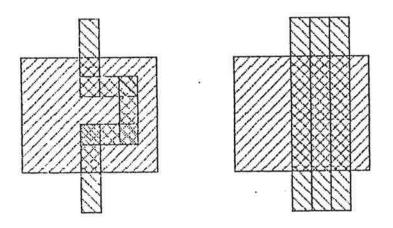

KIC provides no hierarchical design restrictions. The electrical relationship between the cells is not machine recognisable. The onus is on the designer to recognise and account for all connections between cells at the time of composition. The only hierarchical division of cells is a visual bounding box around the perimeter of a cell at the time of composition. Even this hierarchical division may be freely turned on or off by the designer using a menu selection called **EXPAND** which then displays all of the enclosed leaf and/or composition cell information within this top level cell (see Fig. 2.3)

PLAN, however, provides connectivity information as well as the bounding box around the cell. When a cell is generated, pins must be placed on the inputs and outputs of the cell before connection can be made between cells when they are composed. These pins only appear within a bounding box, generally on the edge of the box, and serve

Figure 2.3: The top picture shows a non EXPANded view of project C4 using KIC, while the picture below shows an EXPANded view of the same design. Some interesting KIC features can be seen in these pictures. Firstly the Magnifying Glass, the grided rectangle at the bottom of the pictures providing a magnified view of the contents of the small black rectangle shown in the top picture on the left of the cross hairs. Also the MENU of KIC commands selectable via the bit pad can be seen on the left hand side of the pictures. At the bottom of the pictures can be seen the LAYER TABLE viewport indicating the various mask levels used and their associated colours, while immediately above this viewport is the PROMPT viewport enabling textual input by the designer. The hierarchy in KIC is only implied via the use of non EXPANded bounding boxes as in the top picture.

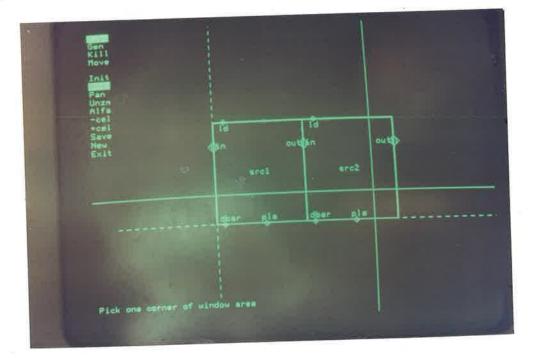

to define the cell electrical input and output ports and act as terminal nodes for wires (see Fig. 2.4). It is worthwhile noting that in PLAN only hierarchical information is displayed at different levels of composition. That is, the designer can only view composition cells as bounding boxes with I/O ports, there is no equivalent to the KIC **EXPAND** menu command. This restricts the designer to a strictly hierarchical design strategy but can cause problems if connection must be made to pins internal to the cell, (a poor design technique), or if layout geometry is placed close to the edges of the bounding boxes of composed cells, as design rules could be violated. In these circumstances, it is necessary to know the internal geometry of the cell or at least the geometry near the edges that could possibly be involved in design rule violation. PLAN does not allow a designer to see internal geometry for composed cells at the time of composition.

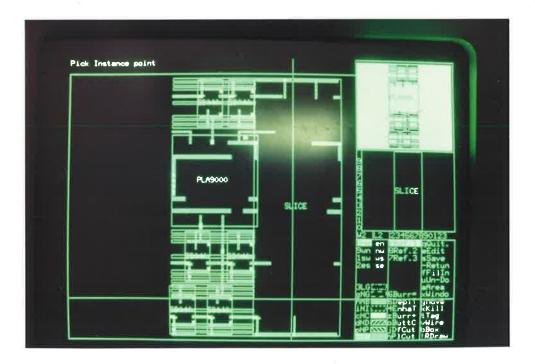

ET considers the hierarchical design problem exposed in PLAN and provides a solution to it. By restricting the designer to the same hierarchical design strategy (although a step backwards has been made by omitting the electrical connectivity information), and adding the feature of displaying mask level geometry to design rule penetration depth at the edges of the bounding boxes of composition cells, the design problems presented by PLAN are avoided (see Fig. 2.5).

#### 2.3.2 Further Analysis of Geometry Editors

The different hierarchical attributes of the various geometry editors are not the only differences between them<sup>[26]</sup>. KIC is an editor written in the programming language  $C^{[35]}$  to run under the **UNIX**<sup>†</sup> operating system and has been modified<sup>[36]</sup> to make it portable for use on a machine running the**VMS**<sup>‡</sup> operating system. PLAN was written in PASCAL, to run under VMS. ET was written in **VAX-11 C**<sup>‡</sup> to run under VMS, with the intention of making it portable to machines running UNIX.

The geometry manipulation functions provided by the different editors are

t UNIX is a Trademark of AT&T.

VMS and VAX-11 are trademarks of Digital Equipment Corp.

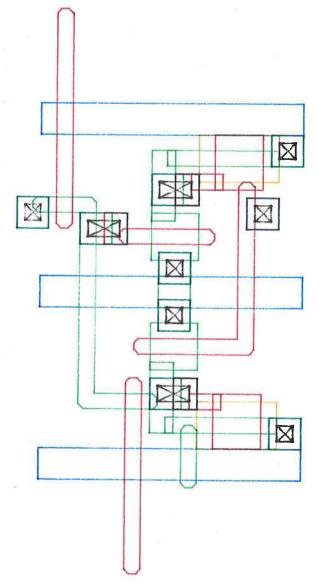

Figure 2.4: A PLAN view of the shift register cell in Fig. 2.1. This cell is shown at leaf cell level above and at composition level below. Note the hierarchical pin information that must be specified on the bounding box to enable connection between leaf cells at the time of composition, shown on the picture below. Note that at a particular level of composition PLAN allows only the hierarchical information to be seen, unlike KIC which allows a full EXPANsion of the composition level down to the leaf cell level.

Figure 2.5: Above, an ET view of a bit slice of AUSMPC 5/82, Project C4, displaying routing over sub-cells used in the composition of the cell. Below, two slices are composed alongside each other. One shows leaf cell information to Design Rule Penetration Depth, while the other is the same as that shown above. Notice the three viewports displaying design information, as opposed to two used by KIC. The largest is the working viewport, while the highlighted viewport displays the original cell that was called. The third viewport displays the cell to be used at composition time in its correct composition orientation.

similar, with KIC currently being the most versatile in this respect. This is not surprising as it is one of the oldest of the tools considered, was developed in conjunction with other research tools such as CAESAR and preceded others such as MAGIC<sup>[29,1]</sup>. For more comments on the Geometry Editing tool MAGIC, see the concluding section, section 2.8, of this chapter.

The main disadvantages of geometry editors relate to the problems of designing in mask level geometry. The problems in converting from electrical design to mask layouts requiring the adherence to geometrical design rules by the designer adds a step in normal design complexity. The hierarchical advances in such editors can only minimize the complexity involved in this conversion process, it does not rid the designer of the conversion problem.

| Comparison of Geometry<br>Editors KIC and ET |             |             |  |

|----------------------------------------------|-------------|-------------|--|

| Subject KIC ET                               |             |             |  |

| Technology Independence                      | Excellent   | Not Good    |  |

| Terminal Independence                        | Excellent   | Not Good    |  |

| Hierarchical Information                     | Fair        | Very Good   |  |

| Hierarchical Restrictions                    | None        | Good        |  |

| Language                                     | С           | C           |  |

| Operating Systems                            | VMS or UNIX | VMS or UNIX |  |

| Non Manhattan Geometries                     | Yes         | No          |  |

Table 2.1: A comparison of factors indicating the versatility of two Geometry Editors. Note that KIC is seen here as the more versatile of the two tools. However, it has been in existance and developed over much longer period. ET will be developed by ISD as PLAN2.

The advantages of these geometry editors are based on the ability of such tools to carry out the conversion from electrical design to mask level layout much more efficiently and quickly, in terms of design time, than Embedded Layout Languages. Geometry Editors demand much more computing resource than Layout Languages however. Table 2.1 above details some of the qualities of two of the editors discussed in this section on a comparitive basis. Section 2.4

Design Rule Checkers

## 2.4 Design Rule Checkers

Using low level layout tools as described previously in this chapter, the chance of an error occuring in the layout process causing a design rule violation is high<sup>[37]</sup>. If the circuit is to work, careful checking is mandatory<sup>[7]</sup>. Error checking programs embody the rules for a particular process and examine CIF files or PG tapes for violations, reporting each instance in terms of coordinates or patterns along with the nature of the violation. For MPC processes, the error checking tool must examine the CIF as a remote designer will not be concerned with PG tapes.

Design Rules (see Appendix B) typically assign minimum distances to dimensions of features, spacing between features in the same layer, and spacing between features in different layers. Design Rule Checking (DRC) programs ideally take the CIF description of the layout and provide some output indicating errors when and where they occur. There are a number of different approaches to design rule checking and an analysis and comparison of a number of different design rule checking programmes, Baker's DRC<sup>[37]</sup>, Noble's ADRIC<sup>[39]</sup>, Hartley's ROWAN<sup>[42]</sup> and ISD's CHECK<sup>[42]</sup>, will highlight these different approaches.

Baker's DRC uses a Raster Scan method, in which a small window is scanned across the design in raster fashion, and the contents in the window are checked for design rule violations. A  $4\lambda$  by  $4\lambda$  window is used as it was initially presumed that this was a large enough window to provide sufficient information to determine whether design rules had been violated. Baker does acknowledge however that this DRC produces false errors and a larger window, say  $10\lambda$  by  $10\lambda$  is needed to detect false errors arising from geometries that are close together, are separated, but are electrically connected. An example of such a situation can be seen in Fig. 2.6. Even the larger window modification will not always delete all such errors.

Apart from false errors, this DRC system has a number of other disadvantages. It is not very fast because it steps across every square of the design, even for large

The second

empty spaces. It has no hierarchical structure, the same error is reported every time it is encountered. Finally, the design rules for a particular manufacturing technology are intricately embodied in the program making this tool very inflexible with regard to technology change. It would be a major task to modify this program to accept a new set of design rules. Baker's DRC does accept non-manhattan geometries, but it approximates them in such a way that it makes certain width and spacing checks impossible to perform<sup>[39]</sup>. Baker's DRC was originally written in C under the UNIX operating system and transported to run under VMS.

Figure 2.6: The butting contact alongside the depletion mode transistor above, while connected to the transistor, can be seen as erroneous by Baker's DRC if the transistor to contact join falls outside the raster window.

#### 2.4.1 Hierarchical Design Rule Checking

Hierarchical design rule checkers exploit the hierarchy of a design by first checking leaf cells, then checking symbols which instance only leaf cells and CIF primitives, and subsequently repeating this process until the highest level of composition is reached.

ADRIC is an example of such a DRC. Apart from a different method to Baker's DRC, ADRIC also incorporates Hierarchical design rule checking based on the work done in Whitney's HDRC Algorithm<sup>[40]</sup>, although ADRIC, unlike HDRC was designed to accept CIF.

And the second se

The hierarchical philosophy used by ADRIC applies restraints on the designer at the layout stage. During each run, ADRIC will only check what has not been checked before unless a previously checked and validated symbol has been altered. ADRIC forces the designer to check each level of the hierarchy as it is completed. This is because it can only check those symbol definitions which exclusively instance previously validated symbols. If the designer runs ADRIC regularly, this causes no problems, otherwise the designer may find that several runs of ADRIC are necessary to reach the current level of composition. This restraint could be annoying unless it was to be implemented automatically at the time of composition.

The Polygon method of design rule checking used by ADRIC applies contraction and expansion to the features of the layout. These features are stored as polygons and if two of these polygons overlap when they are expanded by a certain amount, then they are too close together and a design rule is violated. This type of DRC operates by referring to a table indicating which features are to be expanded or contracted and by how much for each design rule for the technology. ADRIC is a much less technology dependent tool than Baker's DRC and together with its hierarchical analysis algorithm, implements some good concepts. However, it can be rather slow and consumes large amounts of storage space. Although ADRIC was never completed, it provided useful background research for ROWAN. ADRIC was written in PASCAL under the VMS operating system.

ROWAN is based on the DRC, LYRA<sup>[41]</sup>, which is written in LISP. The checking philosophy used by this tool is corner based. The rules are only checked at the corners of features on the layout because if a design rule is broken, then there must be a corner at which the violation either begins or ends, or both. This DRC is also hierarchical although the hierarchical philosophy of ROWAN is different to that of ADRIC. ROWAN will take a design at any level of composition and check for errors without having to iteratively run the checker for all unvalidated cells, at each level of the hierarchy. ROWAN takes advantage of the fact that CIF allows structured designs in which certain

ł

11

W

basic circuits can be defined as symbols, and then be incorporated in larger circuits by just calling the symbol. If the design is done like this in a repetitive fashion, a tree-like structure results.

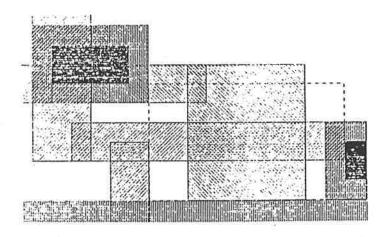

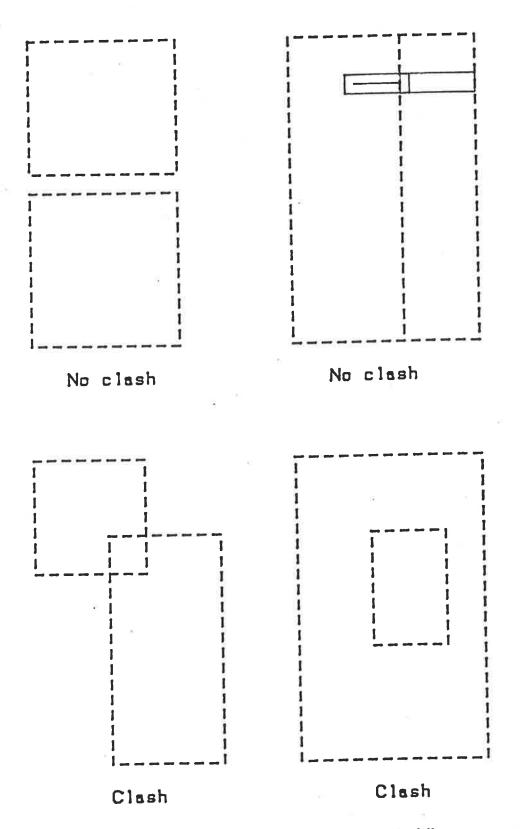

ROWAN exploits this structure to speed up the design rule checking and reduce the number of error reports made for the same error. ROWAN does this by using a bounding box concept similar to that used in PLAN for individual cells. This cell is checked once, when it is defined, and skipped when it is called later as long as no CIF primitives intrude within the bounding box. If CIF primitives do intrude within the bounding box, the cell will be checked.

If it is possible to skip a symbol when it is called, a thin boundary layer, similar to that appearing in ET, must still be checked for errors involving objects surrounding the symbol call. So if a symbol has been checked upon definition, then most of the data structure of that symbol may then be discarded, leaving just the boundary layer, which is then called as if it were the complete symbol. Certain layout restrictions are placed on the designer. To effectively use the hierarchical features of ROWAN, a designer must adhere to rules about the cell bounding box, see Fig. 2.7. If these rules are not obeyed, ROWAN cannot detect hierarchy and will check all cells which are intruded upon. The hierarchical features of ROWAN provide great speed increases, especially on sparse designs, as long as the designer conforms to the hierarchical layout restrictions.

#### 2.4.2 Technology Independent Design Rule Checking

Technology Independent Design Rule checking calls for increased input to the DRC Tool. ROWAN includes a separate PASCAL programme called a design rule compiler<sup>[42]</sup>. This programme takes a text file describing the design rules for a particular fabrication technology and produces a complete set of tables suitable for use by ROWAN. This file is called a *Technology File*. The language used for expressing the rules in this file is an embedded language and is actually a restricted list of PASCAL procedures. This feature of ROWAN has already been exploited to provide accurate checks of designs

Figure 2.7: Examples of ROWAN symbol interactions. The dashed lines represent the cell bounding boxes. If the cells clash, the hierarchical nature of the design is lost. Note that wires joining to a cell may have their half-width protrusions entering the cell bounding boxes without clashing.

under a number of different technologies at the University of Adelaide. These technologies are, the Mead and Conway nMOS technology, two Jet Propulsion Laboratory (JPL) CMOS technologies, and the Eshraghian and Weste<sup>[48]</sup> CMOS technology. These Technology Files contain an average of about 65 statements.

The obvious advantage of a Technology File means a new Design Rule Checker can simply be created within a few hours, for any technology using geometrical design layout rules. This feature alone makes ROWAN a very versatile tool, but considering its hierarchical checking algorithm, its efficient storage and speed of operation, it is considered to be an extremely flexible DRC. ROWAN is another tool that does not accept non-manhattan geometries.

Another DRC, CHECK<sup>[42.1]</sup>, is an extension of work done in ROWAN which makes it an even more versatile DRC. Like ROWAN, its checking is corner based, uses a technology file, but can either be run as an hierarchical checker like ROWAN, or as a non-hierarchical tile based DRC.

In its tile based mode of operation, a design is split into a number of square windows, ususally  $512\lambda$  square but with some flexibility to cater for small designs, which completely cover the design area. Each of the tiles making up the complete design are checked individually. As a result, any hierarchy involved in the design is lost at the tile partitioning stage. This method of analysis is used in CHECK as even modest sized IC designs require the use of more Virtual Memory than can currently be reasonably allocated to users on a multi-user computer. As a result, if CHECK were to be operated without its tiling feature, its algorithm would place severe restrictions on the size of circuits designed on multi-user systems.

Most designers find it difficult to confine themselves to the hierarchical design restrictions placed upon them by the DRC's ROWAN and CHECK for most efficient use of their hierarchical checking features. Non-hierarchical designs require very significant amounts of storage for checking using the hierarchical routines. The tile based approach

was implemented to avoid this problem.

An unusual feature of CHECK provides for the optimization of the input CIF code. This feature takes hierarchical CIF and flattens it, that is, it replaces CIF symbol calls with instantiated CIF. All overlapping geometries are also altered to form abutting geometries. This feature is intended to make plotting and Circuit Extraction (to be discussed in detail in the next section) more efficient.

## 2.4.3 Design Rule Checking Input and Output

As tools become more sophisticated they require and produce more information in an effort to make the use of such tools more *User Friendly*, a term often employed to indicate the ease of use of software or hardware for novice users.

The input to the DRC programmes of all of the DRC's discussed in this section is CIF, as is required for MPC prototyping. However, the tools ROWAN and CHECK also require the use of Technology Files. The Technology File input to these tools is done by the use of embedded languages similar to those used for design layout as discussed, except that these embedded languages are used for the purpose of creating a new design rule checker. The input is via a restricted set of PASCAL procedures. As an example, the procedure set for ROWAN is summarised as follows:- lambda, layers, layer, grow, rules, width, spacing, separation, extension, overhang, define, context, constraint and endrule. A sample technology input file may be seen in Appendix C. ADRIC also used an extra file which was used as an I/O file. It's purpose was to keep track of previously validated symbols to enforce ADRIC's unique method of hierarchical design rule checking.

The output from the various DRC's varies quite significantly depending on the tool. Baker's DRC provides a single output file, a .DRE Design Rule Error file. This file is often very large due to the fact that Baker's DRC reports the same error every time it is encountered. The output tends also to be cryptic and not particularly easy to follow. ADRIC produced two output files, the .VSS, Validated Symbol Skeletons

DRC Conclusions

file and the .DRE file. ADRIC need not be considered in any great depth owing to its incomplete state, yet its unique DRC algorithm necessitating the two file output is of interest. ROWAN produces a single output file, also called a .DRE file. The file reports errors as they occur, once only and also contains some user accounting information. CHECK produces very similar output to ROWAN.

## 2.4.4 DRC Conclusions

Many different types of Design Rule Checking programs are available for use under a range of operating systems. The latest make use of design hierarchy as well as technology file input to make the tools efficient and technology independent. It is interesting to note that hierarchical checking does not necessarily provide great advantages unless the designer uses an hierarchical design methodology. This is in most cases not a trivial task. The technology file notion does however provide great versatility by allowing the generation of an essential tool in a matter of hours instead of months.

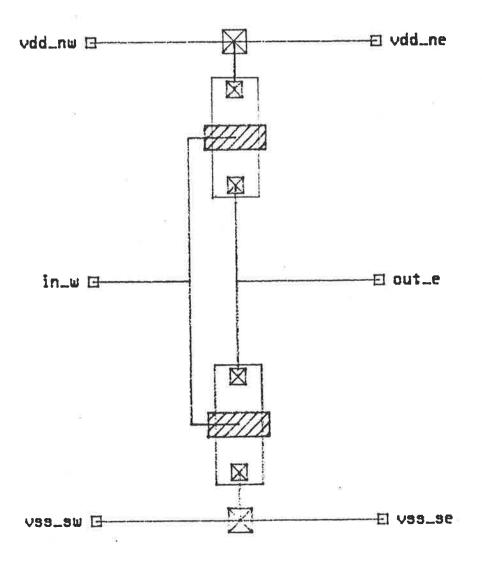

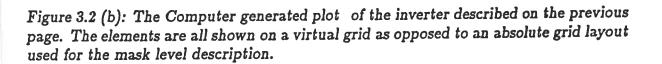

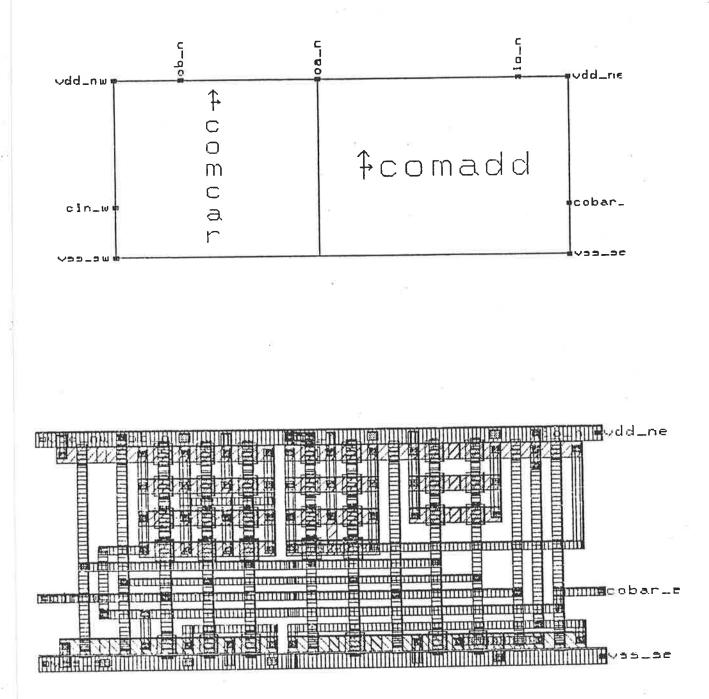

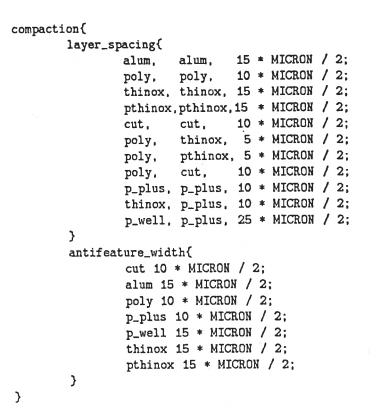

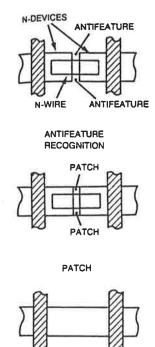

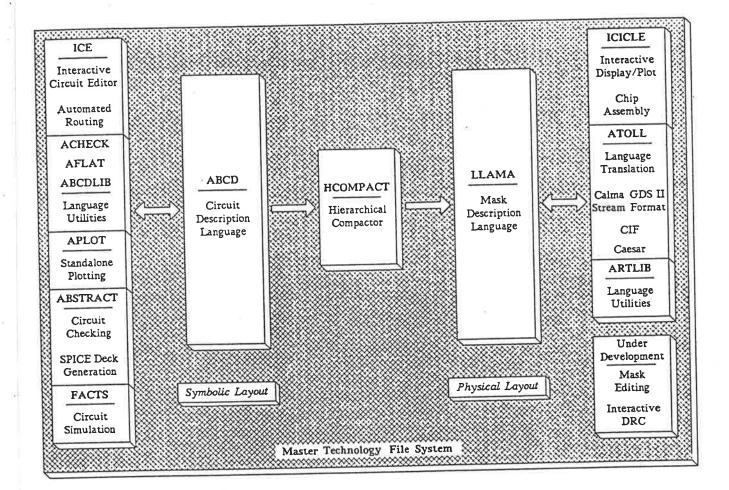

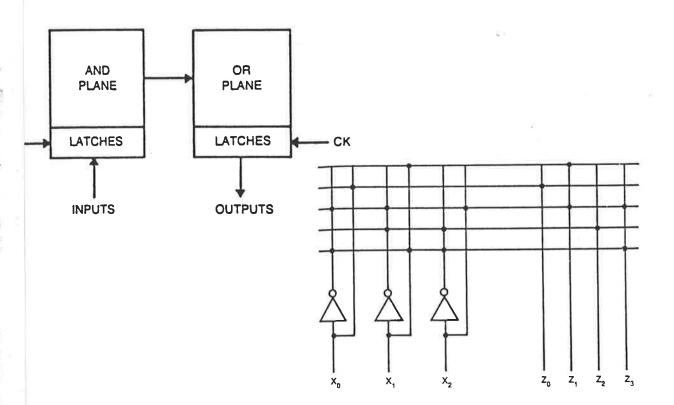

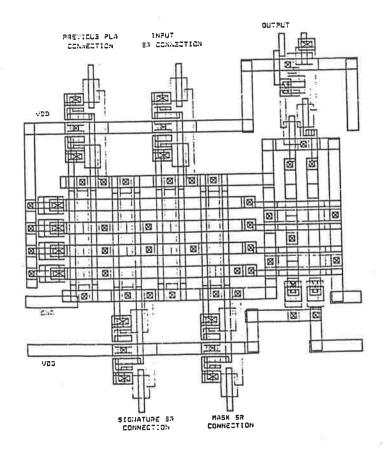

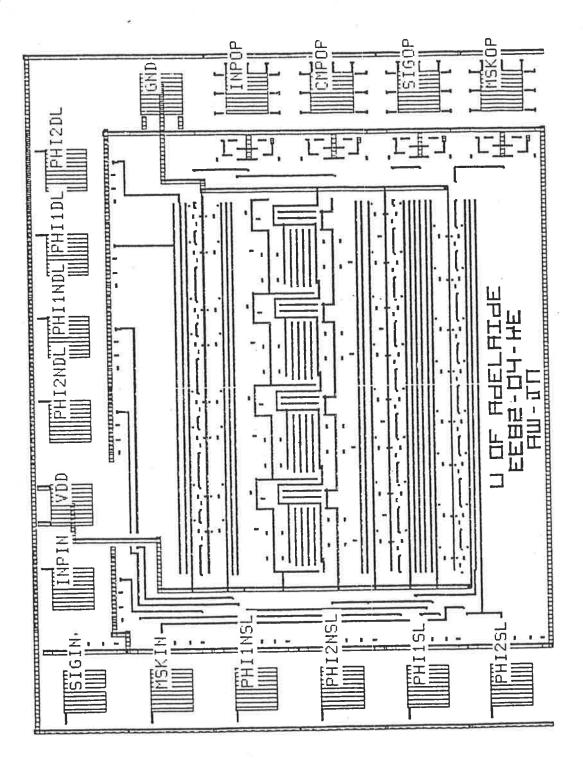

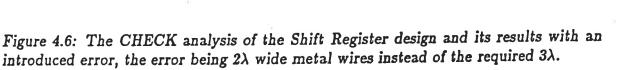

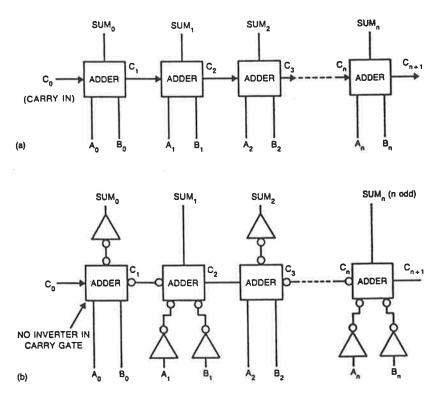

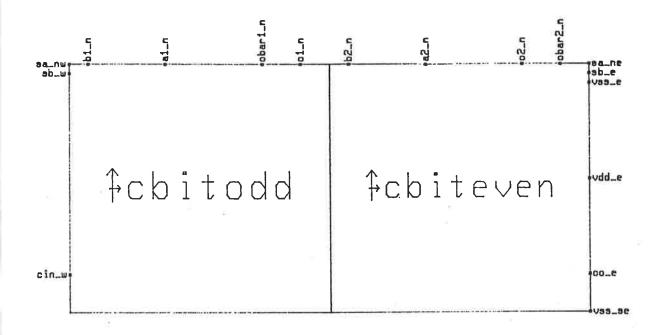

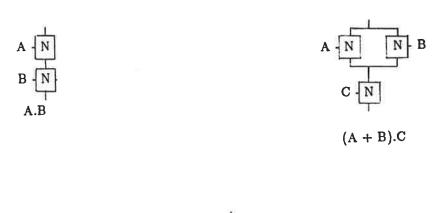

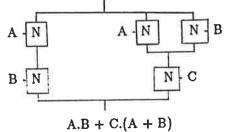

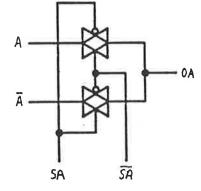

| Comparison of Design Rule<br>Checkers, ROWAN and CHECK |              |              |