# GaAs MESFET Photodetectors for Imaging Arrays

by

Derek Abbott, B.Sc. (Hons.)

Thesis submitted for the degree of

Doctor of Philosophy

The University of Adelaide Adelaide, South Australia

Department of Electrical and Electronic Engineering Faculty of Engineering

December 1995

## Contents

|   | Abs            | tract      | * # 35 # # # # 35 # # # # # |                           | 36), # 36                  | *0 19      | * *    | (#) ×                    | ::*() ¥ | 91 X     | 38 - | 5 2 3        | * *    | a as  | g 92 | 40   | ×     | viii  |

|---|----------------|------------|-----------------------------|---------------------------|----------------------------|------------|--------|--------------------------|---------|----------|------|--------------|--------|-------|------|------|-------|-------|

|   | Dec            | laratio    | n                           | (e) (e)                   | 190 <b>6</b> 3             | * * *      |        |                          | 140.4   |          | s 1  | 8 <b>3</b> 8 |        | 2 (2) |      | 8    | į     | X     |

|   | Pre            | face .     |                             | (00): (0)                 | 2 <b>0</b> 00 <b>x</b> 6 3 | +8:3•      | 36 X   | (36) S                   |         | a :      | 8 1  | 8 9 0        | a. s   |       |      | 8    |       | xi    |

|   | Ack            | nowle      | dgement                     | ( ) <b>*</b> ( ) <b>*</b> | 90 K S                     | ** **      | : x: x |                          |         |          | 2 4  |              | n u    |       |      | •    |       | xiii  |

|   | $\mathbf{Res}$ | ume .      |                             | ( (M)( ( M)               | an e s                     | - 1 av. 3a | 242.0  | 3 <b>-</b> 81 <b>-</b> 8 | ***     | (i i     | 4.5  | ,            |        |       |      |      |       | xviii |

|   | Pub            | olicatio   | ns                          | 0000 N                    | 31 K S                     |            | 980 B  | · ·                      | G. 1    | 4.       |      | 8 🖲 9        |        |       |      | ٠    | 9     | xix   |

|   | List           | of Fig     | ures                        | 10 <b>4</b> 0 <b>3</b> 4  | ac e s                     | - Tay 5    |        | 36 €                     |         | 94 a     | 2 13 |              |        |       |      | ٠    | •     | xxi   |

|   | List           | of Ta      | bles                        | - 000 ×                   | en e s                     | (   45 S4  | 5*6 %  | 30° ¥                    | 87 F    | - A¥ - 2 | . 1  | : Q 0        |        |       |      | ·    |       | xxvi  |

|   | Glo            | ssary      |                             | - 1965 W                  | 39 <b>- 9</b> 3 - 54       |            |        | 300 9                    | Se 2    | 94 4     |      | 0 2 3        | 1 1    |       | 8.8  | ٠    |       | xxix  |

| 1 | Intr           | oducti     | on                          |                           |                            |            |        |                          |         |          |      |              |        |       |      |      |       | 1     |

|   | 1.1            | Aims       | and Significance            |                           |                            |            |        |                          |         |          |      |              |        |       |      |      |       | 2     |

|   |                |            |                             |                           |                            |            |        |                          |         |          |      |              |        |       |      |      |       |       |

|   |                | 1.1.1      | Long Term Aim               |                           |                            |            | •      | ٠,                       | 9.      | 8 1      | 9 3  |              |        | ě ě.  |      | *    | 9 9   | 2     |

|   |                | 1.1.2      | Immediate Aim of            | this '                    | Worl                       | ι          | • •    | •                        |         |          |      |              | . 5    |       | e e  | 1.00 | t: :5 | 2     |

|   |                | 1.1.3      | State of the Art and        | d Pre                     | esent                      | Kn         | owl    | edge                     | e in    | the      | Ar   | ea c         | of C   | JaA:  | s A  | rra  | ıys   | 3     |

|   |                | 1.1.4      | Significance of GaA         | .s .                      |                            |            |        |                          | ٠.      |          |      |              |        |       |      |      |       | 5     |

|   | 1.2            | Overv      | ew of XY Array Str          | ategy                     | /                          |            |        |                          |         |          |      |              |        |       |      |      |       | 6     |

|   |                | 1.2.1      | Photocollection Mo          | des                       |                            |            |        |                          |         |          |      |              |        |       |      |      |       | 6     |

|   |                | 1.2.2      | Pixel Array                 | 1                         |                            |            | 191 X  | 9 ·                      | æ •5    | (¥ 0)€   |      |              |        | * *   | e ×  | 500  | * *   | 7     |

|   | 1.3            | Resear     | ch Philosophy               | · · · ·                   |                            | B•0 •      | 3C 8   |                          | 3• III  | * **     |      |              | · 1063 | * 14  | 15 W |      |       | 8     |

|   | 1 /            | T2: _1 J _ | .f +h:- D                   |                           |                            |            |        |                          |         |          |      |              |        |       |      |      |       | 1.0   |

|   | 1.5 | Achie  | evements from this Research               | 11 |

|---|-----|--------|-------------------------------------------|----|

|   | 1.6 | GaAs   | Background and Future Vision              | 11 |

|   | 1.7 | Sumn   | nary and Chapter Overview                 | 15 |

| 2 | Gaz | As ver | sus Silicon                               | 23 |

|   | 2.1 | Introd | duction                                   | 24 |

|   | 2.2 | Histor | ry                                        | 24 |

|   |     | 2.2.1  | Gallium                                   | 24 |

|   |     | 2.2.2  | Arsenic                                   | 25 |

|   |     | 2.2.3  | Gallium Arsenide                          | 25 |

|   | 2.3 | Comp   | eting Technologies                        | 26 |

|   |     | 2.3.1  | Diamond                                   | 26 |

|   |     | 2.3.2  | Silicon Carbide (SiC)                     | 29 |

|   |     | 2.3.3  | Gallium Nitride (GaN)                     | 30 |

|   |     | 2.3.4  | Polymer Electronics                       | 31 |

|   |     | 2.3.5  | Porous Silicon                            | 31 |

|   |     | 2.3.6  | Silicon-on-Insulator (SOI)                | 31 |

|   |     | 2.3.7  | Silicon-Germanium (SiGe) Heterostructures | 32 |

|   | 2.4 | The S  | emi-insulating (SI) GaAs Substrate        | 35 |

|   | 2.5 | GaAs   | Characteristics                           | 40 |

|   |     | 2.5.1  | Bandgap                                   | 40 |

|   |     | 2.5.2  | Speed                                     | 41 |

|   |     | 2.5.3  | Radiation Hardness                        | 42 |

|   |     | 2.5.4  | Dark Current                              | 42 |

|   |     | 2.5.5  | Absorption Coefficients                   | 43 |

|   |     | 2.5.6  | Atmospheric Bands                         | 48 |

|   |     | 2.5.7  | Quantum Efficiency Formulae               | 48 |

|   |     | 2.5.8  | Quantum Efficiency & Responsivity         | 50 |

|   |     | 2.5.9  | Spatial Degradation by Diffusion          |

|---|-----|--------|-------------------------------------------|

|   | 2.6 | Summ   | ary                                       |

| 3 | ME  | SFET   | Photodetection 6                          |

|   | 3.1 | GaAs   | MESFET Optical Model 6                    |

|   |     | 3.1.1  | Background                                |

|   |     | 3.1.2  | Photoresponse Model                       |

|   | 3.2 | GaAs   | MESFET Photoresponse Measurements         |

|   |     | 3.2.1  | Monochromator Measurements                |

|   |     | 3.2.2  | Laser Flood Measurements                  |

|   |     | 3.2.3  | Focussed Laser Measurements               |

|   |     |        | 3.2.3.1 Two Dimensional Laser Scan Set Up |

|   |     |        | 3.2.3.2 Two Dimensional Scan Results      |

|   |     |        | 3.2.3.3 Discussion                        |

|   |     |        | 3.2.3.4 Experimental Refinement           |

|   | 3.3 | Summ   | ary                                       |

| 4 | Noi | se     | 103                                       |

|   | 4.1 | Introd | uction                                    |

|   | 4.2 | A Brie | ef Early History of Noise                 |

|   | 4.3 | A New  | Derivation of the Thermal Noise Formula   |

|   |     | 4.3.1  | Overview of Methods in the Literature     |

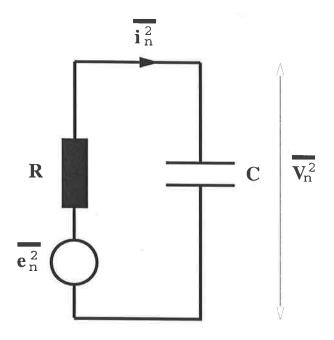

|   |     | 4.3.2  | The Lumped Model                          |

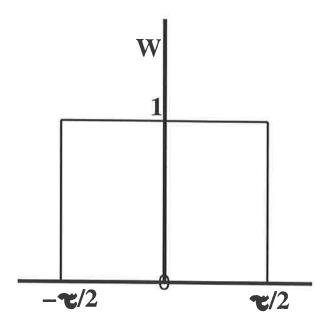

|   |     | 4.3.3  | The Windowed Fourier Transform (WFT)      |

|   |     | 4.3.4  | The Thermal Noise Formula                 |

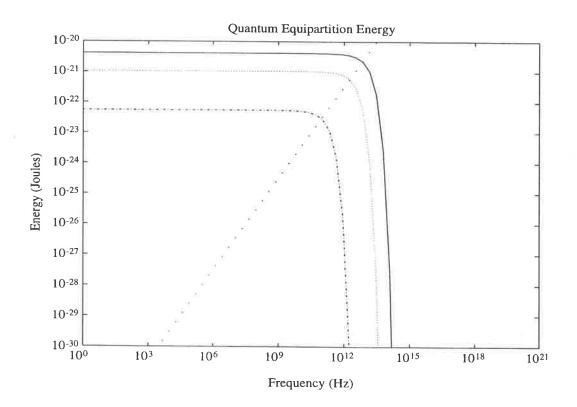

|   | 4.4 | The C  | lassical Energy Catastrophe               |

|   | 4.5 | The Q  | uantum Energy Catastrophe                 |

|   | 4.6 | The St | eak Grilling Debate                       |

| 4.7  | Quan     | tum Cut-Off Experimental Status   | 120 |

|------|----------|-----------------------------------|-----|

| 4.8  | MacD     | Oonald's Objection                | 122 |

| 4.9  | The (    | Case of Limiting R & C            | 122 |

| 4.10 | kTC      | Noise                             | 125 |

| 4.11 | Power    | r in a Matched Load               | 126 |

| 4.12 | 2 Distri | buted RC                          | 127 |

| 4.13 | The C    | Capacitor Paradox                 | 129 |

| 4.14 | Forwa    | ard's Photoamplifier              | 129 |

| 4.15 | Meası    | urement of Noise                  | 130 |

|      |          | mal Noise in MOSFETs              |     |

|      |          | er Noise in MOSFETs               |     |

|      |          | nal Noise in MESFETs              |     |

|      |          | er Noise in MESFETs               |     |

|      |          | Noise in MESFETs                  |     |

|      |          | Analysis of Imager Output Circuit |     |

|      |          | Silicon output circuit            |     |

|      |          | GaAs output circuit               |     |

| 4.22 |          | nary                              |     |

|      |          |                                   |     |

|      | igers    |                                   | 153 |

| 5.1  | Introd   | luction                           | 154 |

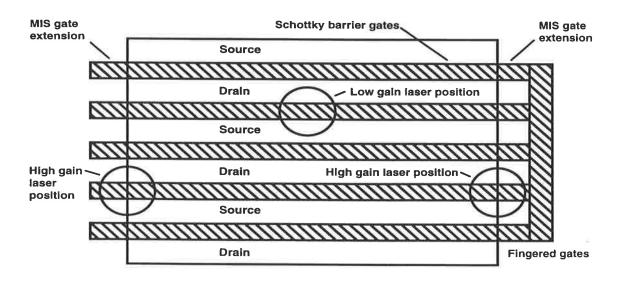

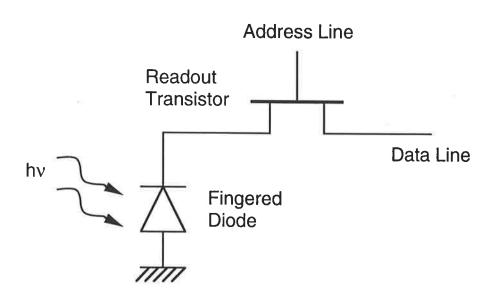

| 5.2  | Pixel 1  | Design                            | 154 |

|      | 5.2.1    | Illumination Modes                | 154 |

|      | 5.2.2    | Photocollection Modes             | 154 |

|      | 5.2.3    | Channel to Substrate Mode         | 156 |

|      | 5.2.4    | Gate to Channel Mode              | 158 |

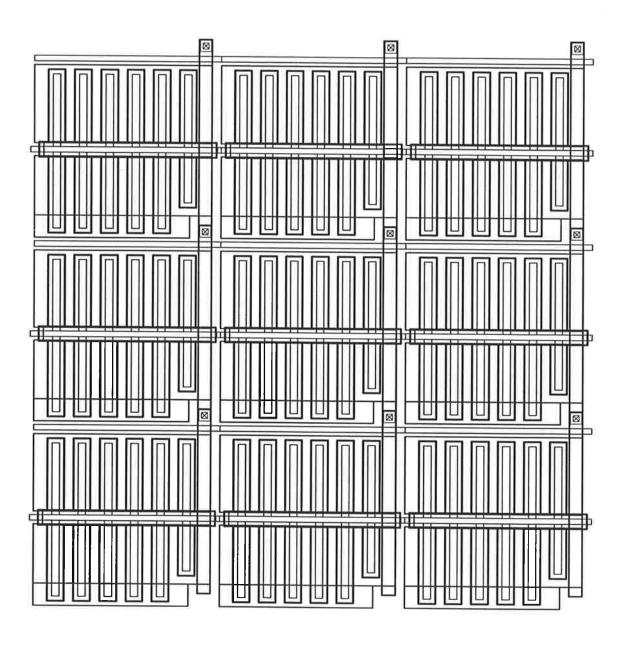

|      | 5.2.5    | Pixel Active Area                 | 159 |

|      | 5.2.6    | Pixel Design                      | 159 |

5

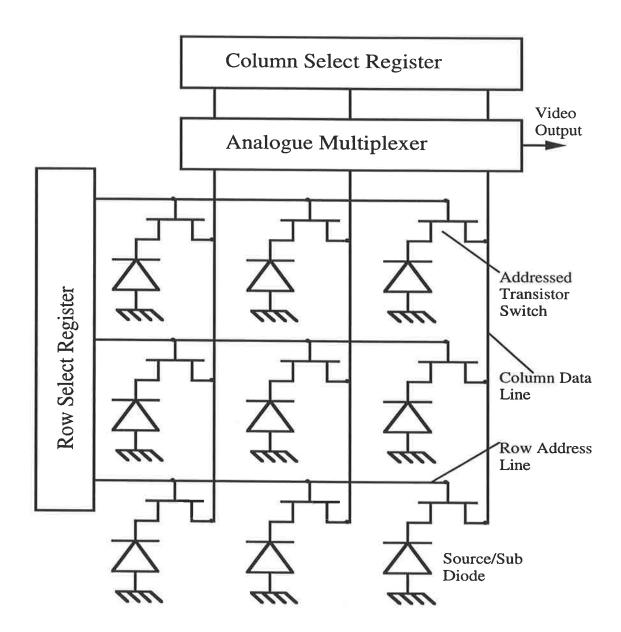

|   | 5.3  | Array      | Organisation                                             |

|---|------|------------|----------------------------------------------------------|

|   | 5.4  | Addre      | ss Circuitry                                             |

|   |      | 5.4.1      | Case 1: The Capacitively Bootstrapped Shift Register 169 |

|   |      | 5.4.2      | Case 2: Conventional D Flip-Flop Shift Register          |

|   |      | 5.4.3      | Case 3: Edge Triggered D Flip-Flop Shift Register        |

|   |      | 5.4.4      | Register Comparison                                      |

|   | 5.5  | Colum      | n-to-video line multiplexer                              |

|   | 5.6  | Summ       | ary                                                      |

| 6 | Des  | sign Me    | ethodology 181                                           |

|   | 6.1  |            | 101                                                      |

|   | 0.1  |            | uction                                                   |

|   |      | 6.1.1      | Technology                                               |

|   |      | 6.1.2      | Parasitic Oscillations                                   |

|   |      | 6.1.3      | Layout Approaches                                        |

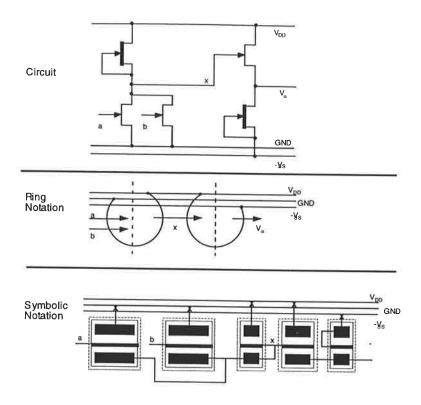

|   |      |            | 6.1.3.1 Symbolic mask level layout                       |

|   |      |            | 6.1.3.2 Practical constraints                            |

|   |      |            | 6.1.3.3 CAD tools                                        |

|   |      |            | 6.1.3.4 Modelling of gallium arsenide circuits 192       |

|   |      |            | 6.1.3.5 Interface to fabrication                         |

|   |      | 6.1.4      | Performance Study                                        |

|   |      |            | 6.1.4.1 Adders                                           |

|   |      |            | 6.1.4.2 Multipliers                                      |

|   | 6.2  | Summ       | ary                                                      |

| 7 | Visi | ons &      | Applications 207                                         |

|   | 7.1  | Introd     | action                                                   |

|   | 7.2  |            | : Aerospace paradigm                                     |

|   |      | 7.2.1      |                                                          |

|   |      | 1 . 44 . 1 | Image Processing                                         |

|     |        | 7.2.1.1    | Image registration                                   |

|-----|--------|------------|------------------------------------------------------|

|     |        | 7.2.1.2    | Image enhancement                                    |

|     | 7.2.2  | Polynom    | tial Evaluator                                       |

|     |        | 7.2.2.1    | Behavioural Model                                    |

|     |        | 7.2.2.2    | Algorithmic Solution                                 |

|     |        | 7.2.2.3    | Functional Specification                             |

|     |        | 7.2.2.4    | Structural Description (Floor Plan)                  |

|     |        | 7.2.2.5    | Symbolic Physical Description                        |

|     |        | 7.2.2.6    | Physical Layout                                      |

| 7.3 | Case 2 | 2: The Mo  | bile Multimedia Paradigm                             |

|     | 7.3.1  | Complen    | nentary Gallium Arsenide                             |

|     | 7.3.2  | Objective  | es                                                   |

|     | 7.3.3  | Current    | State-of-the-Art                                     |

|     | 7.3.4  | Sub-syste  | ems                                                  |

|     |        | 7.3.4.1    | High-density high-speed RAM                          |

|     |        | 7.3.4.2    | Image compression                                    |

|     |        | 7.3.4.3    | Modulo Multiplier for Data Encryption/Decryption 240 |

|     |        | 7.3.4.4    | Solid-state imager                                   |

|     |        | 7.3.4.5    | RF/digital interface                                 |

| 7.4 | Case 3 | : The Mo   | tion Detector Paradigm                               |

|     | 7.4.1  | Introduct  | tion                                                 |

|     | 7.4.2  | Comparis   | son with other approaches                            |

|     | 7.4.3  | Motion I   | Detector Chip                                        |

|     | 7.4.4  | Range Es   | etimation                                            |

|     |        | 7.4.4.1    | Gallium Arsenide Implementation                      |

| 7.5 | Case 4 | : The Spa  | tial Light Modulator Paradigm                        |

|     | 7.5.1  | Significan | nce                                                  |

|   |      |         | 7.5.1.1    | FLC/Si 7      | Technology  | у          | 9 V      | 8 %  | <b>3</b> 5 )    |        |            | Sel.          | 0.1     | •           |       |        | •           | . 259 |

|---|------|---------|------------|---------------|-------------|------------|----------|------|-----------------|--------|------------|---------------|---------|-------------|-------|--------|-------------|-------|

|   |      |         | 7.5.1.2    | GaAs Teo      | chnology .  |            | 2. 0     | ⊡ ⊛  | 8 <b>•</b> 0; ) |        | * *        | 300           | * *     | *0          | e 040 | * 0    | . <i>10</i> | . 260 |

|   |      |         | 7.5.1.3    | Devices       |             |            | 2.0      |      | e#U /           | * 2    |            | •             | n 0     | •           | * 780 | · 10   | • •         | . 261 |

|   |      |         | 7.5.1.4    | Optical N     | Neural Net  | work .     | 9 19     | ě    | •               |        |            | ē.            | 77 15   |             |       | A S    |             | . 263 |

|   | 7.6  | Techni  | iques and  | Methods       |             |            | s 0;     |      | e.              |        |            |               |         | •           | : (c) | 8.0    | į.          | . 264 |

|   |      | 7.6.1   | FLC/Si     | Devices .     |             |            | * 20     | · *  | (46) - Y        | 0.02   | ic a       | •             | ¥ 34    | 20          |       | 2 //   |             | . 264 |

|   |      | 7.6.2   | LED/Ga     | As and Fl     | LC/GaAs     | Devices    | S (# 10# | ≅ .€ |                 |        |            | <b>&gt;</b> C | * :*    | *           | # R#C | . ¥E S |             | . 266 |

|   |      | 7.6.3   | Smart P    | ixel Circui   | try         |            | œ 0*     | e .* | • 2             |        | <b>6</b> 9 | 31            | ** :*   |             |       | * 5    | (45         | . 266 |

|   |      | 7.6.4   | SLM and    | d ONN Te      | sting       |            |          |      | Ž,              |        |            |               |         | •           |       | 85 0   |             | . 266 |

|   | 7.7  | Summ    | ary        |               |             |            | 8 5      | a •  | •               |        | •          | 3             |         |             |       | . 8 3  | <b>(6)</b>  | . 267 |

| 8 | Con  | clusior | ns and R   | ecomme        | ndations    |            |          |      |                 |        |            |               |         |             |       |        |             | 277   |

| A | Fini | te Diff | ference N  | <b>Method</b> |             |            |          |      |                 |        |            |               |         |             |       |        |             | 283   |

|   | A.1  | FDM '   | Voltage P  | otential Sc   | olution     |            |          | 8    | ű.              | 5 S    | 0.0        | 17            | 2 2     | ٠           | * 31. | to 15  |             | . 284 |

|   | A.2  | FDM 1   | Electric F | ield Soluti   | on          | ear a a ra |          | F @  | 4               | 8.8    |            | ŝ             |         | •           |       | 1 3    |             | . 285 |

| В | Qua  | ntum 1  | Efficienc  | y             |             |            |          |      |                 |        |            |               |         |             |       |        |             | 289   |

|   | B.1  | Quanti  | um Efficie | ency in a S   | Semi-Infini | ite Slab   | • :      | 8 🖭  |                 | 58 18  | :::: ×     | ÷             | *E 3*   | 000         | * *   | *6.0*  | · •••       | . 290 |

|   | B.2  | Quanti  | um Efficie | ency in a F   | inite Slab  | ·          |          |      |                 |        |            | ez.           | 70 - 27 |             | * 8   | 8 8    | 3.53        | . 291 |

| C | Hea  | t Equa  | ıtions     |               |             |            |          |      |                 |        |            |               |         |             |       |        |             | 295   |

| D | Con  | iplex I | ntegrati   | on            |             |            |          |      |                 |        |            |               |         |             |       |        |             | 299   |

|   | D.1  | Genera  | ıl Comple  | x Integral    | for Capac   | citor Pr   | oble     | em   |                 |        | 90 R       | ×             |         | 260         | es se | DE - 0 | 14.5        | . 300 |

|   | D.2  | Noise A | Analysis c | of 2-Stage    | RC Ladde    | er         |          |      | e 1             | si .e. | x          |               | e: •    | <b>3•</b> 0 | e a   | oes o  |             | . 301 |

| E | Poly | nomia   | l Equati   | ons           |             |            |          |      |                 |        |            |               |         |             |       |        |             | 303   |

#### ABSTRACT

Is it possible for an XY addressable imaging array to be realised in standard or near-standard gallium arsenide digital IC technology? This was the original question at the heart of this work. The motivation was the ability to embed such an imager with digital GaAs processing on one IC chip. Integration of an imager with a processor offers the promise of smart sensors that exploit the excellent power-delay product of GaAs, useful for mobile applications – where, for instance, image compression may need to take place in real-time on the same chip. Compact mobile systems of the future can also exploit the mixed digital/RF capability of GaAs.

Measurements of the photoresponse of GaAs MESFETs are used to understand the photodetection mechanisms to aid future study and design. A significant new internal gain effect, in planar MESFETs has been discovered which we call the "photovoltaic self-biasing edge-effect." The edge-effect can be exploited to attain up to a factor of ten improvement in photosensitivity. In order to project further the advantages of GaAs and fully understand the challenges, the key differences in device physics between silicon and GaAs are critically examined.

Theoretical quantum efficiency calculations are carried out and compared against the photoresponse measurements. A new result is obtained showing that the quantum efficiency in a finite slab (which models an epitaxial layer) is equal to the quantum efficiency in a semi-infinite slab (which models a bulk substrate) plus a simple additive second order term.

A new optical technique for extracting semi-insulating (SI) substrate parameters, including the carrier diffusion length, is demonstrated showing diffusion lengths of an order of magnitude *lower* than in silicon. This is significant for improved spatial resolution in high definition television (HDTV) imagers. From the perspective of silicon device physics this is a surprising result, but is explained in terms of the deep levels in the GaAs SI substrate.

Various new pixel schemes and layouts are presented for the realisation of a GaAs XY addressable imaging array. A number of shift register designs for readout of the imager are

analysed, simulated and compared for the first time. Detailed calculations for optimising the noise performance of imager readout circuitry are developed and this is based on a detailed review of a number of conumdrums and surprises in noise theory.

Future visions and novel applications of the imager are carefully considered. A review of various image enhancement, image compression and image registration schemes are presented for possible future integration with the imager. Potential applications in mobile multimedia communications, artificial insect vision and spatial light modulators are reviewed.

The edge-effect discovery is shown to be particularly suited to producing increased photosensitivity in a smart sensor array based on insect vision.

In conclusion, a number of important new principles have been uncovered by this research leading to the potential realisation of a simple GaAs XY addressable imager that can be integrated with digital GaAs processing circuitry. This enables the 'smart sensor' paradigm to shift from silicon and reap the advantages of GaAs.

### **DECLARATION**

This work contains no material which has been accepted for the award of any other degree or diploma in any university or other tertiary institution and, to the best of the author's knowledge and belief, contains no material previously published or written by another person, except where due acknowledgement has been made in the text.

The author gives consent to this copy, when deposited in the University Library, being available for loan or photocopying.

Derek Abbott.

#### PREFACE

This work has an interesting history behind it giving rise to a thesis with a number of significant perspectives that are highlighted as follows.

Firstly, like many engineers today, the author originally came from a firmly entrenched silicon background, via working many years in industry, and thus originally approached the field of gallium arsenide with extreme skepticism. A change in belief took place, as concrete experimental results from this research gradually verified that GaAs is an excellent medium for imaging systems.

The initial research questions and challenges concerning a GaAs implementation are thus tackled and presented from the point of view of a 'silicon mind.' Interesting discoveries and surprises concerning GaAs device physics are viewed from a silicon perspective.

This work faced the interesting challenge that technology was not static over the duration of this research. The status quo was constantly changing throughout this research period. Due to the many unknowns in GaAs device physics, unknowns in substrate behaviour and immaturity of the technology, only a few years ago, the idea of a GaAs XY array imager was quite a courageous one. The known 'facts' at the time dictated that such an imager would not outperform silicon. However, the adopted attitude has been "what do we need to change to make it work?" The next question was "why should we expend the effort to do this?" The initial motivation was a vision that a simple GaAs XY array could be integrated with high speed image processing circuitry on the one chip, making making an ideal solution for mobile multimedia applications. This in itself was also a rather bold vision as mobile multimedia, in the telecommunications community then, was to our knowledge not spoken of and easy to contest based on the near-term foreseeable technology then.

Today, the understanding of the GaAs substrate has greatly improved, the maturity of the technology can support large VLSI designs, the research described in this work shows 'surprisingly' (from the silicon mindset) good prospects for GaAs XY arrays based both on theoretical analysis and actual experimental results. Furthermore, telecommunications

technology has matured to the point where concepts such as BISDN microcell networks are now within foreseeable reach and therefore the eventual realisation of a communications infrastructure required to support mobile multimedia is no longer a dream but now inevitable.

The philosophy employed in writing this thesis has been to communicate in a clear and non-obfuscating manner. As part of creating a clear presentation some special attention has been made to the history, vision and motivation that the work is built on. For clear understanding the "why" is as important as the "how."

In any pioneering research program, the meandering path is seldom straight. More often than not other discoveries are made along tangent paths, that can turn out to be more valuable than the original goals. This is the nature of true research. Therefore a number of these 'side alleys' have been carefully woven into the main fabric of this thesis – with hopefully minimal disturbance to the logical flow. The famous engineer Thévenin was surprised when he was told, just before his death, that his theorem had been accepted worldwide, some 43 years after he posed it in 1883. For this reason nothing has been prejudged.

Alexander Graham Bell once said "Leave the beaten track occasionally and dive into the woods. You will be certain to find something you have never seen before." This has been one of the principles underlying this work.

### **ACKNOWLEDGEMENTS**

I warmly thank my parents for their vision and sacrifice in providing an education for me. Also for the strong work ethic, they taught me by their example. They did not have the money to buy toys, so as a baby I was given old electrical plugs to play with. This early contact with electrical devices must have worked on my subconscious to bring me to this point today. Electricity was actually my worst physics subject at high school, so the plugs must be thanked for at least having a delayed effect on shaping my future.

I thank Dr. Percy Baxter and Dr. Denis Scotter for employing me at the GEC Hirst Research Centre, UK, which set me on the path of interest in electronic devices. They also awarded me a Bursary to help pay my way for obtaining my first degree. I would not be here today without their foresight.

At Hirst, David Burt was my mentor and generously guided me through many semiconductor principles. Ray Bell taught me the basics of electronics, how to use instruments and even how to solder. I thank them both for their patience and generosity. An important milestone, was at about the age of 19 when I asked the 'silly' question: "why do electric field lines stop existing outside a depletion region?" Stephen Lovatt provided the answer: "because field lines begin and end on fixed charges." The realisation of this simple fact, helped my understanding of device physics to suddenly blossom. I thank Stephen for providing the vital catalyst.

My mentors at Loughborough University, during undergraduate days, were Dr. Mike Brown and Nick Phillips. Mike Brown taught me how to look at solid state physics in simple ways and Nick Phillips sparked my curiosity in unsolved noise theory. These seeds, that were then implanted in my mind, have now grown and found expression within this thesis. Without their inspiration, this work would not be the same.

Moving to the present, I heartily thank my supervisors Prof. Kamran Eshraghian and Associate Prof. Bruce Davis for their guidance, patience and belief in me. Prof. Eshraghian has taught me so much through his tireless energy, loyalty and vision. He has been the rock upon which this work has been built, in terms of raising funding, springboarding

ideas and never prejudging a 'wild' idea. His belief in me and in the vision of the project, carried us through the early days when I could not see that far ahead. His boundless enthusiasm, deep belief in people & teamwork, willingness to encourage risks & taking them, devotion to long term thinking, ability to engineer & redefine reality, commitment to high expectations along with readiness, virtue and vision have been marks of his true leadership. Prof. Davis also has generously given of himself and has guided me through many mathematical concepts and has been an inspirational springboard for discussion of noise concepts.

There are many people that I must thank of their input into this work. Due to the obvious breadth of this thesis in contrast to my limited time & capabilities something has had to 'give.' Consequently, I kept myself totally 'software dumb' throughout this work. Michael Liebelt, Andrew Beaumont-Smith and Ali Moini have been extremely patient and generous by rescuing me from many software problems. The scan software for the Laser Prober turned out to be particularly tricky and although I originally wrote most of the code, Andrew must get the credit for making it work properly.

Dr. Don Griffin and Michael Needle must be thanked for the early work they did in getting the Laser Prober made up. A special thanks goes to Dr. Tony Pugatschew of the University of South Australia for arranging the laser unit to work through the microscope optics of the prober. Stephen Guest, Ian Linke and all the guys from the workshop did a marvellous job of constructing the antivibration table, for the prober, out of a granite gravestone, steel tubing and industrial vibration isolators. Thanks also to Geoff Pook for making up numerous PCB test heads for all my samples.

The Physics Department also generously lent me their monochrometer equipment for a year.

A special thanks is due to Dr. Eithne McCabe, Oxford University (now at Trinity, Dublin), for her support and encouragement with some of the early laser based measurements. She was the first of a long line of international visitors to witness the 'photovoltaic self-biasing edge-effect,' uncovered by this work.

I warmly thank Dr. Jerry Hallmark and Dr. Jon Abrokwah, of Motorola, for recently hosting me in Arizona and answering all my questions about their CGaAs HIGFETs. I would also like to thank Dr. Tim Coe, of Vitesse Semiconductor Corporation, for hosting me in Camarillo, California and also answering my questions.

Prof. Antonio Nuñez, Prof. Roberto Sarmiento and Dr. Jose Lopez have hosted me many times at the University of Las Palmas, Spain - their hospitality has been selfless and lavish. They have been a delight to work and collaborate with. Much of the credit for

Chapter 6 must be given to their team. I cannot praise them too highly.

Dr. Bruce Odekirk of Triquint Semiconductor generously spent a lot of his time unlocking some of the mysteries of the semi-insulating substrate for me. Much credit is owed to him for this very tricky area. Discussions with Prof. Doug S. McGregor, University of Michigan, Ann Arbor, and Prof. Robert B. Darling, University of Washington, Seattle, on this vexing subject have also been tremendously influential and helpful.

Dr. Bobby Yu of the University of Reading, UK, receives my deepest thanks for flying out to meet me both in Adelaide and Paris and has provided much of the inspiration for the Spatial Light Modulator (SLM) paradigm in Chapter 7.

Our Head of Department, Dr. Tony Parker must be thanked for his marvellous support, finding lab space and releasing me from teaching duties on many occasions for me to engage in international conferences and collaboration.

Dr. Neil Burgess has been a great springboard for discussions on the *mobile multimedia* concept and he has generously pointed me to some useful references on encryption and compression for which his inspiration must be given credit.

The assistance of Sam Mosel with the polynomial evaluator and Mrs. L. Gu with the background work on image processing & use of KHOROS is gratefully acknowledged. Much credit is due to their tireless help.

The following figures were put together by the following people and appeared in joint publications with myself: (1) Figs. 1.2 and 1.3, Andrew Beaumont-Smith, (2) Fig. 3.3, Song Cui (3) Figs. 7.27, 7.30 and 7.31, Dr. André Yakovleff and (4) Figs. 7.34, 7.35 and 7.36, Ali Moini.

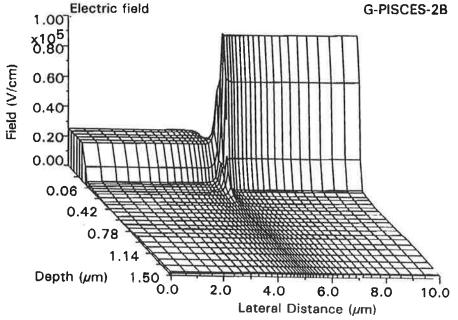

The photographs in Figs. 4.1 and 4.2 are by courtesy of AT&T Archives. Dr. Bob Anholt, of Gateway Modeling, Minnesota, kindly ran G-PISCES-2B for me, to produce Fig. 3.16. Clive Fuller kindly took the photograph in Fig. 3.12.

The section on insect vision would not be possible without the ingenuity and energy of the whole 'Bugeye' team: Ali Moini, Dr. André Yakovleff, Andrew Blanksby, Richard Beare, Ook Kim, Gyudong Kim, Thong Nguyen, Dr. Abdesselam Bouzerdoum, Prof. Adrian Horridge, Prof. Bob Bogner and Prof. Wonchan Kim.

Thanks are due to Dr. Murray W. Hamilton, University of Adelaide; Prof. B. L. Hu, University of Maryland; Prof. Laszlo B. Kiss, JATE, Hungary; Dr. Roger H. Koch, IBM Watson Research Center; Prof. Matt McIrvin, Harvard University; Prof. Tony Siegman, Stanford University for helpful discussions on ZPF.

A special thanks is due to Prof. Paul C. W. Davies, University of Adelaide, and Prof. Walter T. Grandy, Jr., University of Wyoming, who as leading experts in the field, kindly checked through my section on ZPF.

Also thanks is due to Dr. Andrew Mehnert, of Queensland University of Technology, for checking through this thesis and filtering out my errors.

Assistance with historical references from Hugh H. Wigg, Adelaide; Claudia Bruning, Fachhochschule Hamburg Fachbereich Bibliothek und Information; Dr. Jan W. Nienhuys, Eindhoven University of Technology; Prof. Gary A. Zimmerman, Antioch University, Seattle; Prof. Arthur van Rheenen, University of Minnesota, and Prof. Chapin C. Cutler, Stanford University is gratefully acknowledged.

Thanks is due to Ninette Ellis, Walter Foid and Chris Holshuysen for translation of papers from Dutch and German.

A special thanks to my wife, Stevie, for translating a number of papers from French. I warmly thank my wife, children and family for their support and coping with my long hours day & night away in the lab or grafted to a computer terminal. The true credit for this work belongs to them – and this work is dedicated to them.

A final thanks to my friends over the years for their support and encouragement. I have been particularly influenced by Peter & Helen McKenna, Bill & Brioney Smart, Bill & Jane Francis and especially Lyndon & Jenny Dolling who have taught me to always challenge the prevailing paradigm and to think without limits.

The initial funding for this work came from the Sir Ross & Sir Keith Smith <sup>1</sup> Foundation and credit is due to Prof. Sam Luxton who encouraged us to apply for this funding. Further funding then came from the Australian Research Council (ARC) and the Australian Department of Education Employment & Training (DEET) Targeted Institutional Links (TIL) program (in conjunction with Seoul National University, Korea) and the Australian Asean Educational Cooperative Program (AAECP).

<sup>&</sup>lt;sup>1</sup>Sir Ross & Sir Keith Smith were famous Australian aviators of the 1930s and the aerospace application overview in Chapter 7 is in their honour. An anecdote about Sir Ross & Sir Keith Smith can be found in Dale Carnegie's classic book on interpersonal relations.

Typesetting: This thesis has been generated using IAT<sub>E</sub>Xsoftware and graphical output is displayed using MATLAB. Processed images are via KHOROS. Numerous different drawing packages were used as departmental standards kept changing – regularising the postscript format generated from these different sources was a nightmare and was achieved with difficulty.

Spelling: The English spelling convention has been adopted, except for the words "programme" and "analogue" have been replaced by their American equivalents "program" and "analog." Where more than one spelling variant is allowed in English such as "biassing" or "biasing" and "infra-red" or "infrared," the option with the *fewest* characters has been adopted.

Quotations: At the beginning of each chapter, various quotes are displayed. The quotes are a mixture of pro and con. Contrary quotes are provided to reflect on the paradigm-shift in thinking. Some are tongue-in-cheek.

**Transistors:** Unless otherwise stated all, GaAs MESFET analysis, experimental results and discussion apply only to n-channel and non-self-aligned transistors on an SI GaAs:EL2 substrate with no p-buffer layer.

Mathematics: All mathematical results in this thesis have been carefully double checked using the MAPLE symbolic math editor. In some cases where this was not readily possible, MAPLE was used to numerically solve an equation and this was cross-checked for a number of specific examples with the by-hand analytical solution.

#### RESUME

Derek Abbott obtained his B.Sc. (HONS) in physics at Loughborough University of Technology, UK, and completed his PhD thesis in Electrical & Electronic Engineering at the University of Adelaide. He worked for a number of years at the GEC Hirst Research Centre, London, on infrared and visible image sensors - requiring discipline in VLSI design, optoelectronics, device physics, semiconductor noise, fabrication and testing. He has worked with both novel and standard technologies including nMOS, CMOS, CCD, SOS, GaAs and vacuum microelectronics (ie. field emission devices). Since his arrival in Australia, he worked for Austek Microsystems, Technology Park, and has been associated with the University of Adelaide since 1987 and is a Lecturer within the Department of Electrical Electronic Engineering. He has been an invited speaker at a number of international institutions and has appeared on national radio and television. He is a founder member of the Centre for Gallium Arsenide VLSI Technology, Adelaide, instituted in 1987. He has been consultant to various industry and defence organisations. His current research interests are in the areas of VLSI, GaAs, photodetectors, biologically inspired sensors, device physics and noise. His most recent contribution is the discovery of a new photovoltaic self-biasing internal gain effect within planar GaAs MESFETs. He is on international committees of both the SPIE, USA and UPoN, Hungary. He was an invited keynote speaker at the SPIE conference in Philadephia, 1995, and is an invited speaker for Unsolved Problems in Noise (UPoN '96) in Hungary. He has been invited to speak at a number of international institutions including: EPFL, Lausanne; University of Geneva; MIT, Cambridge; Los Alamos National Research Labs (LANL), New Mexico; Motorola, Tempe, Arizona; Seoul National University and the University of Las Palmas, Spain.

### **PUBLICATIONS**

- "Gallium Arsenide MESFET Imager," World Intellectual Property Organisation, International Bureau, Patent WO 93/07643, 15 April 1993. (with Eshraghian.)

- "Photovoltaic Gate Biasing Edge Effect in GaAs MESFETs," Electronics Letters, IEE, vol. 27, no. 21, Oct. 1991, pp. 1900-1991, (with Eshraghian, Cui & McCabe).

- "Derivation of the thermal noise formula using window limited Fourier transforms," *IEEE Trans Ed.*, vol. 39, no. 1, Feb. 1996, pp. 1-13.

- "An Introduction to Gallium Arsenide Devices," Proceedings of the Australian International Electronics Technology Conference, Adelaide, Oct. 1988, pp. 19-37.

- "Towards Ultra High Speed Systems," *Electronics '90*, Oct. 1990, pp. 193-202. (With A. Nunez.)

- "Conception of a Robot Eye Using a New Technology," ANZAAS, Microfilm, University of Sydney, Oct. 1991.

- "Ultra high speed gallium arsenide systems: design methodology, CAD tools and architectures," *Microelectronics Conf.*, Melbourne, June 1991, pp. 85-90.

- "An analog implementation of early visual processing in insects," *International Symposium on VLSI Technology, Systems, and Applications*, Taipei, pp. 283-287, May 12-14, 1993. (With Moini *et al.*)

- "An implementation of smart visual micro-sensor based upon insect vision," *Proc. 12th Aust. Micro. Conf.*, 5-8 Oct 1993, Gold Coast, Queensland, pp. 129-134. (With X.T. Nguyen *et al.*)

- "The stair-step tracking algorithm for velocity estimation," *Proc. 1st Australia & NZ Conf. on Intelligent Info. Sys.*, 1-3 Dec 1993, Perth, pp. 412-416. (With Moini *et al.*)

- "A new VLSI smart sensor for collision avoidance inspired by insect vision," *Proc. SPIE*, vol. 2344, 2-4 Nov 1994, Boston, pp. 105-115.

- "Biologically inspired obstacle avoidance a technology independent paradigm," *Proc. SPIE*, vol. 2591, Oct 1995, Philadelphia, pp. 2-10, Invited Keynote Paper.

- "VLSI implementation of an insect vision based motion detector chip," IEEE J. Sol. St. Circ., 1996. (With Moini et al, accepted.)

- Natural and Artificial Compound Eye Sensors, Ed. J. Sanders, SPIE Milestone Series, 1996. (With A. Yakovleff et al.)

- "Obstacle Avoidance and Motion-Induced Navigation," CAMP 95 Computer Architectures for Machine Perception Workshop, Como, Italy, pp. 384-393, 1995. (With A. Yakovleff.)

- "GaAs versus SiGe is there a challenge?" GAAS 96 European Gallium Arsenide and Related III-V Compounds Application Symposium, CNAM, Paris, 1996, pp. 4A1 ff.

- "Current gain mechanism in planar GaAs MESFETs due to new photovoltaic self-biasing effect," GAAS 96 European Gallium Arsenide and Related III-V Compounds Application Symposium, CNAM, Paris, 1996, pp. 3B3 ff.

- "Quantum vacuum fluctuations, zero point energy and the question of observable noise," *UPoN 96*, Szeged, Hungary, 1996, (Invited).

- "Is the thermal noise coefficient really 4?," UPoN 96, Szeged, Hungary, 1996, (accepted).

- "A new circuit theory paradox in the noise analysis of a 2-stage RC ladder," *UPoN 96*, Szeged, Hungary, 1996, (accepted).

- "Photovoltaic edge-effect in planar GaAs MESFETs," ICO-XVII, Taejon, Korea, 1996, (accepted).

# List of Figures

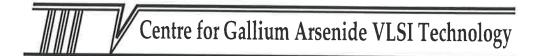

| 1.1  | Photonics versus electronics. The scope of this research is indicated in the shaded region                                                                     | 10         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

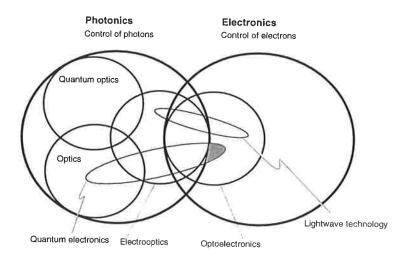

| 1.2  | Optical interconnects                                                                                                                                          | 13         |

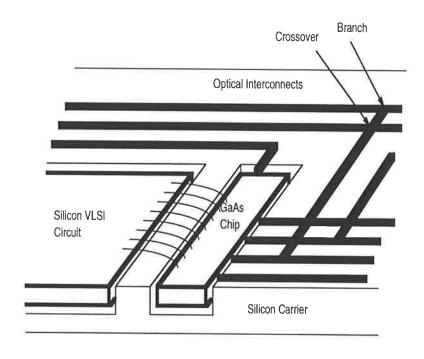

| 1.3  | Partitioning of high speed systems                                                                                                                             | 14         |

| 2.1  | Victor Moritz Goldschmidt                                                                                                                                      | 27         |

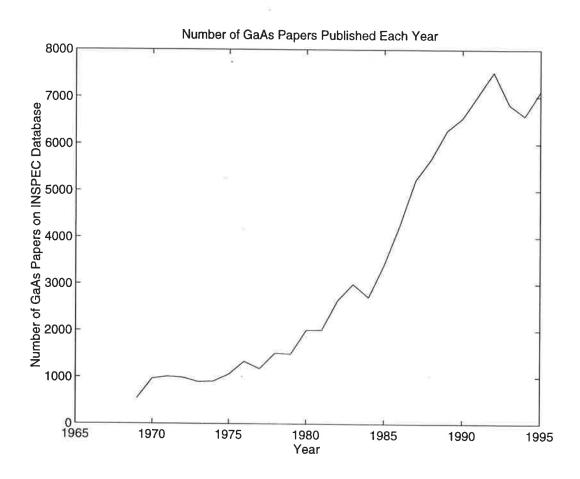

| 2.2  | Number of published GaAs papers on the INSPEC data base. Only the keywords 'GaAs' and 'gallium arsenide' were searched for.                                    | 28         |

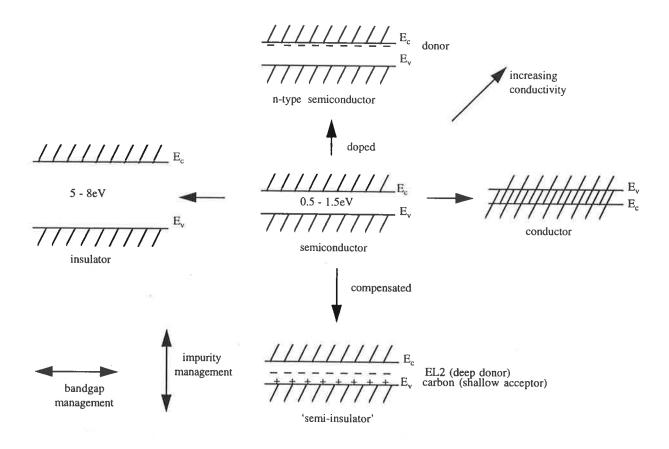

| 2.3  | Understanding the meaning of 'semi-insulator.'                                                                                                                 | 36         |

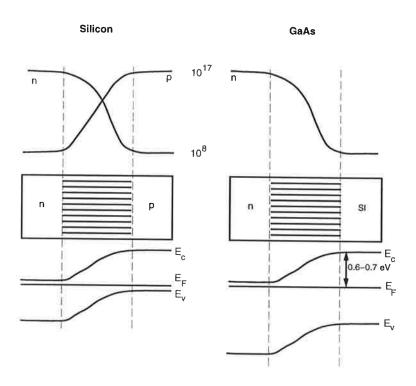

| 2.4  | Carrier concentration plots, electric field lines and band bending diagrams for a silicon pn junction an a GaAs hi-lo n/SI junction                            | 38         |

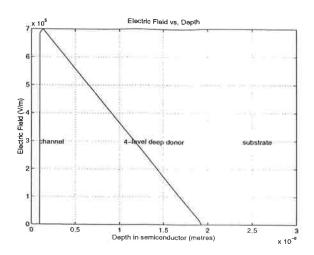

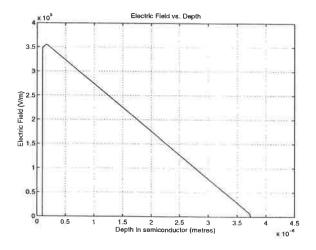

| 2.5  | Channel/substrate hi-lo junction field solved by FDM using the 4-level deep donor compensation model due to George et al                                       | 39         |

| 2.6  | Channel/substrate hi-lo junction field solved by FDM using the 2-level deep donor compensation model due to McGregor et al                                     | 39         |

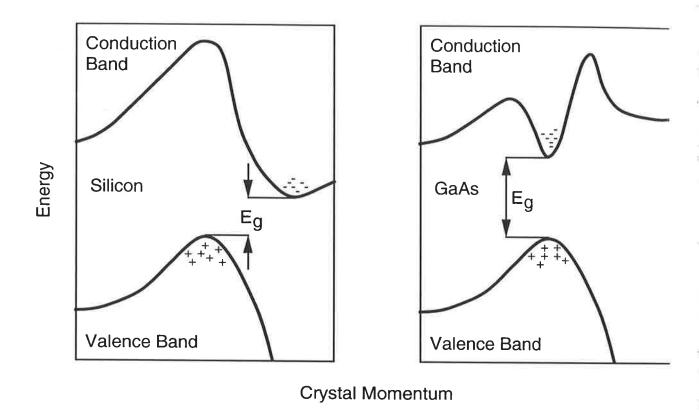

| 2.7  | Energy Band Structures of GaAs v. Si                                                                                                                           | 41         |

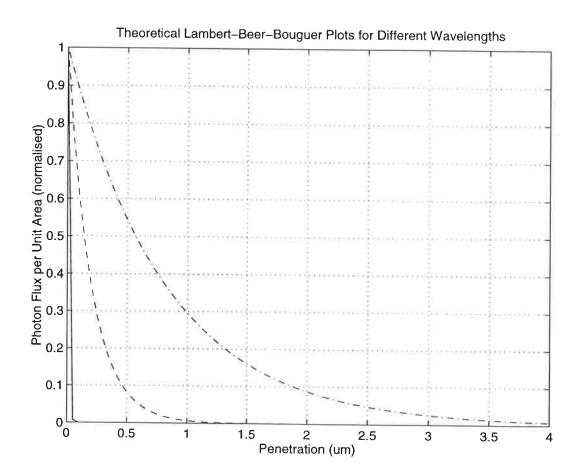

| 2.8  | Lambert's Law of Absorption for GaAs. Solid line: $\lambda=0.4~\mu\text{m}$ . Dashed line: $\lambda=0.6~\mu\text{m}$ . Chained line: $\lambda=0.8~\mu\text{m}$ | 44         |

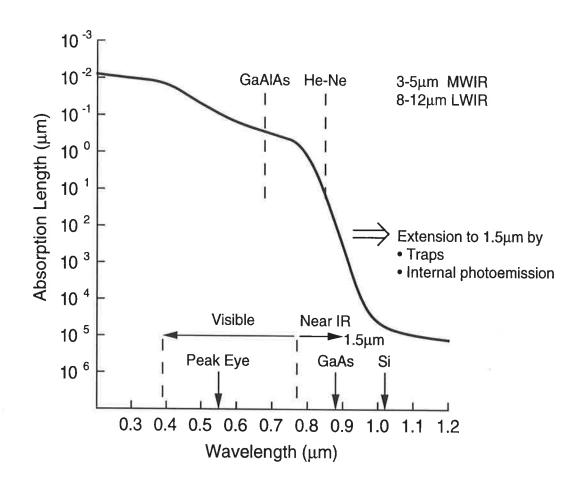

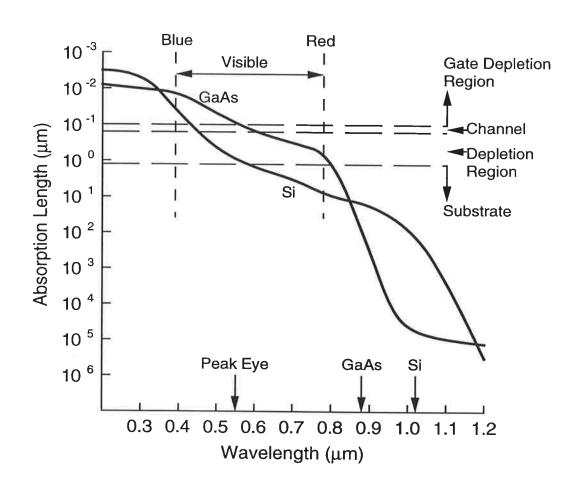

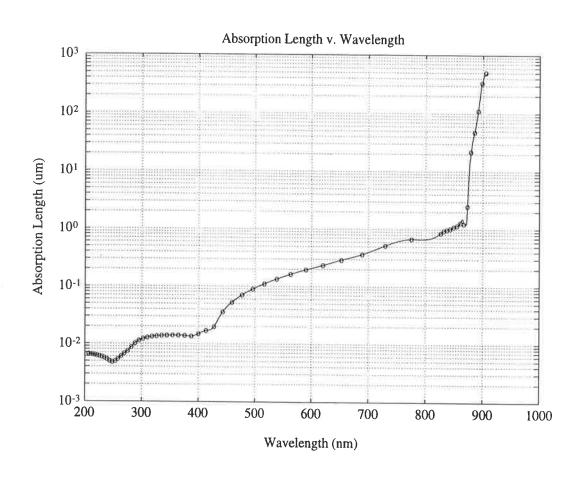

| 2.9  | GaAs Absorption Length Dependence on Wavelength                                                                                                                | 45         |

| 2.10 | GaAs v. Si Absorption Length Comparison                                                                                                                        | 46         |

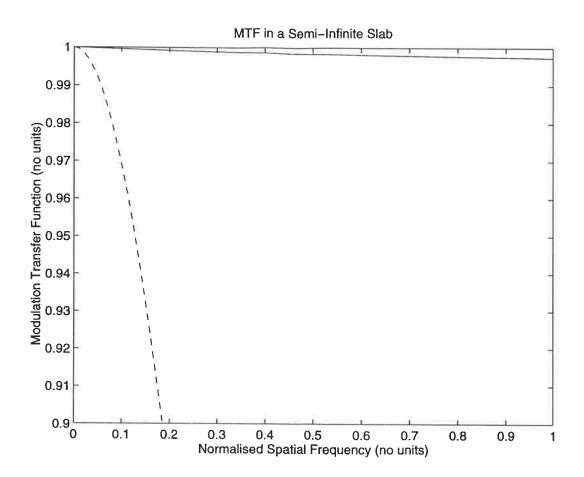

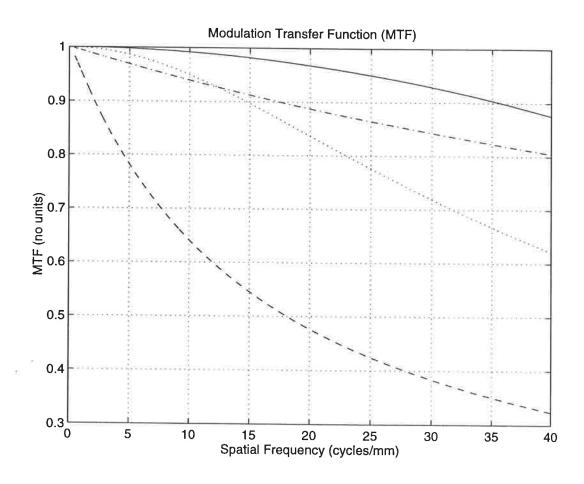

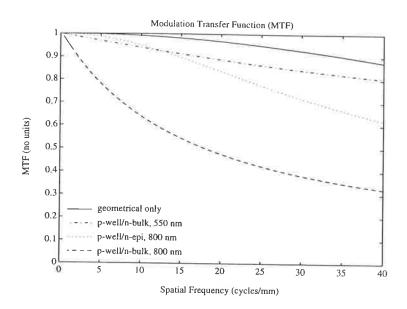

| 2.11 | MTF due to diffusion. A comparison of the traditional formula due to Seib (dashed line) and the formula due to Barbe (solid line)                              | 51         |

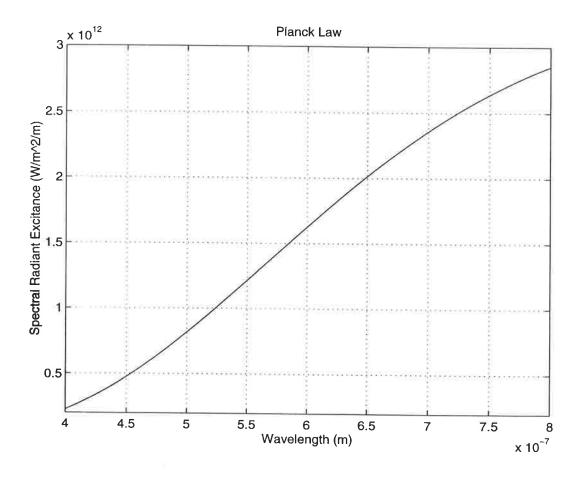

| 2.12 | Planck's law                                                                                                                                                   | <b>E</b> 9 |

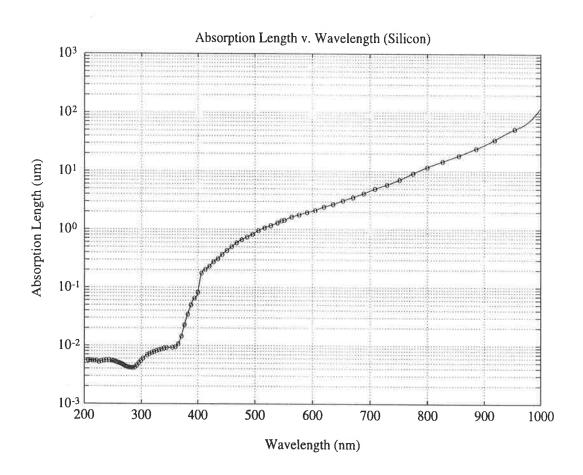

| ۷.1 | o measured absorption length against wavelength for silicon                                                                                                                                                                                                                        | 53 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | 4 Measured absorption length against wavelength for GaAs                                                                                                                                                                                                                           | 54 |

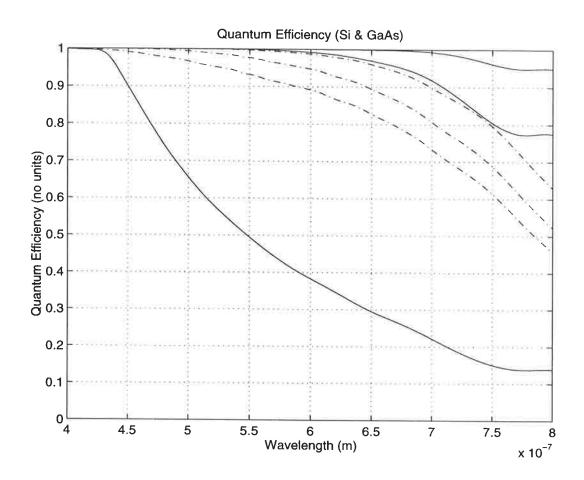

| 2.1 | 5 Internal quantum efficiency v. wavelength                                                                                                                                                                                                                                        | 55 |

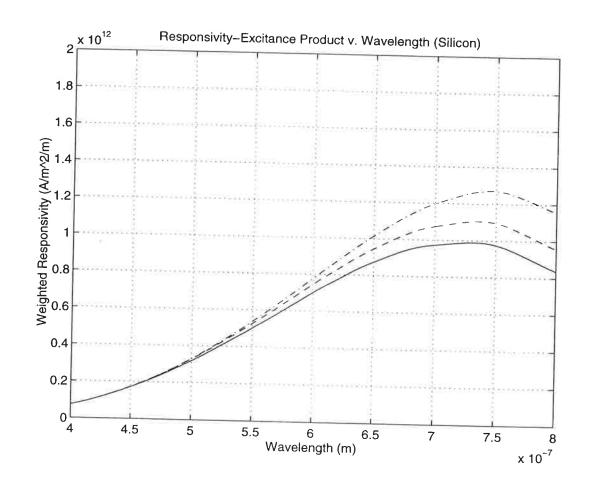

| 2.1 | 6 Weighted responsivity versus wavelength for silicon. Solid line, $W=0.5~\mu\mathrm{m}$ . Dashed line, $W=2~\mu\mathrm{m}$ . Chained line, $W=5~\mu\mathrm{m}$                                                                                                                    | 56 |

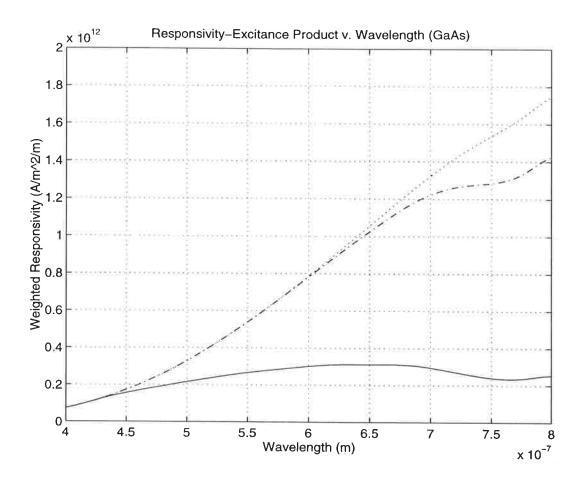

| 2.1 | 7 Weighted responsivity versus wavelength for GaAs                                                                                                                                                                                                                                 | 57 |

| 2.1 | 8 Theoretical MTF versus spatial frequency. Diffusion-only curves are: Si bulk, 550 nm (chained line); Si epi, 800 nm (dotted line); Si bulk, 800 nm (dashed line). Geometrical-only curve is for a 7/20 aperture to pitch ratio and the GaAs case matches this curve (solid line) | 59 |

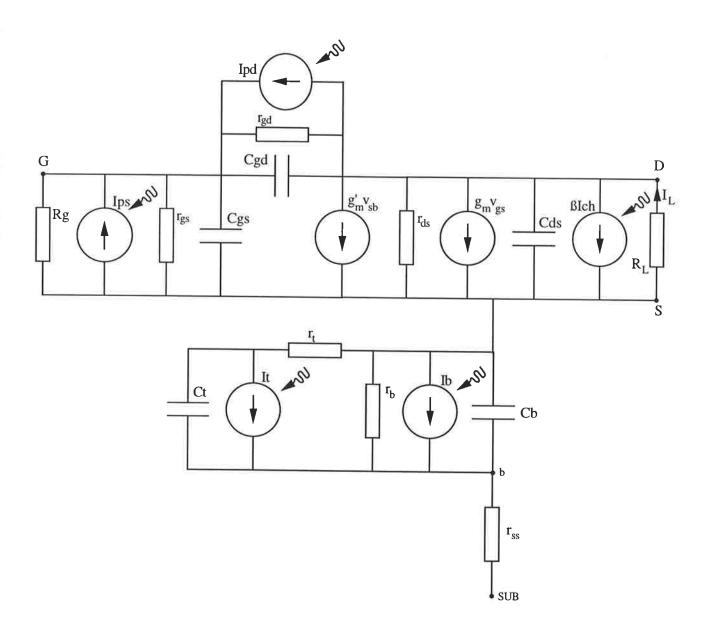

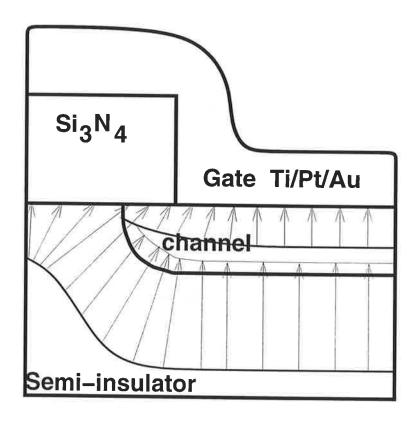

| 3.1 | Equivalent circuit of MESFET showing photoresponsive elements                                                                                                                                                                                                                      | 70 |

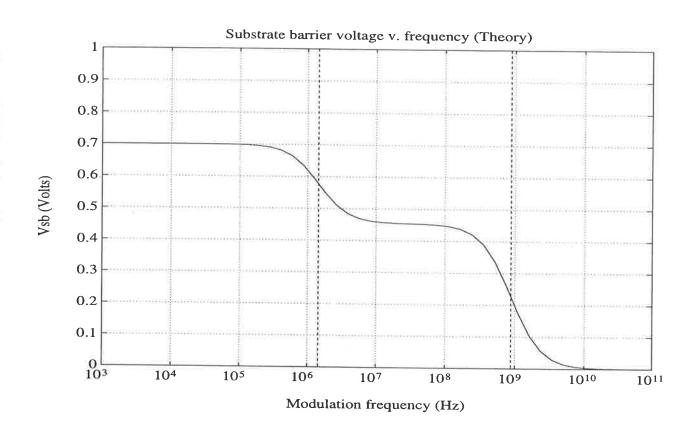

| 3.2 | Voltage across channel/substrate barrier against laser modulation frequency. The vertical dashed lines show the approximated time constant positions.                                                                                                                              | 74 |

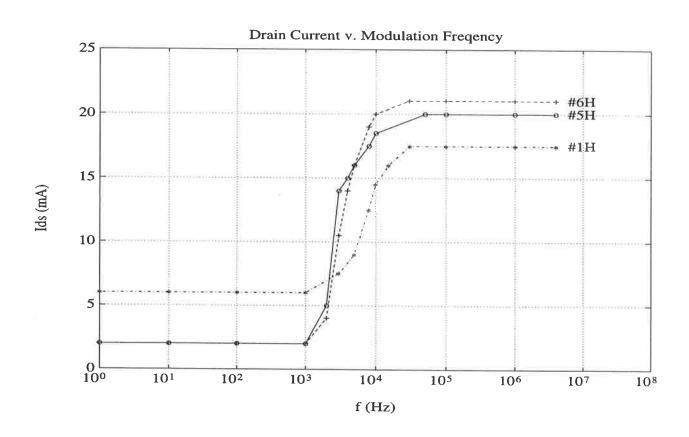

| 3.3 | Drain current versus laser modulation frequency. Three curves represent three separate devices                                                                                                                                                                                     | 75 |

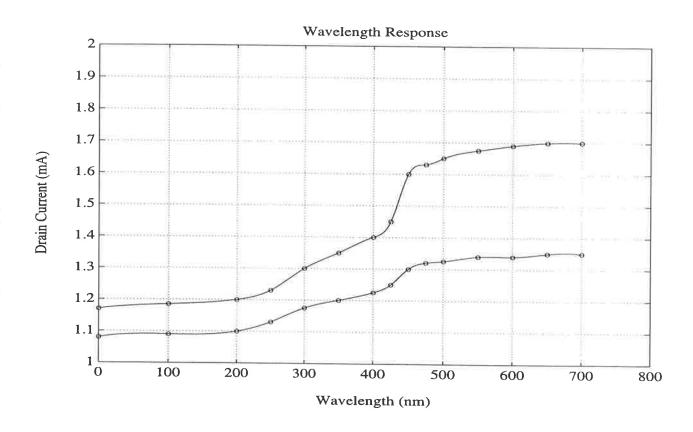

| 3.4 | Wavelength response using xenon source monochromator, $V_{gs}$ =-0.8 V, $V_{ds}$ =0.6 V. Dual curve represents the looping effect                                                                                                                                                  | 76 |

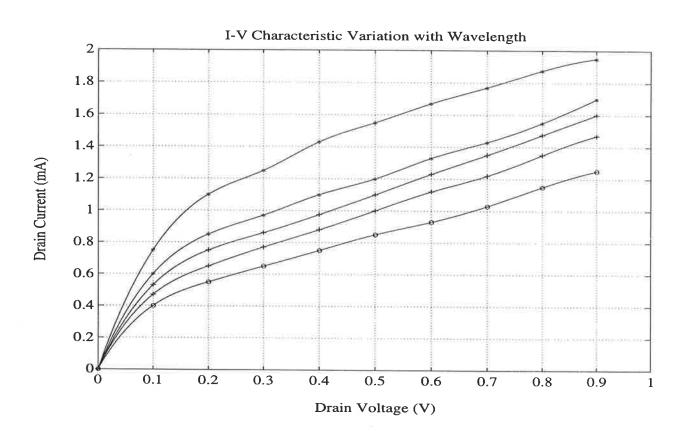

| 3.5 | I-V Characteristic variation using xenon source monochromator, $V_{gs}$ =-0.8 V, '*'=700 nm, '+'=300 nm, 'o'=0 nm (dark). Dual curves represent the looping effect. There is no looping in the dark condition.                                                                     | 77 |

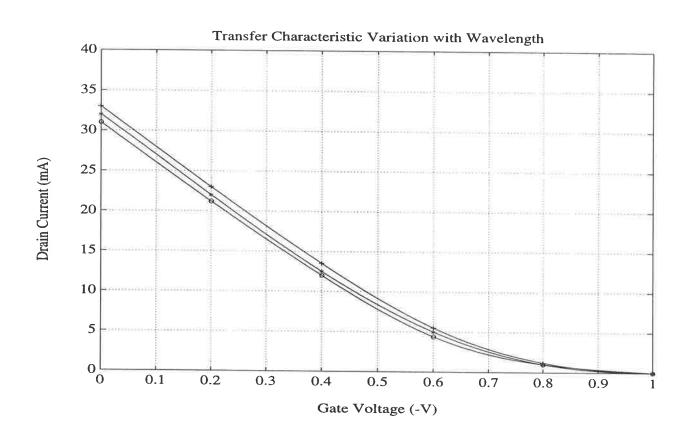

| 3.6 | Transfer characteristic variation using xenon source monochromator. $V_{ds}$ =0.6 V, '+'=700 nm, '*'=400 nm, 'o'=200 nm                                                                                                                                                            | 79 |

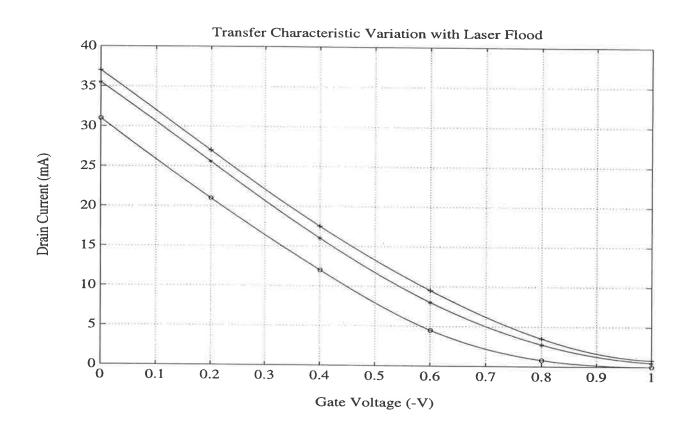

| 3.7 | Transfer characteristic variation using laser flood. $V_{ds}=0.6 \text{ V}$ , '+'=815 nm @ 3 mW, '*'=632 nm @ 0.95 mw, 'o'=0 nm (dark)                                                                                                                                             | 80 |

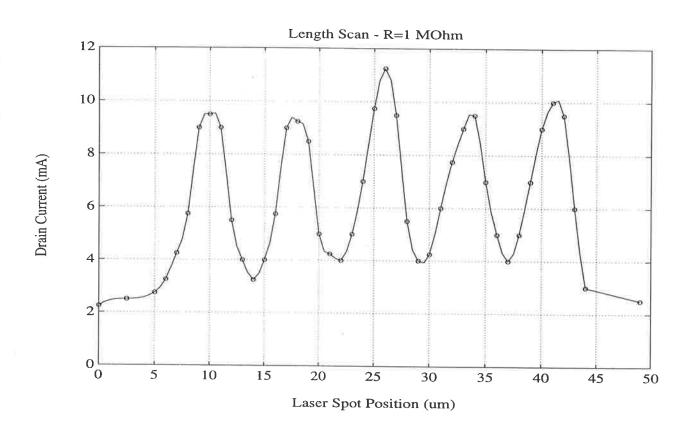

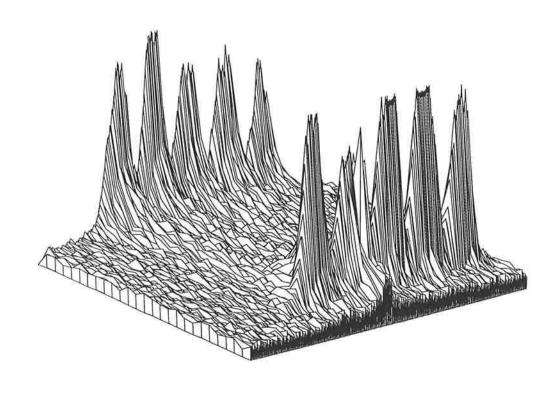

| 3.8 | Transistor length scan with focussed laser, 678 nm @ 0.125 mW, 2 $\mu$ m diameter spot size. 1 M $\Omega$ series gate resistor. $V_{gs}$ =-0.8 V, $V_{ds}$ =0. 6V                                                                                                                  | 82 |

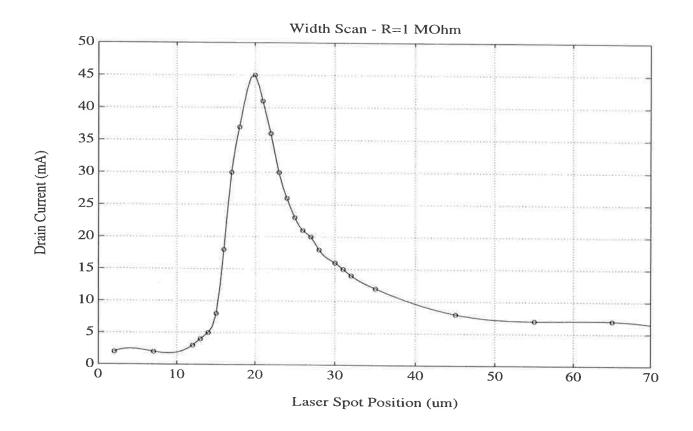

| 3.9 | Transistor width scan with focussed laser, 678 nm @ 0.125 mW, 2 $\mu$ m diameter spot size. 1 M $\Omega$ series gate resistor. $V_{gs}$ =-0.8 V, $V_{ds}$ =0.6 V. Transistor edge corresponds to 20 $\mu$ m on the x-axis                                                          | 83 |

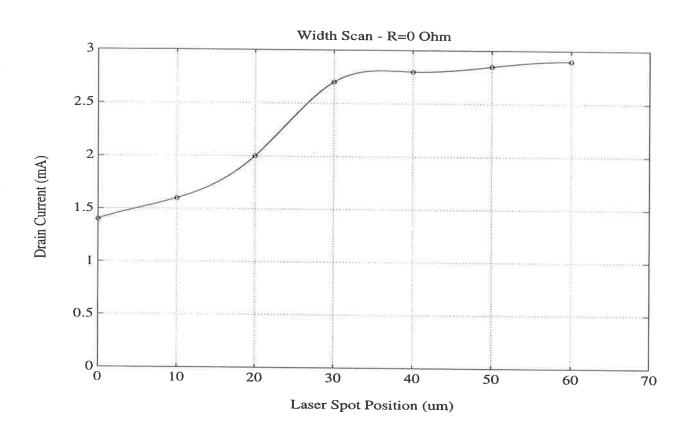

| 3.10 | eter spot size. No series gate resistor. $V_{gs}$ =-0.8 V, $V_{ds}$ =0.6 V. Transistor edge corresponds to 20 $\mu$ m on the x-axis                                                                            | 84 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

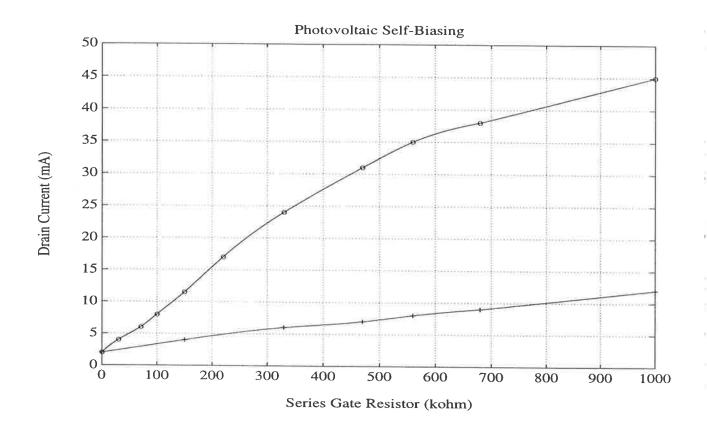

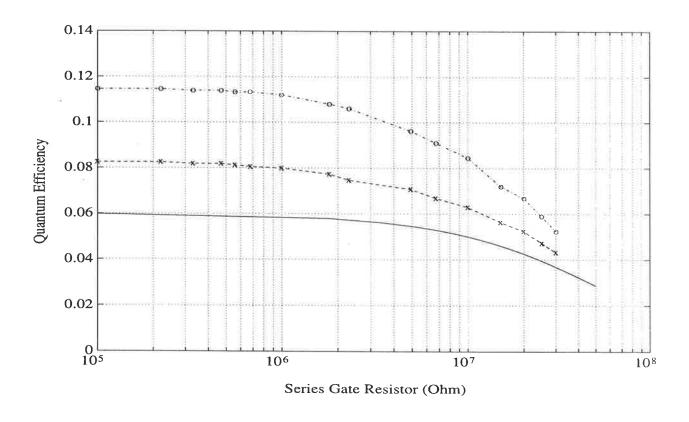

| 3.11 | Response against gate series resistor. 678 nm @ 0.125 mW, 2 $\mu$ m diameter laser spot size. 1 M $\Omega$ series gate resistor. $V_{gs}$ =-0.8 V, $V_{ds}$ =0.5 V, 'o'=transistor edge, '+'=transistor middle |    |

| 3.12 | Laser Prober with Computerised X-Y Platform                                                                                                                                                                    | 87 |

| 3.13 |                                                                                                                                                                                                                |    |

| 3.14 |                                                                                                                                                                                                                |    |

| 3.15 |                                                                                                                                                                                                                |    |

| 3.16 | 3-D Electric field plot using G-PISCES-2B with Spicer's UDM. Left half is                                                                                                                                      | 91 |

| 3.17 | Convergence of Schottky gate, MIS gate and channel/substrate field lines at the transistor edge. Conceptual drawing with exaggerated features                                                                  | 92 |

| 3.18 | Quantum efficiency versus gate resistor. Solid line: internal quantum efficiency (T=1) from first order theory. Dashed line: measured (low gain).  Chained line: measured (high gain)                          | 93 |

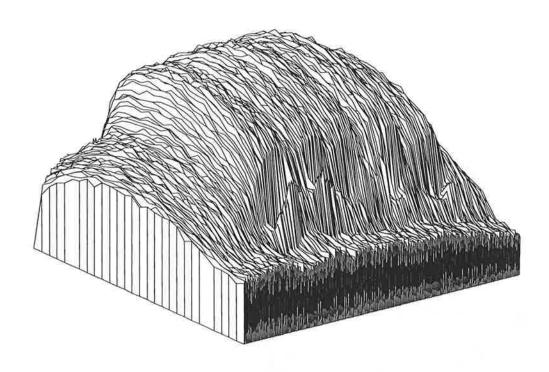

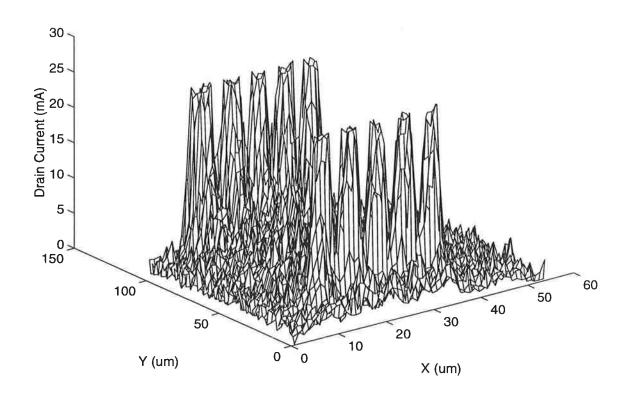

| 3.19 | MESFET drain current response to 2-D laser scan, max. current 29 mA. With 10 M $\Omega$ gate resistor. 3-D plot. Performed on antivibration table                                                              | 95 |

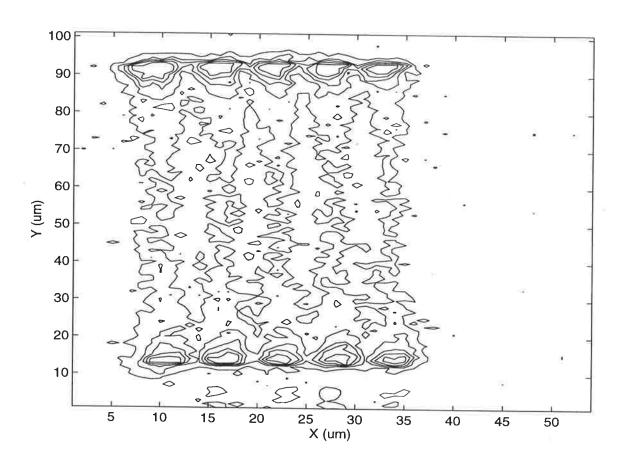

| 3.20 | MESFET drain current response to 2-D laser scan, max. current 29 mA. With 10 M $\Omega$ gate resistor. Contour plot. Performed on antivibration table.                                                         | 96 |

| 4.1  | Bert Johnson                                                                                                                                                                                                   | )6 |

| 4.2  | Harry Nyquist                                                                                                                                                                                                  |    |

| 4.3  | Lumped Circuit Model                                                                                                                                                                                           |    |

| 4.4  | The window function                                                                                                                                                                                            | .3 |

| 4.5  | Quantum equipartition energy                                                                                                                                                                                   | 21 |

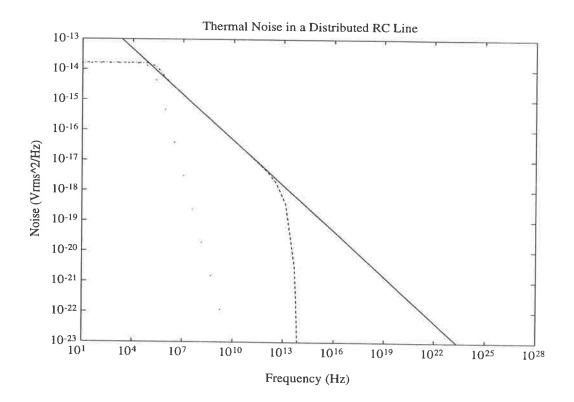

| 4.6  | Noise in distributed RC line                                                                                                                                                                                   |    |

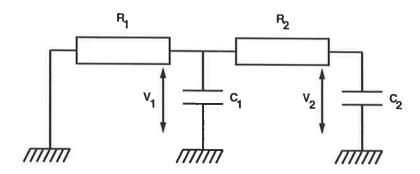

| 4.7  | Two stage RC ladder – a source of an unsolved paradox                                                                                                                                                          | 29 |

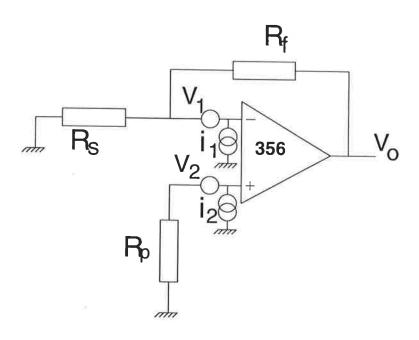

| 4.8  | Amplifier configuration                                                                                                                                                    | 0  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Opamp noise sources                                                                                                                                                        | 1  |

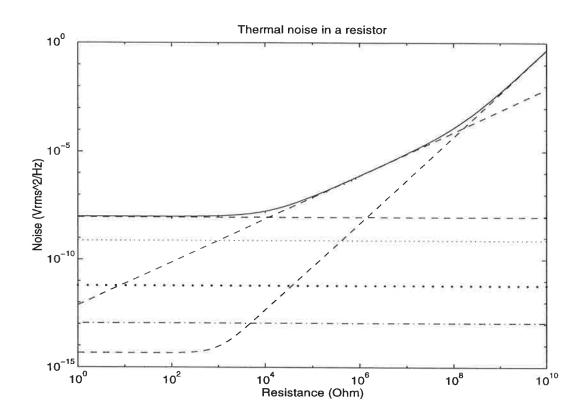

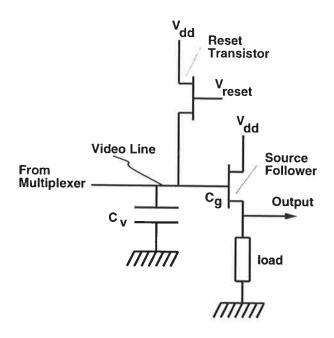

| 4.10 | Imager output circuit configuration                                                                                                                                        | 18 |

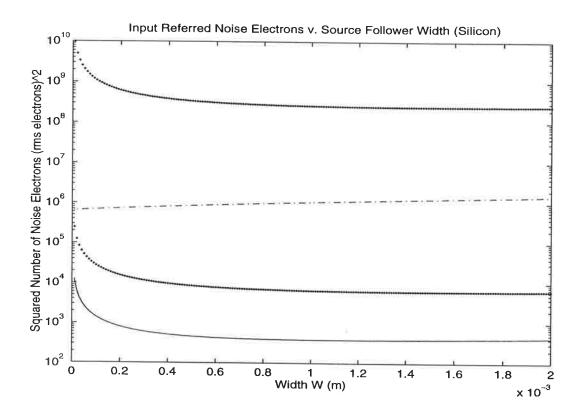

| 4.11 | Imager output circuit noise (silicon)                                                                                                                                      | :0 |

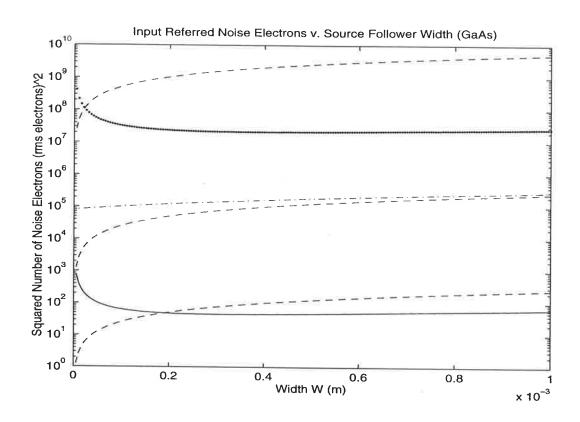

| 4.12 | Imager output circuit noise (GaAs)                                                                                                                                         | :2 |

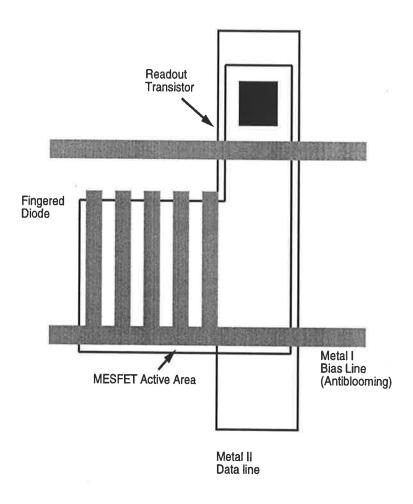

| 5.1  | Fingered Transistor Dual-Gate Pixel Conceptual Layout                                                                                                                      | 0  |

| 5.2  | Pixel Equivalent Circuit                                                                                                                                                   | 1  |

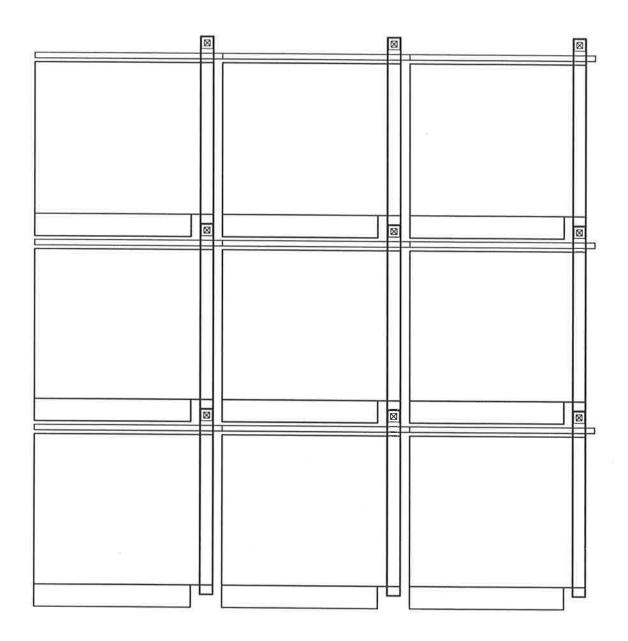

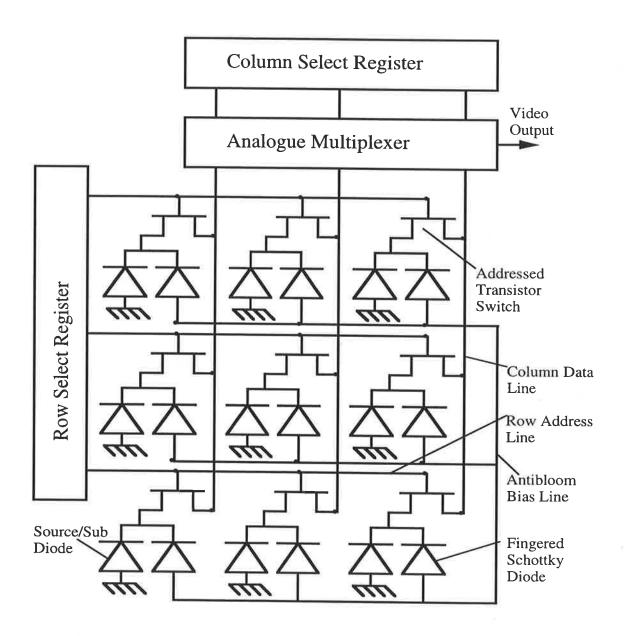

| 5.3  | Layout of 3 by 3 pixels                                                                                                                                                    | 3  |

| 5.4  | Layout of 3 by 3 pixels, with antiblooming structure                                                                                                                       | 4  |

| 5.5  | Array organisation                                                                                                                                                         | 7  |

| 5.6  | Array organisation with antiblooming structure                                                                                                                             | 8  |

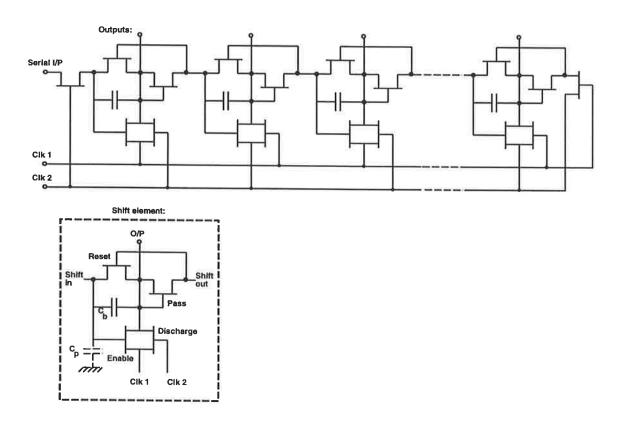

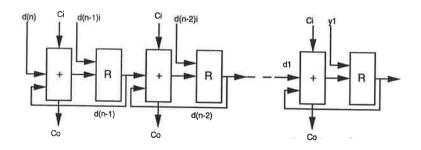

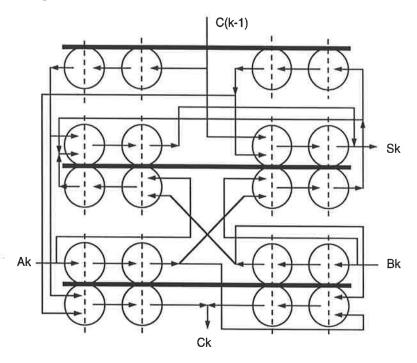

| 5.7  | Shift register with bootstrapped stages                                                                                                                                    | 9  |

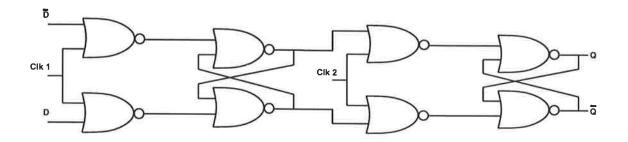

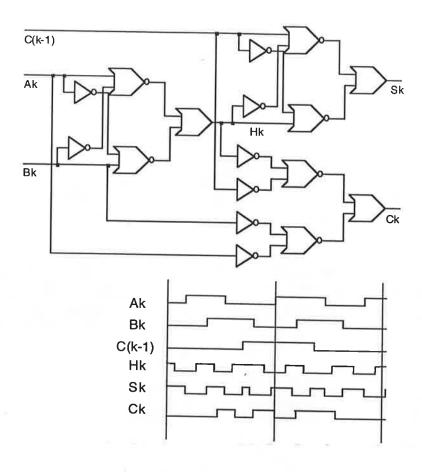

| 5.8  | Conventional D flip-flop shift register stage                                                                                                                              | 1  |

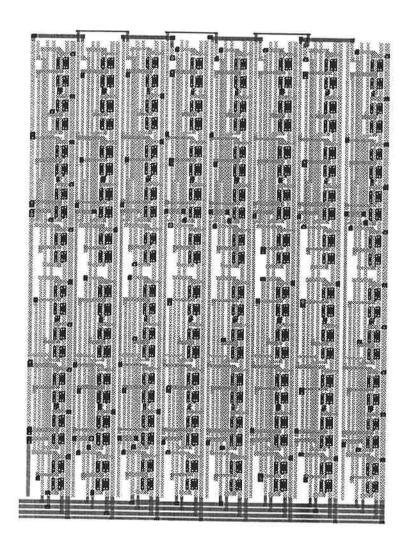

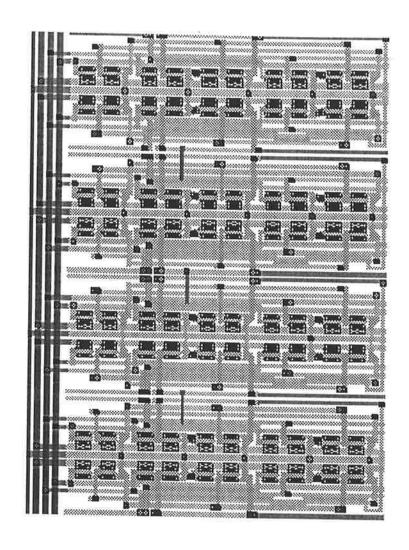

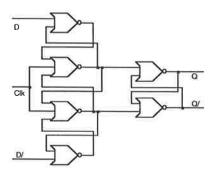

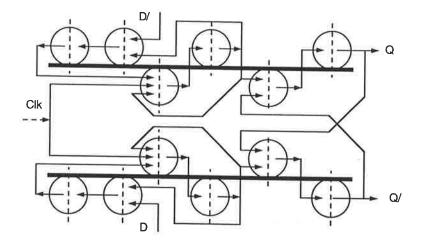

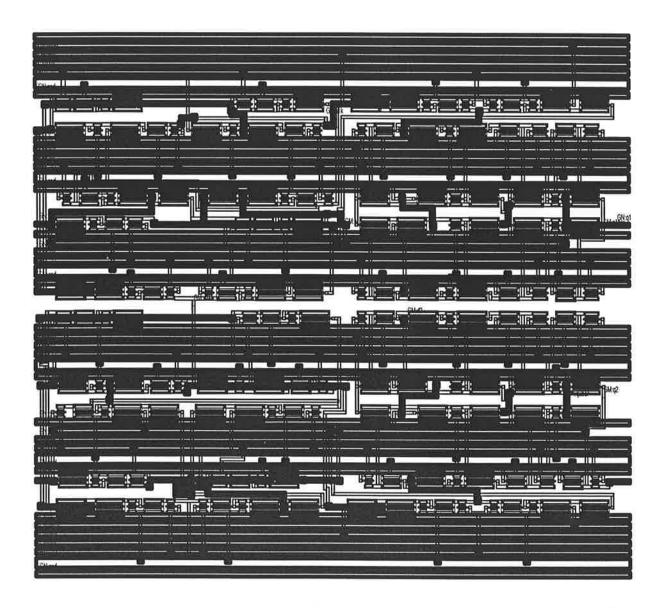

| 5.9  | Conventional D flip-flop shift register layout segment                                                                                                                     | 2  |

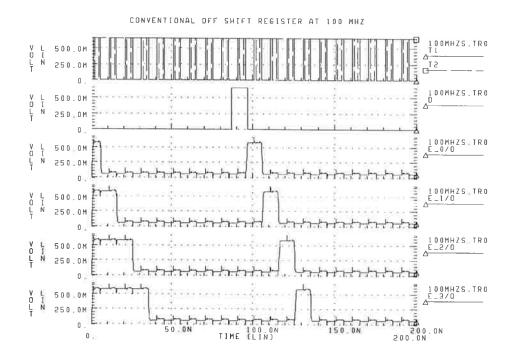

| 5.10 | Conventional D flip-flop shift register simulation. Top trace demonstrates non-overlapping clocks, second trace is the serial input and subsequent parallel outputs follow | 3  |

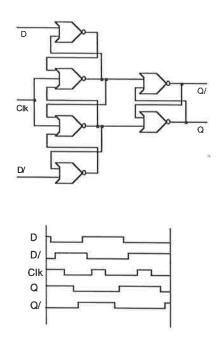

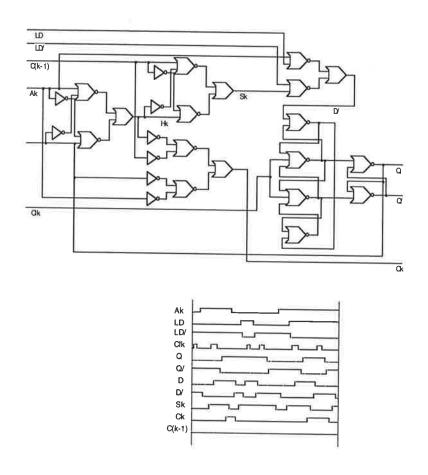

| 5.11 | Edge triggered D flip-flop shift register stage                                                                                                                            | 4  |

| 5.12 | Edge triggered D flip-flop shift register layout segment                                                                                                                   | 5  |

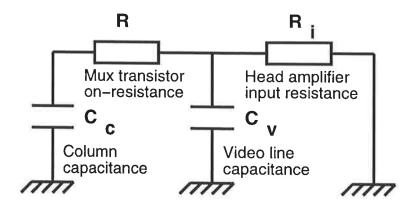

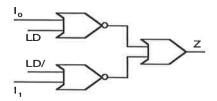

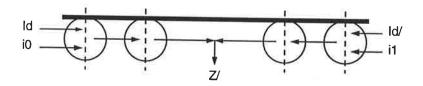

| 5.13 | Column-to-video line switching: equivalent circuit                                                                                                                         | 7  |

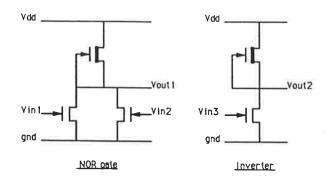

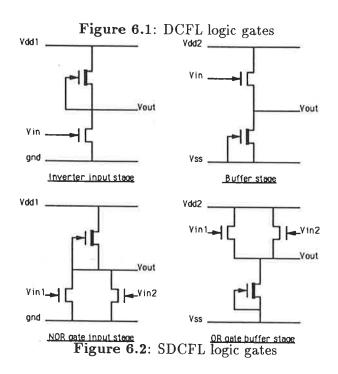

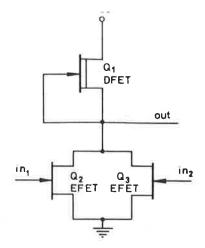

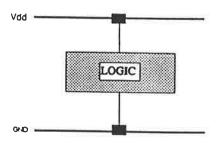

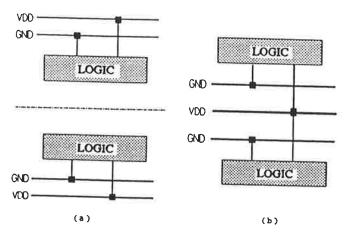

| 6.1  | DCFL logic gates                                                                                                                                                           | 4  |

| 6.2  | SDCFL logic gates                                                                                                                                                          | 4  |

| 6.3  | DCFL inverter circuit                                                                                                                                                      | 5  |

| 6.4  | SDCFL inverter circuit                                                                                                                                                     | 5  |

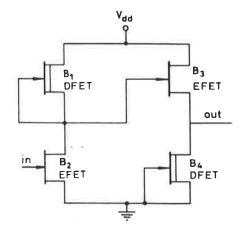

| 6.5  | Photograph qualitatively showing parasitic oscillations in I-V characteristic. Arbitrary axes. Notice region of negative resistance                                        |    |

| 6.6  | Layout styles: nMOS-type stick approach                                                                                                                                    |    |

| -    |                                                                                                                                                                            |    |

| 0.7  | using single bus pair                                                                    |

|------|------------------------------------------------------------------------------------------|

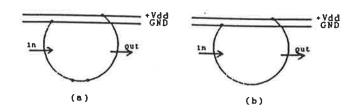

| 6.8  | Ring Notation showing topology of circuit                                                |

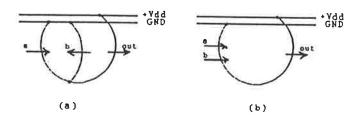

| 6.9  | Ring Notation for 2-Input NOR gate, (a) initial representation, (b) after simplification |

| 6.10 | Translation from Ring Notation into Mask layout for a D-Latch 189                        |

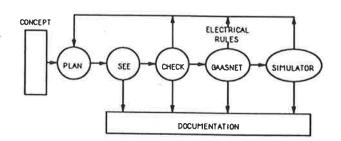

| 6.11 | Gallium arsenide design process using CAD tools                                          |

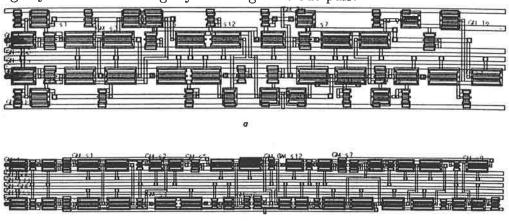

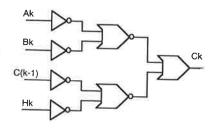

| 6.12 | 1-bit Ripple Carry layout (a) nMOS type stick and (b) Ring Notation 195                  |

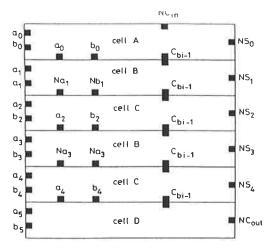

| 6.13 | Floorplan of the GaAs implementation of carry look-ahead expressions 197                 |

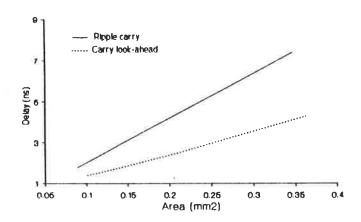

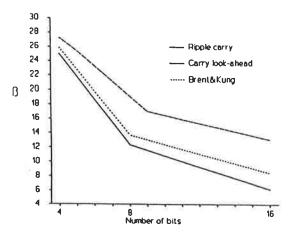

| 6.14 | Area vs. delay of Ripple Carry and Carry Look-Ahead adders 197                           |

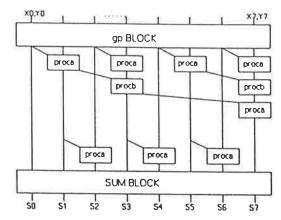

| 6.15 | Block diagram of Binary carry look-ahead adders                                          |

| 6.16 | Comparison of different adders                                                           |

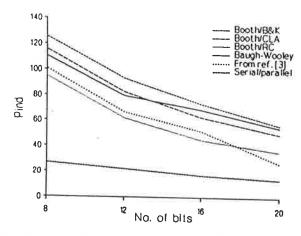

| 6.17 | Computational density of parallel multipliers                                            |

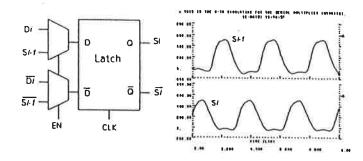

| 6.18 | Shift register bit-slice (a) diagram, (b) simulation 201                                 |

| 7.1  | Edge enhancement/thresholding edge detection system                                      |

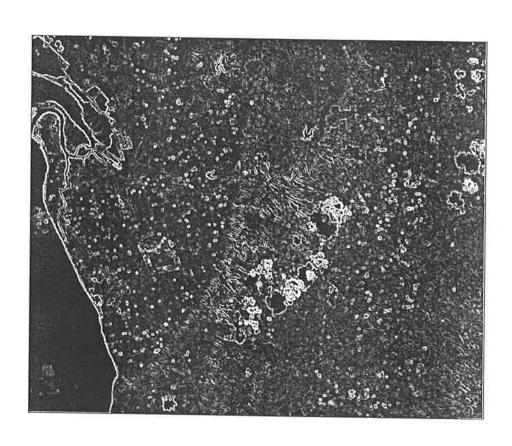

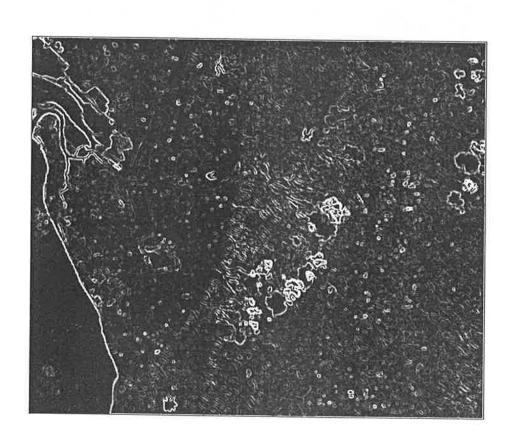

| 7.2  | A satellite image of Adelaide (band7)                                                    |

| 7.3  | The result of edge detection from Roberts operator                                       |

| 7.4  | The result of edge detection from Prewitt operator                                       |

| 7.5  | The result of edge detection from Sobel operator                                         |

| 7.6  | The result of a median filter                                                            |

| 7.7  | The result of Sobel operator applied on the median filtered image 220                    |

| 7.8  | SDCFL design example                                                                     |

| 7.9  | Block diagram of bit-serial algorithmic solution                                         |

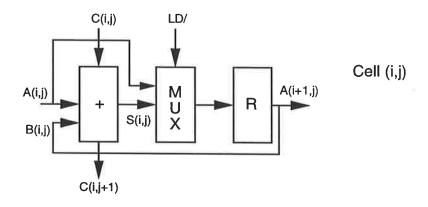

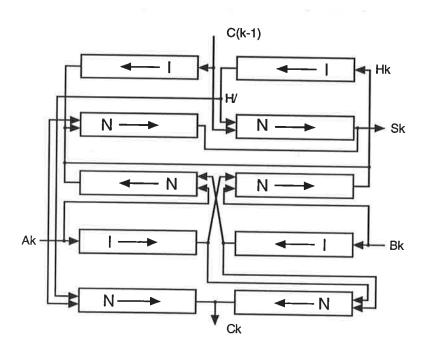

| 7.10 | PE cell structural layout                                                                |

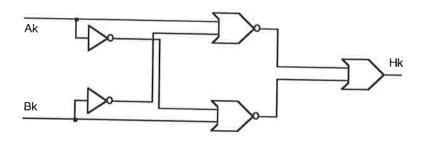

| 7.11 | Generation of half-carry result                                                          |

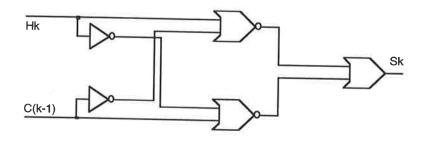

| 7.12 | Generation of sum result                                                                 |

| 7.13 | Generation of carry result                                                               |

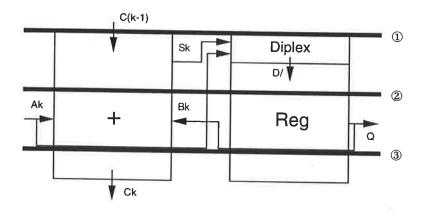

| 1.14 | Register logical representation                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.15 | Diplexor logical representation                                                                                                                                                  |

| 7.16 | Adder floor plan block diagram                                                                                                                                                   |

| 7.17 | Adder cell ring notation                                                                                                                                                         |

| 7.18 | Register cell ring notation                                                                                                                                                      |

| 7.19 | Diplexor cell ring notation                                                                                                                                                      |

| 7.20 | PE cell structural block diagram                                                                                                                                                 |

| 7.21 | Polynomial evaluator cell                                                                                                                                                        |

| 7.22 | Adder and simulation                                                                                                                                                             |

| 7.23 | Register and simulation                                                                                                                                                          |

| 7.24 | Block diagram of bit-serial algorithmic solution with PE cell structural layout below                                                                                            |

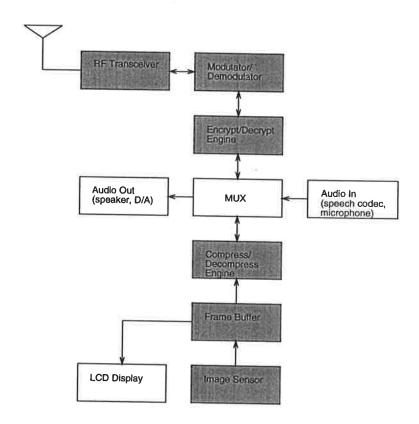

| 7.25 | System block diagram for basic mobile video device. Unshaded areas are standard tasks. Shaded areas need to be particularly addressed by CGaAs solutions                         |

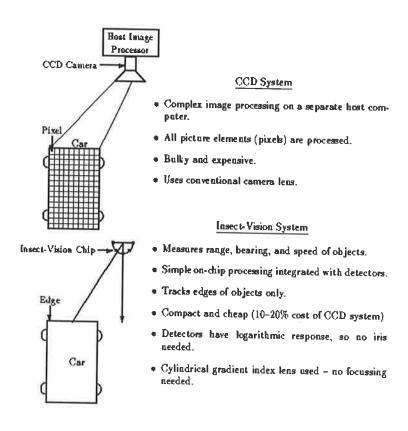

| 7.26 | Insect vision concept compared to conventional CCD camera 244                                                                                                                    |

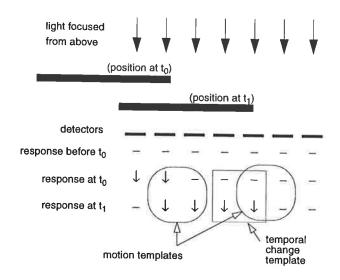

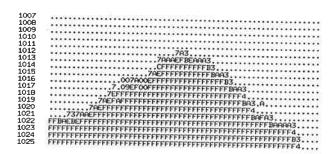

| 7.27 | Coding of templates                                                                                                                                                              |

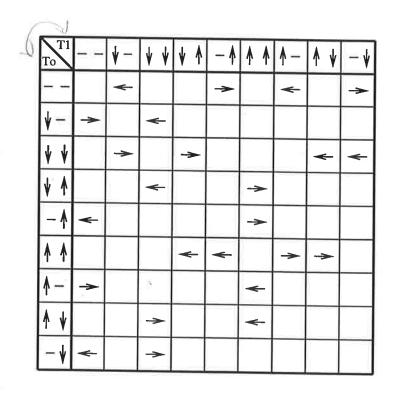

| 7.28 | Template table                                                                                                                                                                   |

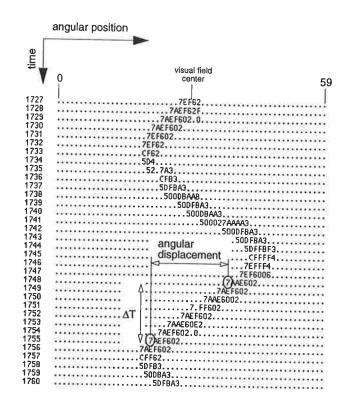

| 7.29 | Example template output pattern. X-axis represents bearing – each sample is 1°. Y-axis represents time – each sample is 20 ms                                                    |

| 7.30 | Extraction of angular velocity from a template pattern                                                                                                                           |

| 7.31 | Looming pattern                                                                                                                                                                  |

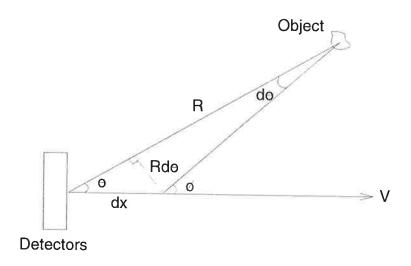

| 7.32 | Calculation for range                                                                                                                                                            |

| 7.33 | Theoretical MTF versus spatial frequency. Diffusion-only curves are for specific optical wavelengths. Geometrical-only curve is for the actual 7/20 aperture to pitch ratio used |

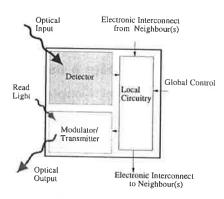

| 7.34 | A Smart Pixel Architecture                                                                                                                                                       |

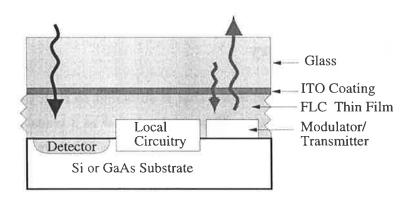

| 7.35 | A FLC/Si or FLC/GaAs Smart Pixel                                                                                                                                                 |

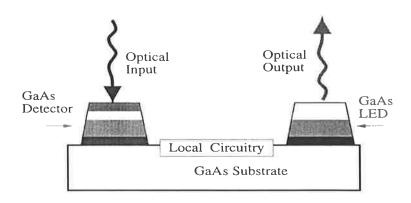

|      | A LED/GaAs Smart Pixel                                                                                                                                                           |

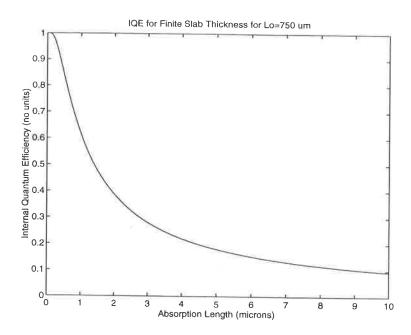

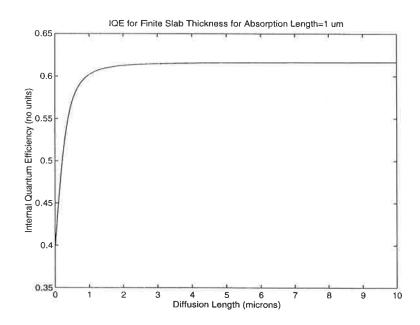

| B.1 | Internal quantum efficiency versus absorption length. | 292 |

|-----|-------------------------------------------------------|-----|

| B.2 | Internal quantum efficiency versus absorption length. | 293 |

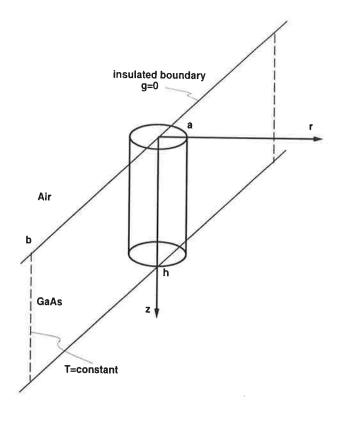

| C.1 | Cylindrical coordinate system                         | 29€ |

# List of Tables

| 2.1 | Historical evolution of GaAs – a brief chronology                                                              |

|-----|----------------------------------------------------------------------------------------------------------------|

| 2.2 | Properties of Si, GaAs, SiC, GaN and Diamond                                                                   |

| 2.3 | Absorption coefficients                                                                                        |

| 2.4 | GaAs v. Si Responsivity                                                                                        |

| 4.1 | History of fluctuation research - a brief early chronology 108                                                 |

| 4.2 | Thermal noise over infinite bandwidth for different cases of limiting R and C                                  |

| 5.1 | Performance comparison of shift registers. Notice Case 1 has no power supplies as it is powered via the clocks |

| 6.1 | Gallium Arsenide Symbolic Representation and Notations                                                         |

| 6.2 | Parameters of several ripple carry adders                                                                      |

| 6.3 | Parameters of the carry look-ahead adders                                                                      |

| 6.4 | Parameters of the binary carry look-ahead adders                                                               |

| 6.5 | Parameters of several adders                                                                                   |

| 7.1 | Some possible insect vision technology application areas                                                       |

| 7.2 | Evolution of 'Bugeye' Insect Vision Chip                                                                       |

#### **GLOSSARY**

ADC Analog-to-digital converter ATMAsynchronous transfer mode BISDN Broadband ISDN CCDCharge coupled device CDS Correlated double sampling CGaAs Complementary GaAs Complementary high mobility GaAs FET (=CGaAs FET) CHFET CID Charge injection device CMT Cadmium mercury telluride CW Continuous wave (unmodulated laser) DCFL Direct coupled FET logic Discrete cosine transform DCT DDS Delayed double sampling **ESD** Electrostatic Damage/Discharge EL2"Electron level 2" - a deep donor FDMFinite difference method FLC Ferroelectric liquid crystal FPN Fixed pattern noise **HBT** Heterojuntion bipolar transistor **HDTV** High definition television **HEMT** High electron mobility transistor HIGFET High mobility insulating gate FET  $IM^3PC$ Interactive mobile multimedia personal communicator IPN Interactive personal navigation ITB Interactive telebanking ITK Interactive time keeping ITO Indium tin oxide **IQE** Internal quantum efficiency LAN Local area network LWIR. Long wave infrared MESFET Metal semiconductor FET MTF Modulation transfer function **MWIR** Medium wave infrared NED Noise electron density NN Neural network Optoelectronic integrated circuit OEIC ONN Optical neural network PAE Power added efficiency QΕ Quantum efficiency RAM Random access memory SISemi-insulating S/D Source or drain S/N Signal-to-noise ratio SOI Silicon on insulator SRAM Static random access memory UDM Unified defect model WFT Windowed Fourier transform ZPEZero point energy ZPF Zero point fluctuations

### Chapter 1

### Introduction

"Research is the process of going up alleys to see if they are blind." Marston Bates (1906-1974)

AMERICAN ZOOLOGIST

"Human knowledge is personal and responsible, an unending adventure at the edge of uncertainty."

Jacob Bronowski (1908-1974)

POLISH-BRITISH MATHEMATICIAN AND POET

### 1.1 Aims and Significance

### 1.1.1 Long Term Aim

The overall aim is to create a significant advance in the area of solid-state imaging via the research of an image sensor than can be ultimately integrated with high-speed gallium arsenide (GaAs) processing circuitry on a common substrate chip. This combination will facilitate a new generation of compact smart sensors, useful in mobile applications for detecting and transmitting full visual images. Spin-off application in the area of high definition television (HDTV) is also promising due to the larger absorption coefficients in GaAs leading to improved spatial resolution. The intention is for a GaAs image sensor, to be fabricated in a standard or near-standard GaAs digital IC process, enabling potential integration with a higher speed GaAs image preprocessor. This new paradigm offers the advantage of a preprocessor that can quickly access the image sensor in serial or parallel to efficiently perform low-level early vision tasks. The high-level vision tasks, if required, may be then carried out in real-time on a simpler host processor. The superior speed-power performance of GaAs over silicon and the excellent ongoing progress in GaAs fabrication maturity make GaAs a favourable choice for mobile applications where superior speedpower product is essential. Also the potential mixed digital/RF capability of GaAs, such as in the emerging  $CGaAs^{TM}$  technology, is ideal for compact wireless mobile systems. The speed performance and other well known characteristics of GaAs are ideal for applications where harsh environment and increasing need for processing speed place high demands.

### 1.1.2 Immediate Aim of this Work

Due to very large throughput rates and vast amounts of data necessary for real time performance, there is an increasing demand for higher speed and lower power consumption in digital image and signal processors. This means that the choice of algorithms, and indeed that of the architecture to match the technology, becomes a crucial task in the realisation of such systems for real time applications.

Within the scope of the research to develop an imaging system for mobile applications it became obvious that many interrelated tasks had to be pursued in order to address numerous questions in relation to Ultra High Speed systems. The issues that required careful consideration included, the identification of suitable technology for Very High and Ultra High speed image processing, front end processing including the photodetector characteristics, architectural mapping and the design methodology.

Having identified gallium arsenide as a suitable contender, the complexities associated with this emerging technology became a focus for much of the initial research program. As the result of this investigation, an original approach to design methodology and hence architecture, referred to as the 'Ring Notation,' has been developed [Eshraghian 91].

The performance of GaAs optical sensors is already proven by our previous investigations [Abbott 91] and the work of others [Darling 93, Lange 94, Lin 93, Hibbs 91, Kozlowski 92], therefore one of the remaining major tasks in the development of a GaAs image sensor is to determine the various factors which affect the optical gain mechanisms in a GaAs MESFET. Thus, the need to accurately model, the behaviour of the MESFET transistor for implementation within the image sensor became the first major task pursued. It may be noted that considerable controversy in the literature exists over the nature of GaAs MESFET optical gain. As a result of our investigation, a consistent model was developed that overcame the difficulties raised by other researchers engaged in the controversy [Adibi 89].

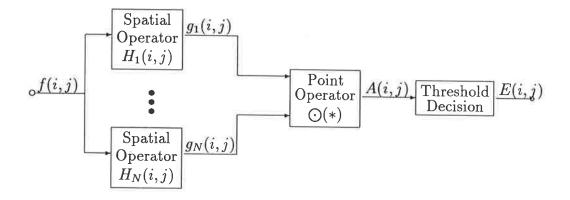

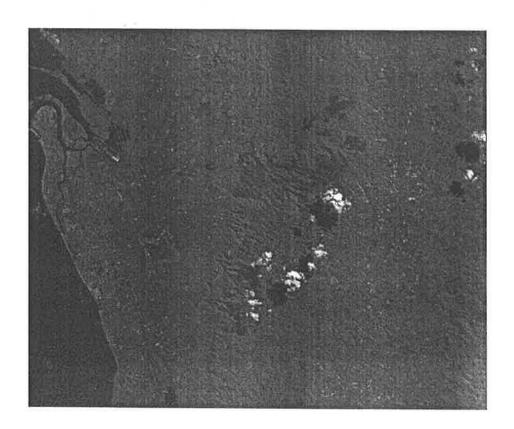

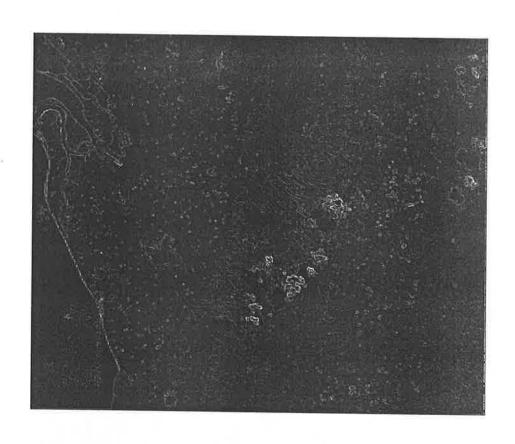

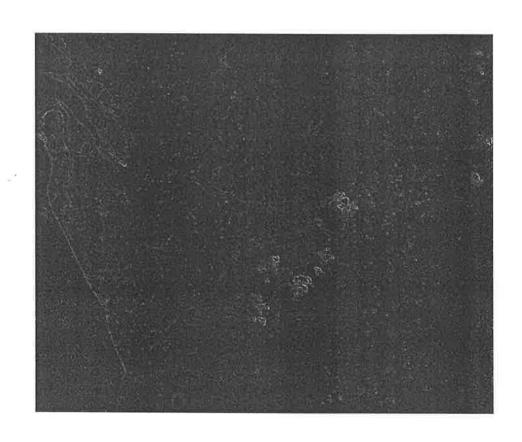

This model is used to resolve apparent contradictions, between different results published in the literature, by observing that each of the reported effects come into play by varying degree depending on the wavelength of light used and hence penetration depth achieved. The results have been instrumental in providing a better understanding towards realisation of both on-chip and off-chip optical interconnects. Furthermore, in the course of our research, we uncovered an important effect that we have termed the "Edge Effect." This discovery may well have significant influence upon the pixel design of future imaging systems.