# VLSI Systems Simulation

Michael T. Pope

A thesis submitted to the faculty of Engineering for the degree of Doctor of Philosophy

Department of Electrical and Electronic Engineering

The University of Adelaide

South Australia

January 1991

# Contents

| 1 | Intr | oducti | on                             | 1  |

|---|------|--------|--------------------------------|----|

|   | 1.1  | Simula | tion                           | 1  |

|   |      | 1.1.1  | The Transform and Filter Brick | 2  |

|   |      | 1.1.2  | Communications Link            | 7  |

|   |      | 1.1.3  | Lessons and conclusions        | 8  |

|   | 1.2  | Overvi | lew                            | 10 |

|   |      |        |                                |    |

| 2 | Lite | rature | Review                         | 11 |

|   | 2.1  | Introd | uction                         | 11 |

|   | 2.2  | Taxon  | omy of Modes                   | 11 |

|   |      | 2.2.1  | Architectural                  | 12 |

|   |      | 2.2.2  | Structural                     | 13 |

|   |      | 2.2.3  | Functional                     | 14 |

|   |      | 2.2.4  | Digital                        | 15 |

|   |      | 2.2.5  | Analog                         | 16 |

|   |      | 2.2.6  | Device                         | 17 |

|   |      | 2.2.7  | Timing                         | 18 |

|   |      | 2.2.8  | Fault                          | 18 |

|   |      | 2.2.9  | Mixed and Hybrid               | 18 |

|   | 2.3  | Functi | ional and Structural Modes     | 19 |

|   |      | 2.3.1   | Introduction                        | 19 |

|---|------|---------|-------------------------------------|----|

|   |      | 2.3.2   | Hardware Description Languages      | 20 |

|   |      | 2.3.3   | Low Level Modelling                 | 23 |

|   |      | 2.3.4   | Timing Analysis                     | 28 |

|   |      | 2.3.5   | Goals                               | 32 |

|   | 2.4  | Digital | l Modes                             | 33 |

|   |      | 2.4.1   | Introduction                        | 33 |

|   |      | 2.4.2   | Logic States                        | 34 |

|   |      | 2.4.3   | Logic Strengths                     | 37 |

|   | g.   | 2.4.4   | Digital Simulation Algebras         | 41 |

|   | 2.5  | Bidire  | ctionality                          | 42 |

|   |      | 2.5.1   | Delay Modelling                     | 44 |

|   |      | 2.5.2   | Other Features                      | 44 |

|   | 2.6  | Analog  | g Modes                             | 48 |

|   |      | 2.6.1   | Introduction                        | 48 |

|   |      | 2.6.2   | Analog Circuit Equation Formulation | 48 |

|   |      | 2.6.3   | SPICE                               | 51 |

|   | 2.7  | Speedi  | ing up SPICE                        | 54 |

|   |      | 2.7.1   | A Philosophical Digression          | 57 |

|   |      | 2.7.2   | Alternative Analog Approaches       | 61 |

|   | 2.8  | Mixed   | Modes                               | 65 |

|   | 2.9  | Hybrid  | d Modes                             | 71 |

|   | 2.10 | Summ    | ary                                 | 75 |

| 3 | Des  | ign of  | Loge                                | 77 |

|   | 3.1  | Introd  | luction                             | 77 |

|   | 3.2  |         | ure                                 |    |

|   |      |         | HDL issues                          |    |

| *.1 | 3.3 | Schedu | ıling                    |

|-----|-----|--------|--------------------------|

|     |     | 3.3.1  | Scheduling Algorithms 82 |

|     |     | 3.3.2  | Event Suppression        |

|     | 3.4 | Simula | ation Objects            |

|     |     | 3.4.1  | Nodes                    |

|     |     | 3.4.2  | Ports                    |

|     |     | 3.4.3  | Modules                  |

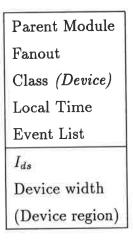

|     |     | 3.4.4  | Devices                  |

|     |     | 3.4.5  | Analog Devices           |

|     |     | 3.4.6  | Example                  |

|     |     | 3.4.7  | Summary                  |

|     | 3.5 | Simula | ation                    |

|     |     | 3.5.1  | Simulation control       |

|     |     | 3.5.2  | Tools                    |

|     |     | 3.5.3  | Verification             |

|     | ъ   | 14     | 167                      |

| 4   | Res |        |                          |

|     | 4.1 |        | luction                  |

|     | 4.2 |        | al Performance Tests     |

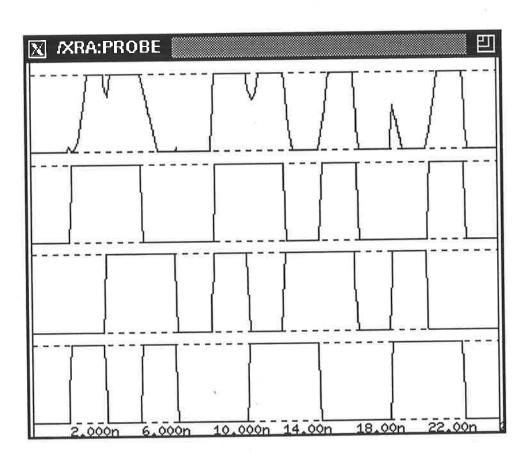

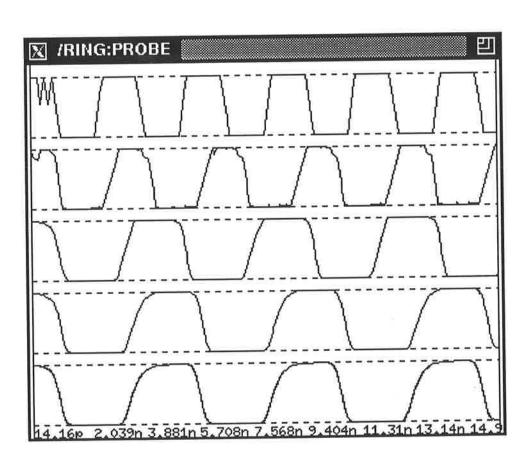

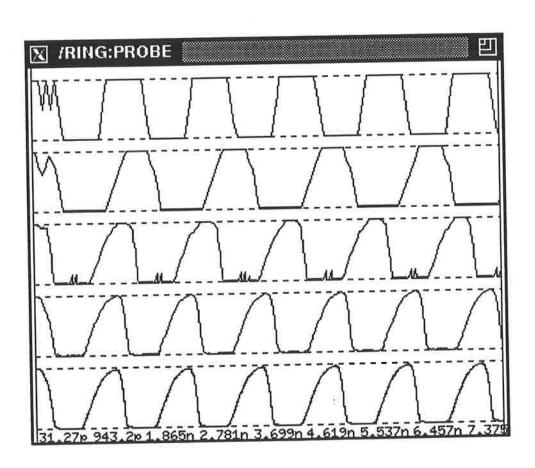

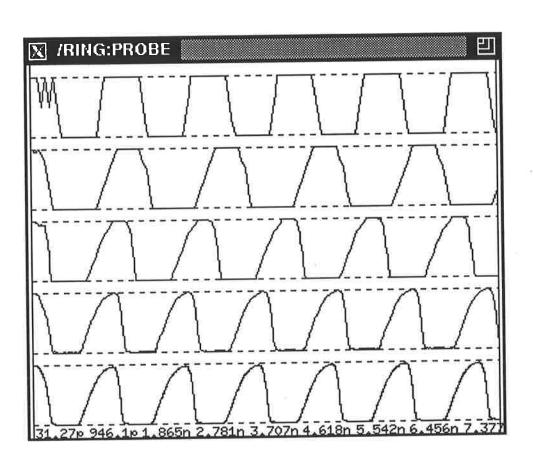

|     |     | 4.2.1  | Ring Oscillator          |

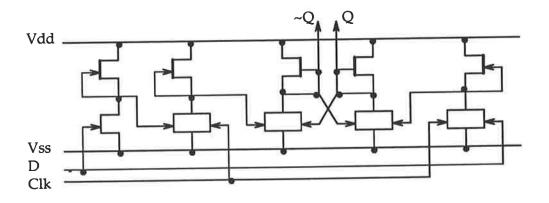

|     |     | 4.2.2  | Shift Register           |

|     |     | 4.2.3  | Adder                    |

|     |     | 4.2.4  | Binary Trees             |

|     |     | 4.2.5  | Barrel Shifter           |

|     |     | 4.2.6  | Memory                   |

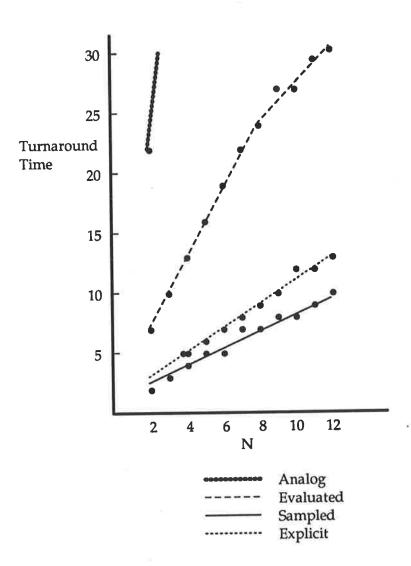

|     |     | 4.2.7  | Simulator performance    |

|     |     | 4.2.8  | Summary                  |

|     | 12  | CaAa   | technology               |

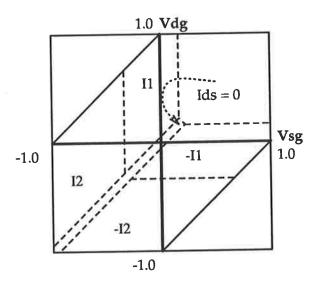

|   |     | 4.3.1  | MESFET current models                                  | 2  |

|---|-----|--------|--------------------------------------------------------|----|

|   |     | 4.3.2  | Simulations                                            | 5  |

|   |     | 4.3.3  | Summary                                                | 8  |

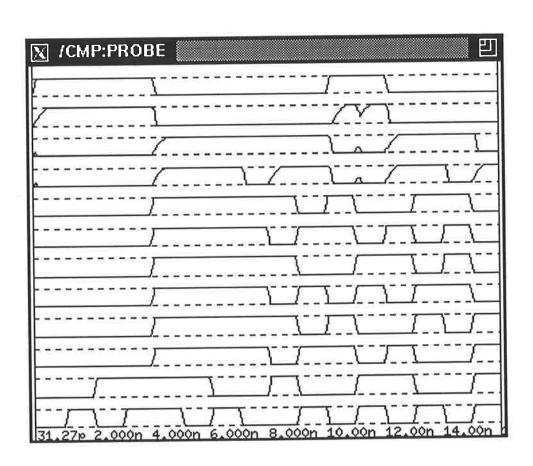

|   | 4.4 | Design | of a Combinator Engine                                 | 13 |

|   |     | 4.4.1  | Introduction                                           | 13 |

|   |     | 4.4.2  | Functional Programming and Combinators                 | 13 |

|   |     | 4.4.3  | Combinator Compilation Example                         | 15 |

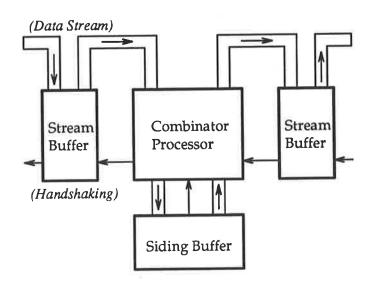

|   |     | 4.4.4  | Basic Architecture                                     | 16 |

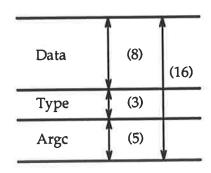

|   | ×   | 4.4.5  | Tokens                                                 | 18 |

|   |     | 4.4.6  | Argument Counting                                      | .3 |

|   |     | 4.4.7  | Combinator Execution Example                           | 4  |

|   |     | 4.4.8  | Stream                                                 | 15 |

|   |     | 4.4.9  | Control                                                | 6  |

|   |     | 4.4.10 | Combinator Processor Design                            | 17 |

|   |     | 4.4.11 | Combinator Processor: A Loge Functional Description 22 | 21 |

|   |     | 4.4.12 | Combinator Processor: Hardware Partitioning 23         | 33 |

|   |     | 4.4.13 | Other stream elements                                  | 35 |

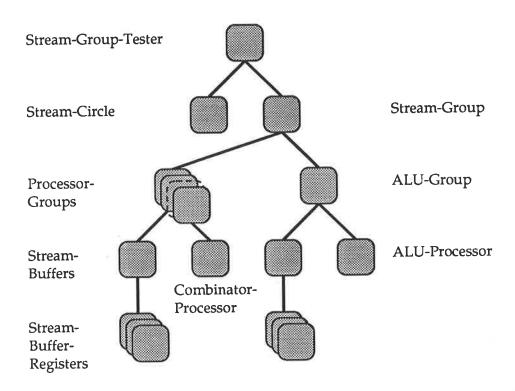

|   |     | 4.4.14 | Stream Group                                           | 35 |

|   |     | 4.4.15 | Top Level                                              | 37 |

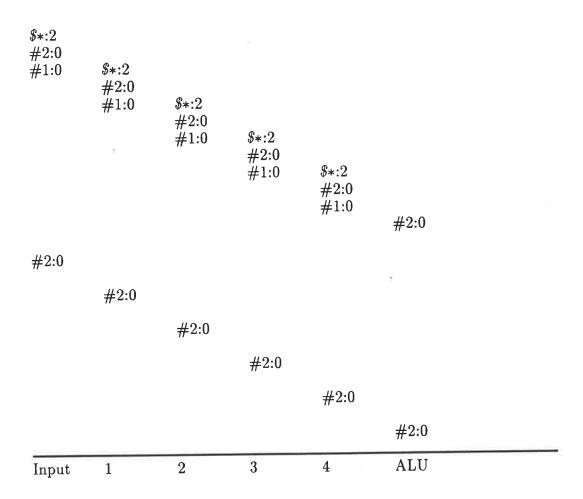

|   |     | 4.4.16 | Simulations                                            | 38 |

| 5 | Cor | clusio | ns 25                                                  | 51 |

#### Abstract

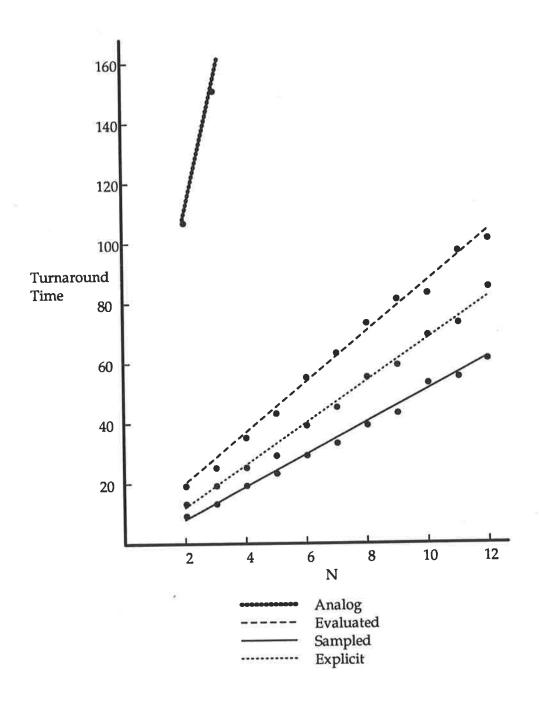

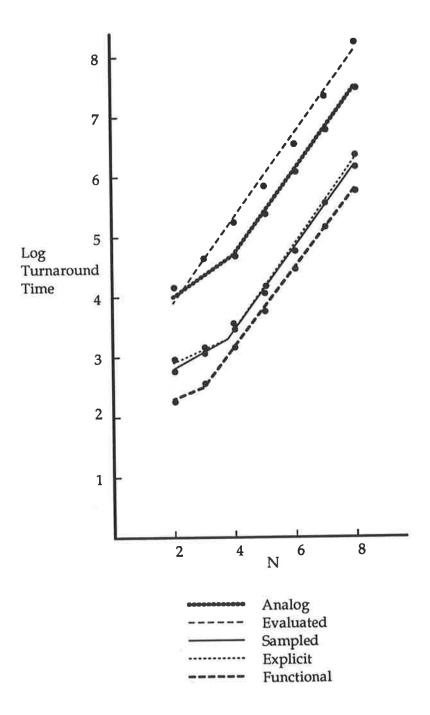

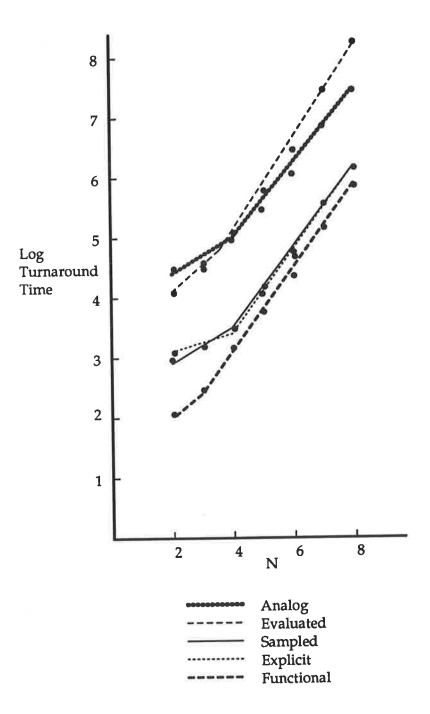

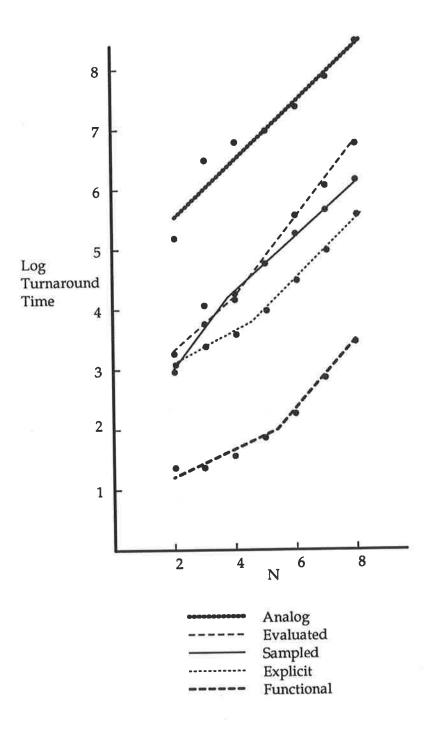

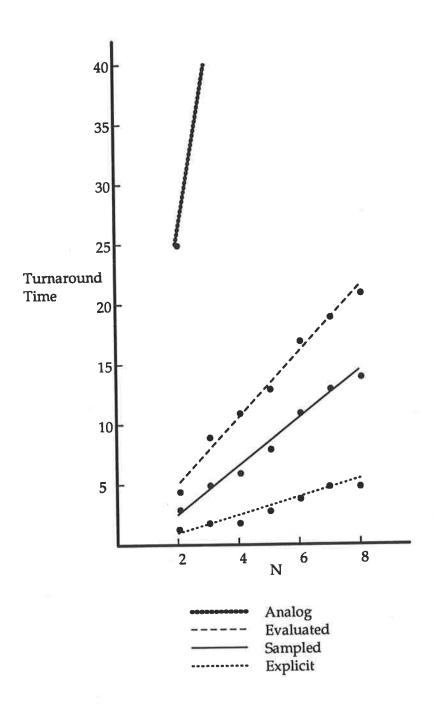

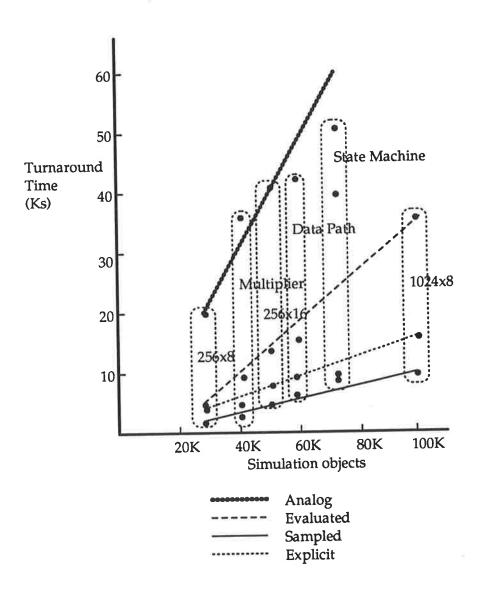

The complexity of modern digital systems, particularly VLSI systems, continues to grow quickly. Simulation has become entrenched as a vital technique for dealing with this complexity, in a variety of ways. In simulation there is a perennial tradeoff between the conflicting goals of accuracy of the results and speed of simulation (turnaround). It is highly desirable that simulation tools exhibit some variability in this regard.

This thesis details the design, implementation and performance of Loge—a simulation tool which while developed for MOS VLSI is quite adaptable to related technologies and digital systems generally. The core of the design philosophy of Loge is that it support a fast moving investigative style of development, where turnaround receives greater emphasis than fine points of accuracy (good simulators with the opposite emphasis are readily available).

Loge is a mixed-mode, variable speed/accuracy system. The modes implemented form a continuum of abstraction, from a functional level (based on a powerful hardware description language which allows the specification of generic modules), through a choice of hybrid modes, down to a conventional analog device modelling mode. All modes interface cleanly with each other within the limits imposed by different levels of abstraction. Flexibility and responsiveness to user control are featured throughout.

## Note

This thesis contains no material which has been accepted for the award of any other degree or diploma in any University and to the best of my knowledge and belief contains no material previously published or written by another person without due reference being given.

I consent to this thesis being made available for photocopying and loan if accepted for the award of the degree.

Michael T. Pope

# Acknowledgements

Undoubtedly, this project would never have occurred but for the infectious enthusiasm and stimulating instruction of my supervisor, Kamran Eshraghian. Thank you for all the encouragement, support and for creating an environment full of opportunities to wander through interesting fields of learning.

Integrated Silicon Design deserve mention for appearing just at the right time with an offer of a quick contract programming job...little did either party know that it would be the first step or a longish trek towards a Ph.D. thesis.

Alex Dickinson can not escape special note for some highly disruptive suggestions— while happily trying to cut a path through the jungle with a pair of scissors, Alex would suddenly hand one a chainsaw. Thanks are also due for the architecture used in the functional simulation case study.

It is still a mystery how Mike Liebelt found the patience to deal with an endless stream of awkward requests and foolish questions while keeping the computers running reliably. Many thanks Mike for all the times "The Guru was In".

DSTO Salisbury have been very helpful in providing equipment, comment and financial support— especial thanks to Peter Drewer for the encouragement and wry but apposite remarks.

Other assorted technical help came from people like Ian Dall, Alf Grasso, John and Simon Rockliff, Bruce Tonkin, Richard Wagner, Susan Wu, Greg Zyner and the massed TFB project members. The DCFL flip flop design is due to Derek Abbott.

Many other people deserve appreciation for positive contributions to ones

<sup>&</sup>lt;sup>1</sup>Sometimes I took a little while to realize how to use it...

working environment. I would like to acknowledge the participants at tea time and Friday night dinners (especially the Vice-President for Business Dinners, and the Whitbreads for regularly turning their house into a restaurant substitute), Amber, J.S.Bach, Communica, the Australian Broadcasting Corporation's classical FM network, Bitey, W.Yendor, and all past, inactive, and active members of the Flat Earth Society.

Finally I would like to thank my extremely patient family, especially my parents, to whom this thesis is dedicated.

# Chapter 1

# Introduction

### 1.1 Simulation

Among the attractions of VLSI design over previous technological paradigms is that it gives the designer great freedom. Freedom to directly build interesting new structures and to solve problems with an elegance approaching that of mathematical proofs... but for the inevitable intrusion of technological details and practical limits such as die size. Throughout all engineering disciplines such a gap exists between the theoretical world of the provably correct and the practical world of the flawed implementation. Simulation is a major technique used to bridge this gap in the field of VLSI, and indeed in digital systems generally.

Simulation is useful throughout the entire process of design, in a variety of roles—

Design Implementation For the present, the most intensive simulation effort tends to occur in excitation of models of a system under active development where the model has been extracted from an independent implementation representation. Here, the role of the simulator is to

reveal errors in functionality.

- Speculative Investigation Alternately, a simulator can be a model building tool— models may be created in some abstract format with no direct connection to an implementation. These models are then be refined and experimented with in a exploratory fashion. This role could be labelled— "simulator as whiteboard". It is the theoretical complement to the practical design implementation role.

- Functionality Investigation Given a model, the addition of instrumentation to support studies of its internal operation— perhaps to identify bottlenecks, collect performance statistics, or for exhaustive checking of special cases. This role embraces the previous two— the system being simulated could equally be an extracted implementation or a speculative model.

- Comparison Many models of the same logical system are possible, either as independent abstract representations or extractions of different implementations. Some may be correct and others faulty—comparison of their behaviour under identical test conditions is likely to be instructive. This is a special case of functionality investigation.

Unsurprisingly, most existing simulators focus on the demands of simulation for design implementation. There is however good reason to desire a wider ranging simulation system, as the following experiences suggest.

## 1.1.1 The Transform and Filter Brick

The Transform and Filter Brick (or TFB for short) [Eshraghian+85] was an innovative signal processing architecture developed in the mid-eighties by a

team of academics, postgraduates and undergraduates lead by Dr. Kamran Eshraghian at the University of Adelaide, Department of Electrical and Electronic Engineering (the author's principal responsibility in the project was in design and implementation of the memory subsystems).

The TFB architecture is quite complicated, due to the inherent demands of the problems it was designed to solve, which require multiple functional units (ALUs and memory) operating in parallel on a shared but segmented ring bus. Thus TFB encountered the design tradeoffs common to other multiple functional unit systems, such as the VLIW (Very Long Instruction Word) processors [Cohn+89].

From the beginning of the project, it was realized that a serious obstacle to its progress was the conceptual barrier that complexity imposes on a design and implementation group. The research of one TFB team member directly tackles this problem— Alex Dickinson's thesis Complexity Management and Modelling of VLSI Systems [Dickinson88]. Amongst the results in this thesis is a discussion of the modelling tool Pink, which is derived from an earlier system called TICTOC, which was developed in parallel with the development of TFB. It was intended that an extensive overall simulation of the TFB architecture be made— to convince the design team of its correctness, and to provide a more precise semi-formal specification of the system than could be supplied by a simple written report.

Unfortunately, for various resource and manpower-related reasons the overall simulation was never fully realized [Schomburgk84], which was cause for some discouragement. With the benefit of hindsight, it appears that the TFB group erred in placing to much emphasis on implementation at the expense of simulation.

Even in the implementation of subsystems, complexity was a major obstacle. However, here quite strenuous efforts were being made to overcome it.

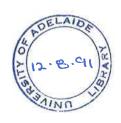

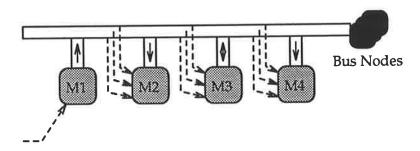

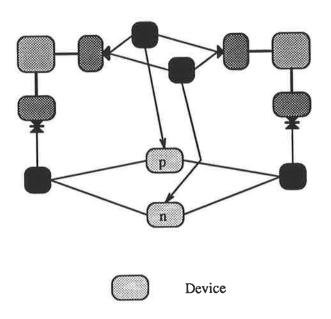

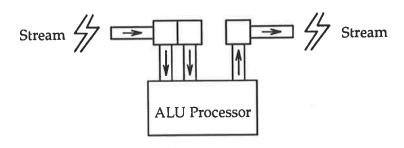

Some difficulties with the subsystems were imposed by the constraints of the implementation technology. TFB was conceived to be a CMOS single chip processor, which could be collected together in large arrays to attack problems of interest to the signal processing researchers in the group. Given that the TFB architecture (figure 1.1) included four ALUs (including divider), four small memory blocks, an Input and an Output processor, a large program memory, decoder, plus considerable routing and control, the problem of squeezing the required functionality onto the die was an ambitious project for the time. Certainly it was the largest and most complex VLSI design and implementation project attempted by our department, albeit a logical development from participation in a number of multi-project chip designs [Clarke82].

The subsystems of TFB, although mostly simple in structure, were nevertheless sizable objects. The combination of a growth in module size with a fairly static set of software tools and a fixed small amount of computing capability resulted in badly degraded tool performance, sometimes to the point of failure. In particular, one of the most adversely affected tools was an analog simulator [Int87]. This was the main tool used to check the correctness of implemented designs, thus the resulting reduction in the amount of simulation that could practically be performed damaged the credibility of much of the implementation work.

Nevertheless, subsystem implementation proceeded to completion of layout. At this point we could conclude that—

- The subsystems worked in isolation for a small test set.

- No one had noticed anything in the specification of the overall architecture that was obviously wrong.

However we were unable to draw any stronger conclusions, such as, for

Figure 1.1: TFB Basic Architecture

example— that an ALU would be able to read data from its local memory over the ring bus under microcode control if everything was connected together. Clearly the existing simulation systems were unlikely to be able to reassure us given that they were struggling to handle problems ten times smaller than the situation being contemplated. In particular, it was estimated that the time to create the extracted description of the whole system would exceed the mean time between shutdowns of the computing facilities available to us. Yet it was important to investigate such details as—

- How tolerant was the architecture to control signal skew?— particularly on control lines that lead to the isolating gates between different sections of the bus.

- How accurate were our estimates of the ring bus capacitance? Would a series of iterations of resizing the bus drivers be necessary?

- How accurate were our estimates of subsystem power consumption? —

specifically with respect to concern about metal migration and number of supply rail pins necessary.

- for which we had no answers that seemed (at least to the author) to be any better than folklore.

Thus once the task of integrating the subsystems was reached the inadequacy of the simulation strategy taken to that point became very clear.

There remained the possibility that a dedicated person could hand-edit a net

list, leaving only the interface logic—but this was recognized to be a very

time consuming and error prone option, to be avoided if possible. It was

perhaps merciful that at this point the TFB project wound down through

lack of funding—the last stages would have been both tedious and difficult,

due to the earlier compromises.

#### 1.1.2 Communications Link

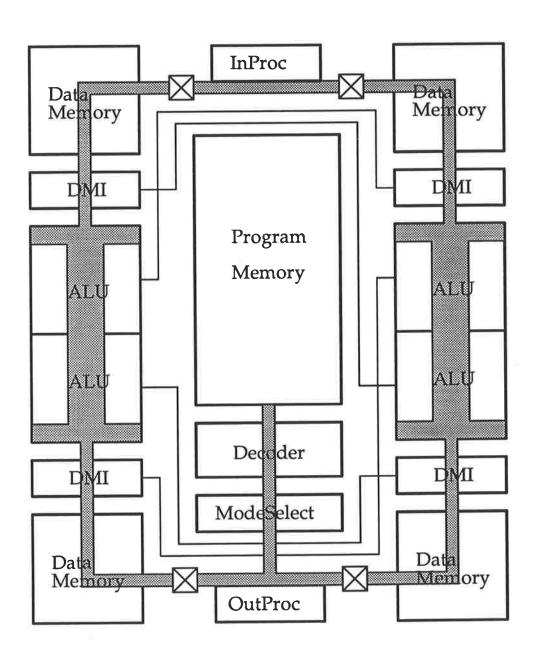

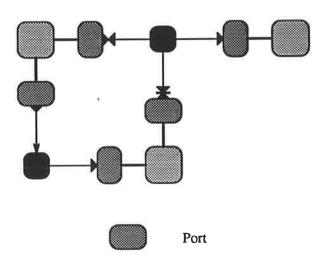

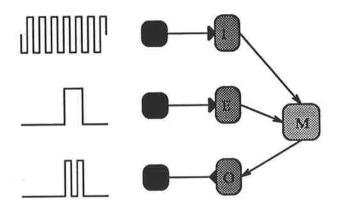

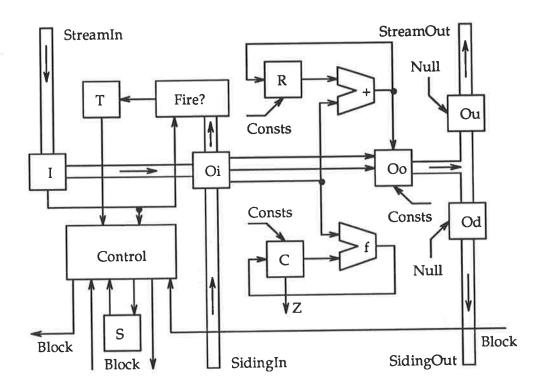

The lessons of the TFB project were reinforced in an unrelated commercial project, but with a brighter outcome. Briefly, the problem was to devise and implement an interface between a bidirectional two-megabit per second serial data link (connected to microwave hardware) and a bidirectional sixteen bit parallel port. The system would be configured identically at both ends of the link as shown in figure 1.2. The two-megabit link was to be considered unreliable, but no data entering through the parallel ports was to be lost.

Figure 1.2: Communications Link

Following a fairly conventional path, the system was built from a commodity microprocessor, memory, communications controller and checksum generate/check hardware. The controlling software provided a simple packetizing scheme (a remote relative of the widely implemented Kermit protocol [da Cruz87]). Development proceeded relatively smoothly, but stalled at a point where the system worked most of the time, but would occasionally unexpectedly lose packets.

Happily, simulation saved the day. The errors were too infrequent and ill-defined to be caught in the physical system, so a high level language simulation of the hardware/software system was quickly developed. This allowed arbitrarily flexible tests to be performed, and in a short time a few marginal special case failure conditions were identified and corrected, resulting in

a reliable link, and a conviction that one should have done the simulation sooner.

#### 1.1.3 Lessons and conclusions

The experience of the TFB project heavily emphasized the importance of both adequate initial investigative simulation, and high quality implementational simulation. One noticed a feeling of paralysis when designing with the knowledge that testing would be difficult to impossible.

The communications link project highlighted the advantages a flexible simulation model has over a less malleable physical piece of hardware or VLSI design representation. In particular it brought home—

- The relative ease with which one can instrument a computer model for functionality investigation.

- The usefulness of comparative simulation, particularly in comparing a steadily refined reference model with a near complete but fault-ridden implementation.

- Attention to accurate modelling is extremely important— each time one increased the level of detail of simulation, another level of marginal error could be found.

The last item above exposes the great weakness of relying extensively on simulation to find errors and characterize performance of a system— one must trust the simulator and models to some degree. Such trust can never be absolute outside the domain of proofs of correctness, and develops under stimuli of rather mixed quality. Comparative simulation is a good method of improving confidence in a model or group of models, but with the dilemma

that if two models disagree, which is wrong? — is there a mistake in the high level specification of the reference model, or a simple miswiring of the implementation, an error introduced by the extraction process, or are both models wrong?

These concerns notwithstanding, the main conclusion reached from the preceding experiences is that to design and build systems of significant size or novelty it would be most helpful to be able to use a wide ranging simulator capable of acting in all roles listed in section 1.1 (the speculative role in particular is of interest to the author for the purpose of investigating novel computer architectures). Development of such a simulator thus became the goal of this research.

Having decided to develop a simulator, one must consider the question of what it should simulate. Despite the VLSI Systems of the title, in practice the scope of the project broadened towards technological independence—the final result is almost technology neutral, making it suitable for the simulation of general purpose digital systems. Similarly while it was initially intended to apply the classic approximation that signals are mainly restricted to the set  $\{Hi, Lo\}$  (the digital model), in practice this attempted narrowing of scope failed to hold— analog phenomena are quite capable of compromising the digital model, therefore analog quantities are modelled everywhere (although the digital model is more readily apparent to the user). Nevertheless, there is no intention or capability to compete with highly detailed analog simulators (at the level of SPICE [Nagel75]).

Another intentional limitation is that parallel operation was not considered a major design criterion. Interestingly though, several practical considerations arose that resulted in a surprisingly parallelizable design. This is clearly an area for future work. The original limitation was due to practical constraints such as the then relative scarcity of parallel hardware, and be-

cause in a cost-conscious world, uniprocessor systems are likely to persist as hosts for simulations for a considerable period of time.

#### 1.2 Overview

Having introduced the background and motivation for this thesis in this chapter, chapter two continues with a combination of literature review, philosophical discussion and development of more specific design criteria than those given so far. A taxonomy of simulation modes and clarification of general terminology appears. Chapter three is a detailed description of the design, implementation and operation of the general purpose digital simulator— Loge. In chapter four performance is summarized and case studies presented. Conclusions appear in chapter five.

Finally, in what way is this work a novel contribution to the field? Briefly, the notable features of Loge include—

- Clean by design inter-mode interfaces— existing simulators are prone to restrictions introduced by loss of information at mode and/or module boundaries.

- A concise, powerful and extremely flexible hardware description and functional modelling language—specified modules may be *generic*.

- Variable accuracy simulation modes.

- Fully event-driven operation throughout.

- resulting in a high quality digital simulator and architectural modelling tool.

# Chapter 2

# Literature Review

## 2.1 Introduction

The overall intention of this chapter is to steadily clarify the requirements for a good digital simulator through a review of the extensive literature on simulation of integrated circuits from the major and more accessible conferences and journals. As important design criteria arise they will be noted in the form—

Design for (some significant design criterion) (0)

# 2.2 Taxonomy of Modes

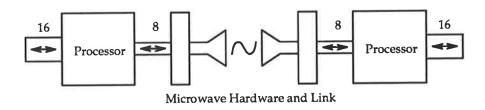

The most logical way of decomposing the field of integrated circuit simulation is by simulation mode. Each simulation mode (or level) is characterized by the assumptions made in abstraction from reality. There are many modes, forming a continuum of abstraction.

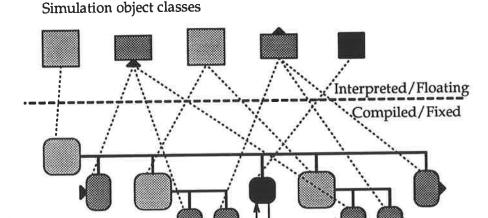

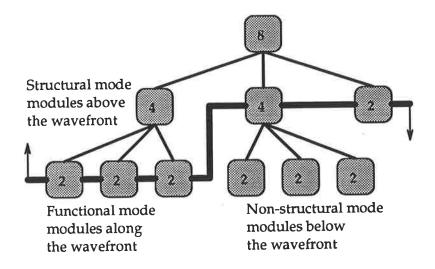

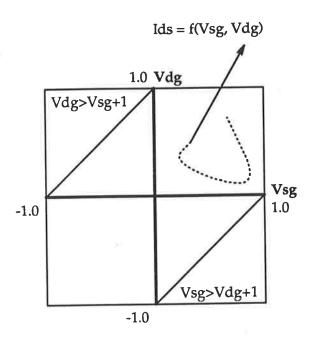

Unfortunately, the names of the modes vary from researcher to researcher. Figure 2.1 clarifies the terminology of this document, defining the main sim-

ulation modes in decreasing order of abstraction. Synonyms and submodes are not shown, but will be discussed under their parent mode.

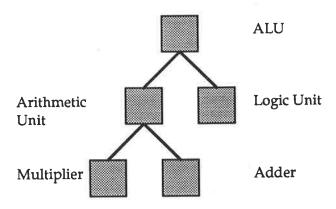

Figure 2.1: Mode Hierarchy

#### 2.2.1 Architectural

Architectural mode simulation is the abstract mental process of design. It is often associated with analysis of requirements, for example "This device is intended to compute inner products— therefore the arithmetic unit/s need addition and multiplication, but not division." In other words, architectural mode is concerned with the broad functionality of the system.

Modelling this type of conceptual process is an open problem in artificial intelligence, and beyond the scope of this research, which is concerned with less abstract modes. However the very fluidity of architectural simulation presents a major challenge to the lower levels in abstraction— which must be highly expressive and variable.

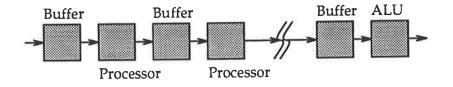

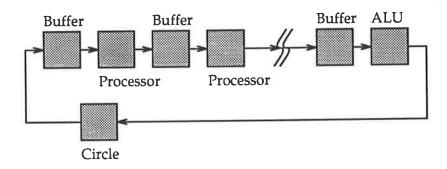

#### 2.2.2 Structural

Structural level is the point of abstraction where a hierarchy of specific modules are decided upon, and function assigned to them. Connectivity between modules is also a structural issue. A module corresponds to the classical engineering idea of the black box— its function and connections are known, but details of its internals are hidden, or equivalently to use of the technique of information hiding. Methodologies for partitioning have been discussed at length in both computer science [Yourdon+75] and circuit design contexts [Mead+80], in particular with respect to the top-down style of design.

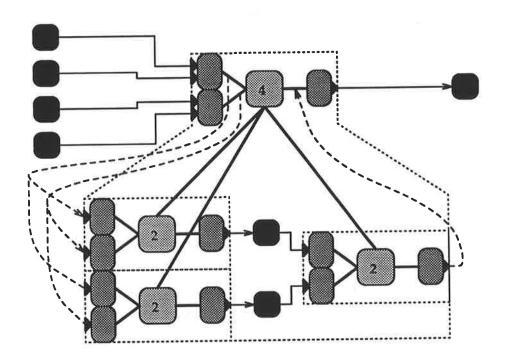

Figure 2.2: Structural Decomposition

Describing a structural decomposition as a simulation mode may appear initially to be rather odd. The justification is this—given that there exist more specific modes, it is possible to simulate a module which contains submodules as the aggregation of the simulations of its submodules in their various modes.

#### 2.2.3 Functional

Functional mode is often known perhaps more descriptively, as behavioural or algorithmic mode. This stage deals with detailed specification of the behaviour of each module.

In developing a multi-mode simulator, functional mode is probably the point at which the greatest "design stress" occurs. On the one hand, it is desirable that the functional description to be simple, elegant, easily comprehendable, and short— attempting to match the architectural abstraction in the designer's mind. On the other hand, it is necessary that the functional mode be able to adequately duplicate all the special case conditions of lower level simulation modes or the technologies that they model. Where the line between these two requirements should be drawn is always likely to vary from design to design— it is to be hoped that both aims are not totally mutually exclusive. The approach eventually taken here is reminiscent of the spirit used in the development of the X Windowing System [Scheifler+86]—to provide functionality but to avoid dictating policy, as summarized by the dictum "Tools not Rules".

It is natural to develop functional descriptions for modules derived from the structural decomposition. Cases where the structural hierarchy (chosen for the purposes of construction) and the functional hierarchy (chosen for the purposes of simulation) are not well matched are rare, and indeed in the field of VLSI such a situation would tend to be viewed as an act of perversity on the part of the designer ([Sussman+80] discusses a system for handling non-isomorphic hierarchies). Because of this close relationship these two modes will be considered together from here on.

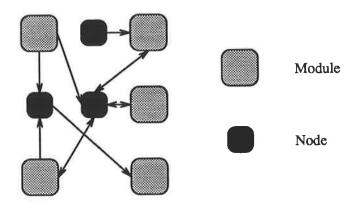

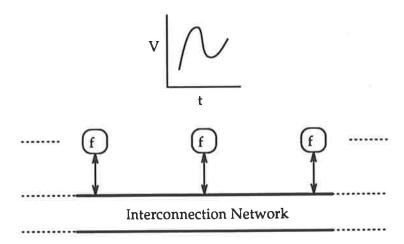

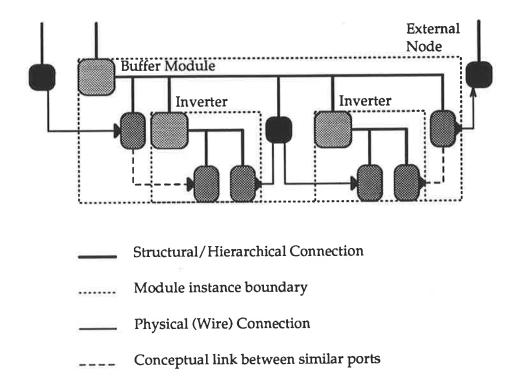

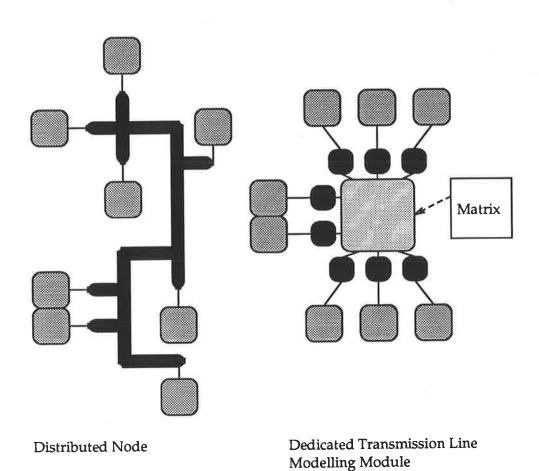

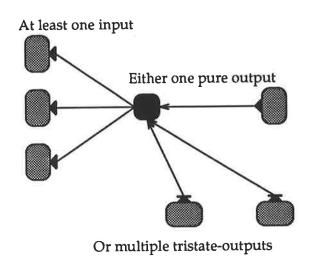

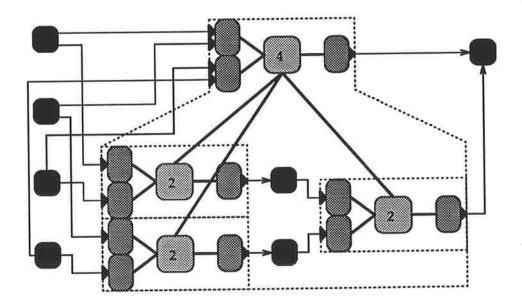

The functional level introduces the question of communication between modules. In most cases there is no better solution than to directly model reality, and provide communication with nodes. Every distinct connection between at least two modules defines a node. Each node has an associated value, which may be accessed or modified in various ways by the modules connected to it, depending on the structure and/or function of the module—see figure 2.3. Links between modules and nodes may be directional.

Figure 2.3: Modules and Nodes

Alternately one may think of the nodes as registers— which gives rise to a specific submode commonly known as Register Transfer Level (RTL). RTL is a subset of functional level as RTL-mode modules typically perform only Read and Write operations on the nodes. A fully general functional mode may plausibly define arbitrarily many other types of interactions.

# 2.2.4 Digital

The general digital model makes the characteristic assumption that the nodes take on a highly constrained set of values—"High" and "Low" or Hi/Lo or 1/0, in the purest form of the digital abstraction. This is a highly efficient choice for systems whose function is easily expressed in terms of boolean

logic— hence the common but imprecise use of the term Logic simulation.

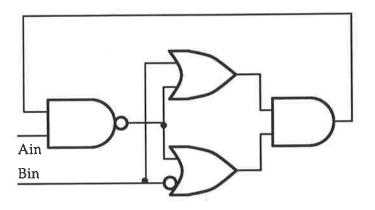

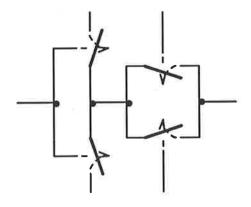

Starting from this basic abstraction, much variation is possible. One of the most common extensions is to allow a third value (often called X) which indicates that the node is in an intermediate state between Hi and Lo— in support of the threshold voltages defined for logic families such as TTL. A well known submode is gate-level simulation, in which the system is dominated by simple logic gates. Another submode is switch-level simulation, where decomposition has reached the underlying devices which are simulated as switches.

Figure 2.4: Gate Level

# 2.2.5 Analog

Analog modes abandon the abstraction of the digital model, and deal in continuous quantities. By this stage of modelling accuracy one is dealing with real voltages, currents, resistances and capacitances, rather than an abstract concept of "value". Similarly, the modular decomposition has progressed down to the raw devices. Common terms for this level are circuit and timing

Figure 2.5: Switch Level

mode.

Diversity of features within analog mode is large. Physical devices have many varied and interesting special case modes of behaviour, resulting in a busy and productive field of research. In the literature one senses a drive towards ever greater modelling accuracy competing against a desire for simple computationally efficient models. At the extreme end of the scale, the horizon collapses to the size of a single device—

#### **2.2.6** Device

—leading to the esoteric field of device simulation. Here the engineer and computer scientist give way to the physicist, and consideration of the overall system is lost, therefore device simulation is beyond the scope of this thesis. A related area is *process* simulation, where the input to the simulator is in terms of fabrication equipment parameters, and the output is the device characteristics required by a device simulator.

## 2.2.7 Timing

Apart from referring to a type of analog simulation, the word timing is attached to the mode of simulation best described as Timing (or Delay) Analysis. In this mode, the object is to determine delays along signal carrying paths within the system without recourse to complete knowledge of node values. Given a mode-specific algorithm to determine delay, Timing Analysis can interface to Functional through Analog modes, and is thus orthogonal to the main mode hierarchy.

#### 2.2.8 Fault

Fault simulation is likewise orthogonal. This is another rich field that studies the effects of errors in a system and how to minimize or efficiently test for them. While fault simulation primitives could be added to Loge<sup>1</sup> they have been omitted for the time being, as has detailed consideration of the fault simulation literature.

# 2.2.9 Mixed and Hybrid

Many simulators are said to be mixed mode. The common meaning of this is that they are capable of simulating individual modules in different modes. In some cases, however, the use of the term "mixed" is intended to imply the use of a mode that contains features from two other common modes (for example, a mode that reports only digital values, but which uses an internal analog representation). Such modes are better described as hybrid. One must observe that while many excellent individual modes exist, the problem of cleanly interfacing Functional, Digital and Analog modes has rarely if at

<sup>&</sup>lt;sup>1</sup>A node controllability/observability statistic generator is a future project.

all been achieved with elegance.

Design for Multiple interchangeable modes

(1)

# 2.3 Functional and Structural Modes

#### 2.3.1 Introduction

It is difficult to say what is the first instance of functional simulation of integrated circuits. Is a subroutine library for a common high level language sufficient? Or the capability to build "macros" of simple AND/OR type gates into larger groupings within a simple gate-level boolean evaluator? Progress in functional simulation has been incremental, but growing steadily in ambitiousness with advances in programming language design and computing capacity. The origin of structural mode simulation is similarly obscure.

Does functional simulation justify its existence? Or, to quote the seminal [Szygenda<sup>+</sup>73]—

The past work on functional simulation can be characterized as generally inadequate. Questions, such as: "Can functional simulation accurately reproduce circuit behaviour?", "Is there any savings realized, in time and storage, when using functional simulation?", or "Can we have gate-level and functional descriptions of a module and interchange them during simulation?" have not been answered.

One would hope that nearly two decades later we are in a position to answer these questions. Sadly however, while it is fairly clear that there are real benefits available from functional simulation, and that systems exist that allow on-the-fly interchange of simulation modes, the question of accuracy is still open amongst some commentators—notably amongst critics of VHDL.

(2)

# 2.3.2 Hardware Description Languages

The central focus in functional and structural simulation is on the representation language or languages— the *Hardware Description Language* (HDL). An important design choice immediately arises— either to develop a special purpose circuit modelling language (as indeed appears in [Szygenda<sup>+</sup>73]), or to embed simulation capability into an existing language, as in [Hill<sup>+</sup>79] where the *base language* was Pascal.

What are the tradeoffs? Special purpose languages allow the developer to retain tight control of language features, they can be carefully optimized for the simulation task and avoid excess syntactic or executional baggage, but must be built from scratch. On the other hand, embedded languages are often easier to develop and write models with, since a rich existing framework is already provided.

Embedded simulation languages are typically implemented with a preprocessor that emits base language code, which is linked with a special purpose library— thus compilation and linking may take significant time, and executable code may be large. Alternately, either type of language may be interpreted— trading speed for flexibility or ease of implementation and extension. Indeed there is a continuum between pure compiled and interpreted approaches— an example of an intermediate case is [Armstrong+81] and [Armstrong84] in which functional behaviour is described in an assembly language (GSPASM), which is compiled into a microcode form, to be interpreted by the simulator.

Some simulators are of such scope as to allow both approaches— an especially obliging system appears in [Doshi+84] which supports both a specific

RTL, and functional models in C, Fortran, Pascal and PL/1! The external language models must of course be compiled, but the RTL is semi-compiled to an interpreted RPN form—giving considerable freedom of choice to its users.

Compiling an entire system is tedious, and makes the addition of new modules rather a chore. In FUNSIM [Des Marias+82] some work is saved by implementing dynamic loading of compiled module object code. The language FML is difficult to categorize as either special purpose or FORTRAN-embedded, as the intent appears to be that native FML constructs be used almost exclusively, despite FORTRAN code being produced as an intermediate step.

Language theorists have commented on the phenomenon whereby language may affect thought processes. A facetious computer-language illustration of which is to recast the proverb "When all you have is a hammer, everything looks like a nail." as "When all you have is FORTRAN, everything looks like an array." The relevance of this to functional simulation is in highlighting a pitfall of embedded languages— does the base language constrain the thinking of the implementor (and thus the functionality of the simulation system), and/or the process of developing functional models? [Pilotny+82] describes the CONLAN project—in which a family of languages are derived from Standard Pascal. The adequacy or otherwise of Standard Pascal for general purpose programming has been a source of controversy—in the case of CONLAN one is left with the impression that something of a struggle with the limitations of Pascal occurred. [Maissel+82] is a similar case, using APL.

Real hardware is inherently parallel, thus for uniprocessor simulation a non-procedural language could be thought to be a natural choice, as for example in [Sakuma+83]. Another example is [Brown+83], for which the functional

specification is rule-based, supporting an exploratory style of development at the expense of performance.

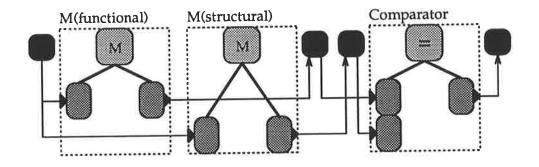

An even more appropriate choice of software technology for functional and structural simulation is object-oriented design [Booch90]. The most important decisions in the use of object-oriented design is the choice of the object partitioning. In the case of functional simulation, a one-to-one correspondence between the module hierarchy and the object partitioning is an easy, natural solution. A fine example of this style is [Lathrop+85] (with some extra objects, such as buses). This functional simulator shows considerable generality, largely derived from the base language (Lisp/Flavors [Weinreb+81]). A notable feature is the use of versional blocks—several versions of the same module, which receive the same input, and whose outputs are compared to detect errors or modelling inconsistencies (an approach familiar from fault-tolerance/reliability). [Wolf89] is a similar system where object-oriented Lisp was used in prototyping, as preparation for a C++ production version.

No survey of functional simulation can credibly avoid mention of VHDL [Lipsett+86], [Shahdad86], [Ins88]. This U.S. Department of Defence backed HDL will doubtless become the standard that it is intended to be, which is certainly desirable for reducing fragmentation and isolation amongst the development community. The technical merits of VHDL (as a whole or individual features thereof) have been hotly debated by many experts, however it is revealing that it has been criticized both for being too closely associated with Ada, and also for not including enough Ada features [Nash+86]. Certainly VHDL does not lack features in comparison with other HDL/simulator systems of its vintage [Aylor+86]. One can not help feeling that having gone a long way along the road to Ada that it was regrettable for the design of VHDL that it stops short of full integration therein. Similarly, proponents

of small languages criticize VHDL for creeping featurism, which is at least partially attributable to the influence of the large Ada language.

More detailed discussion of the implications of various base languages can be found in [Katzenelson+86] which compares the use of Pascal, Simula, CLU, and Enhanced C as hosts. Overall it appears that there is pressure to provide an expressive and powerful HDL, and that the more power there exists in a base language, the easier the embedding process and the development of models.

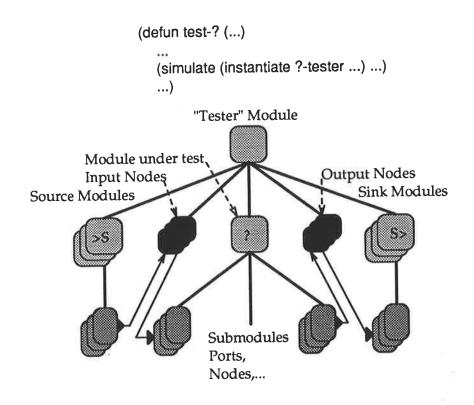

Having provided the HDL to define the system, there is still a requirement for a means of controlling a simulation of it. This control language is often built into the functional HDL, or relegated to a one-off command line interpreter type interface. This is a minor point, however [Terman83] comments positively on the utility of having a powerful language (Lisp) with which to write test programs and directly process results.

As a note of caution, one must not become distracted by the intricacies of HDLs from the fact that they are merely a means to an end. Perhaps the most important design criterion for an HDL is that it be easy to read and write.

# 2.3.3 Low Level Modelling

A subsidiary concern of functional simulation is its provision for detailed modelling of low level effects. This issue is sometimes deliberately ignored in published systems— for if a rigid top-down design style is assumed then the functional level has no theoretical reason to model small scale behaviour. Regrettably however, if a higher level mode provides excessively coarse models

with respect to the next level down, verifying the equivalence of two representations at these levels is severely complicated. One must beware of allowing the simulator to dictate methodological policy.

Taking the remarks above to the extreme, it would be desirable for all modes to be closely integrated, allowing faithful comparison of equivalent designs in arbitrary modes. The specific practical upshot of which is—high-level modes like functional mode must interface cleanly to the very lowest-level modes, such as analog mode. This requirement strongly suggests a common communication strategy is required.

Design for Clean interfacing between all modes (5)

Modules interact by communication through nodes. Nodes driven by an analog mode will contain analog voltage waveforms. How then do functional modes deal with analog waveforms read from their input nodes? As functional modes usually make the digital assumptions, analog inputs are converted to digital levels by thresholding. Well behaved implementations attempt the courtesy of returning non-trivial analog outputs (for example by providing an exponential waveform spanning a change in logic level), but many simply convert logic outputs directly back to analog levels, resulting in a discontinuous signal. Assumption of the digital model for functional simulation has potential implementational benefits such as high level abstraction of module input/output ports as integer-valued variables, reduction in code complexity, and reduction in storage requirements. On the debit side, the ability to model unusual or explicitly analog modules (for example a senseamplifier such as appears in a well known static RAM design ([Weste+85], page 364), has been lost. Ideally, one would hope that both types of behaviour were available.

Given that some scheme has been devised to convert between time varying analog quantities and discrete digital changes, one must consider the timing of digital outputs— how long from change of input does it take to produce output? Once again there are various approaches— in FML [Des Marias+82] delays are assignable with constructs such as—

#### WHEN CLOCK RISES MAKE A = A + 1 WITHIN 10 NSEC;

Similar notations abound, such as in [Foyster86].

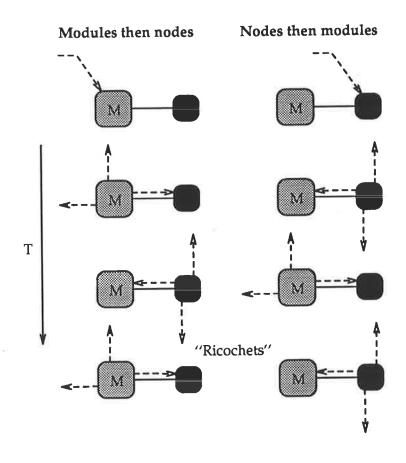

Another approach is to make delay a property of the links between modules (especially in systems that assume top-down design). There is wonderful potential for chaos here if links are allowed to have zero (or negative!) delay. A zero delay link between the terminals of an inverter is the functional simulation equivalent of an infinite loop. In defence of the decision to allow zero delay links, [Lathrop+85] states "It is possible to write an infinite loop in any programming language..." Despite this hazard, in a purely prototyping situation with no catastrophic positive feedback, universal use of non-delaying links is analogous to the situation within common clocked systems where the clock phase changes, much circuit activity follows, eventually stabilizing before the next clock cycle. In this situation a link is effectively a contract that modules can perform arbitrary amounts of communication and stabilize within single clock cycles. Such omissions may be acceptable in early stages of development to avoid the overhead and trouble of making the clock control explicit. A similar case occurs where all delays are unitary, which implies synchronous communication between neighbouring modules.

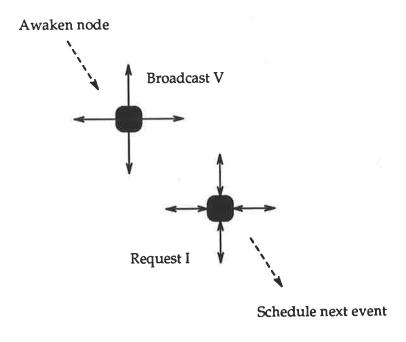

Because digital transitions can be said to occur at a specific time instant, they are often referred to as events or messages. Highly efficient simulation can be achieved within a message-passing paradigm. Unfortunately, there are some serious traps hidden in the semantics of event scheduling and delivery, which are clearly explained in [Luckham<sup>+</sup>86] from which the following

example is drawn.

Design for

$$Speed \Rightarrow event \ driven \ simulation$$

(6)

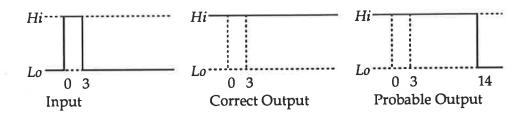

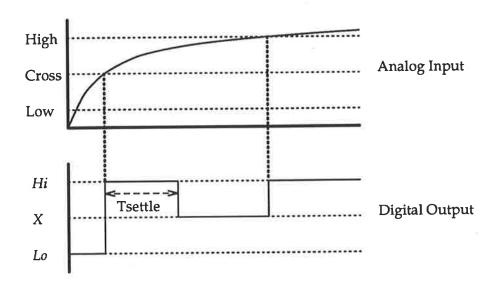

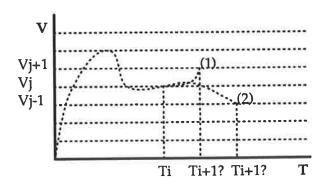

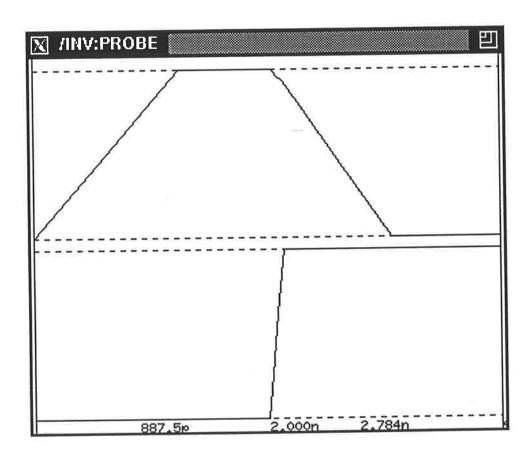

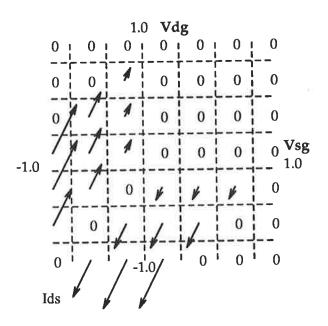

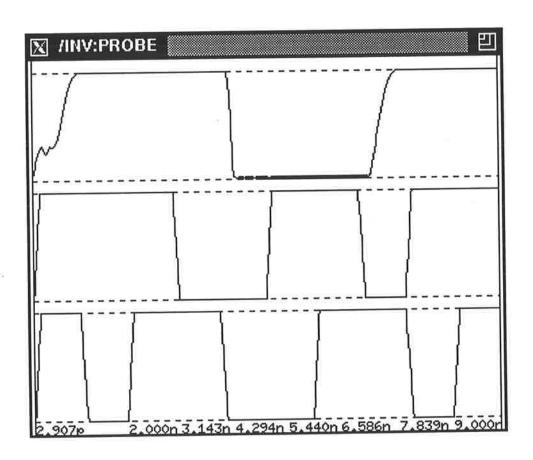

Consider a digital inverter, with  $Lo \to Hi$  delay of 10ns,  $Hi \to Lo$  delay of 14ns. If it receives a pulse of width 3ns, the correct pure digital behaviour would be for the output to remain Hi as the  $Hi \to Lo$  transition will not complete before the inverter is driven Hi again. In event driven terms, two events will be generated from the input events— Output  $\to Lo$  at  $t = t_0 + 14$  and Output  $\to Hi$  at  $t = t_0 + 3 + 10$ . With a simple minded event scheduler that merely executes events in time order, these events will become transposed resulting in a erroneous final output state of Lo— as shown in figure 2.6.

Figure 2.6: Event Scheduling

To prevent events "catching-up" like this, the scheduler must adopt preemptive semantics— when an event for a particular node is scheduled for a time  $t_i$ , then if there are other event/s scheduled for that node at time/s  $t_j$ where  $t_i < t_j$  then the later events are preempted (that is, cancelled). Sadly this approach while safe, may be unnecessarily pessimistic— the cancelled event/s may actually have been quite correct. In particular, preemption constrains functional descriptions to generate events in strict chronological order, which may be an unnatural restriction.

The compromise presented in [Luckham<sup>+</sup>86] is to qualify the event transition over an interval, for example—

```

when inport=low =>

outport := high after 10;

when inport=high during 4 =>

outport := low after 10;

```

—protecting the simulator from generating a transition to Lo unless sufficient time has passed that no transition to Hi could preempt it.

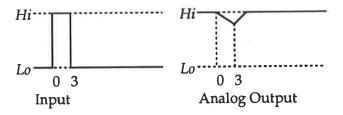

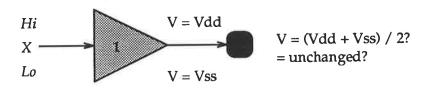

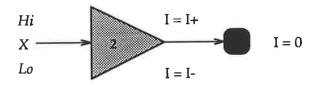

The solution above is quite sensible, but one wonders whether it was worth the effort. The source of the event catchup problem is the attempt to enforce the strict digital model. If the functional mode was capable of analog output, the events could be directly scheduled in time order, with the result shown in figure 2.7. Thus both an event scheduling problem and an interfacing problem can be simplified by introducing the design criterion—

Design for Communication with analog voltages (7)

Figure 2.7: Analog Event Scheduling

An impressive approach to the modelling of digital events in time appears in [Heydemann+88]. Here the use of a rigorous mathematical formalism allows high efficiency modelling of modules as state-machines, with achieved performance of the order of 50,000 events/second per MIPS.

### 2.3.4 Timing Analysis

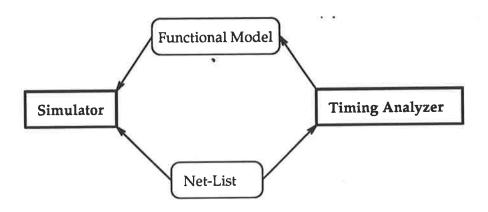

It is appropriate at this point to consider the subfield of timing analysis. The goal of timing analyzers is to estimate the propagation time of a signal through some network, which in the general case can include diverse elements such as raw devices through logic gates up to behavioural models covering the spectrum of circuit simulation primitives. Timing analysis is a useful adjunct to analog simulation, particularly as a tool for directing performance optimization, however another important application is in hoisting the abstraction level of a circuit, (especially from out of the analog domain and into the digital)— the analyzer is run to estimate the delays that characterize a low-level network, the results of which are then used in an explicit delay specification at a higher abstraction level (figure 2.8). This methodology is strongly advocated in [Newton81]. Of course, overall performance of a high level system with specified delays is also of interest— an early example is [McWilliams80] which analyzes synchronous clocked systems of logic gates and blocks with assigned delays. Practical experience gleaned from [Elder+84] suggests that good delay estimation tools, applied from the start of the design cycle result in swifter delivery of systems performing to specification.

In general terms, timing analyzers must enumerate paths through the system under test, looking for the critical path between a specified input event and the arrival of its consequent outputs. Clearly, circuits with large branching (and reconnect) complexities will exhibit swift growth in the number of paths with respect to circuit size, making exhaustive enumeration costly. The review [Hitchcock82] notes this fact, and suggests that the user should guide the search by labelling paths with tags such as "critical", "marginal", "normal" and "trivial". Alternately, [Nomura+82] argues that excessive searching

Figure 2.8: The Role of Timing Analysis

can be avoided with reference to the hierarchical structure of the system—for example to avoid checking several instances of bitwise equivalent paths [Jouppi83a].

A practical point made in [Bening<sup>+</sup>82] is that just finding the one worst path is probably a wasteful approach— a more useful form of output would be the N worst paths in the system, with the ability to mark paths for omission once the user is satisfied that no further improvement can be made on them. Another concern is that there are other statistics of interest apart from just "maximum time to traverse a path"— the average time, and the minimum time are as relevant if one wishes to check clock skew— see [Dagenais<sup>+</sup>86] for an implementation. A potential time saving measure is rather than analyzing for path delays, attempt to prove that minimum clock periods and duty cycles are met ([Cherry88])— allowing early termination on violation.

As usual, feedback configurations are a complication. The immediate practical question is how does one avoid looping when there are cycles between inputs and outputs? The easy detection of cycles has been cited as a reason for using a depth-first search for path enumeration [Agrawal82].

However if the number of cycles is small, depth-first search may be slower then breadth-first search, which in the seminal TV [Jouppi83a], [Jouppi83b] is projected to be linear in the number of devices. This is a controversial point, as another influential timing analyzer, Crystal [Ousterhout83], uses depth-first on the grounds that the paths are short, thus backtracking is nominal and justified by the algorithmic simplifications.

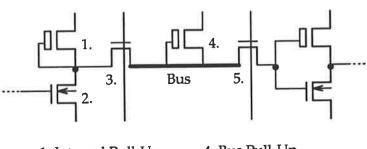

Perhaps as a consequence of breadth-first searching, TV includes much analysis of the circuit with the aim of finding the purpose of each device—see figure 2.9. With such knowledge and the assumption that devices have unidirectional information flow, many invalid paths can be eliminated from consideration. In [Jouppi87], this analysis reaches an impressive accuracy of around 99.9%.

- Internal Pull-Up

Internal Pull-Down

- 4. Bus Pull-Up

- 2. Internation

- 5. Input Latch

- 3. Bus Pull-Down

Figure 2.9: TV Device Labelling

The important result in Crystal, is introduction of delay sensitivity to the shape of the input signal and its interaction with loading effects (in detail in [Ousterhout85]). The Crystal model is refined in [Matson85] where the consequences of different sized devices are included, and further in [Hwang+86], and again in [Overhauser+88] which allows for dynamic loads (nodes that are

partially charged, overlapping inputs, etc). The delay analysis methods in Crystal have been used to extract circuit parameters from SPICE waveforms [Rathmell86].

It is well known that many technologies show different delay characteristics for rising and falling signals. For a complete analysis then, a separate accounting must be kept of delays for a rising input and a falling one. Furthermore, given the system under test contains objects such as functional mode modules or gates, the "unateness" (the inversion characteristics) of these objects must be known [Ng+81].

Like other modes, timing analysis has tracked technological development, changing focus from gates to devices— a typical timing analyzer allows user specified block delays, and includes an RC-tree model— for example [Murphy+85]. Accurate models of gates appear in [Okazaki+83], [Etiemble+84] with the specific case of inverters treated in [Sakurai88]. Much work on RC-tree analysis has occurred, flowing from the seminal [Penfield+81] and its refinement [Rubinstein+83], which present useful upper and lower bounds on delay for RC networks. Refinements such as [Chu+87] (for charged shared networks) and [Martin+88] (cyclic networks) continue to appear, but are showing a trend towards accuracy at the expense of computation time. This trend appears likely to be unavoidable in the case of very fast systems—where large buses begin to resemble transmission lines rather than simple nodes or wires. A simple, efficient transmission line model is a difficult problem—see [Canright86].

The explicit split between RC-tree (or general low level element) and high level block models is a blemish that may weaken timing analyzer performance. Attempts to unify these submodes appear in [Brocco+88] and [Wallace+88]— a very general system with no explicit notion of time or delay.

An important theoretical paper is [Lin<sup>+</sup>84], which details a general and comprehensive model for delays through a system of two-port modules characterized by parameters R (series resistance), C (total capacitance), D (internal delay), Q (stored charge), D\* (internal delay due to stored charge), and how this extends to the general RC tree case. Notably, the rules for combining the parameters of characterized modules imply that it is possible to continue to rise up through the structural hierarchy, accumulating delay information.

Thus to summarize, timing analysis is a useful simulation tool applicable to the main primitive elements found in digital systems. Good estimates of average, upper and lower bounds on delay times through a system can be found. These estimates are useful in the development of higher level models, which provides justification for the delay modelling system used in many functional and gate-level simulators.

#### 2.3.5 Goals

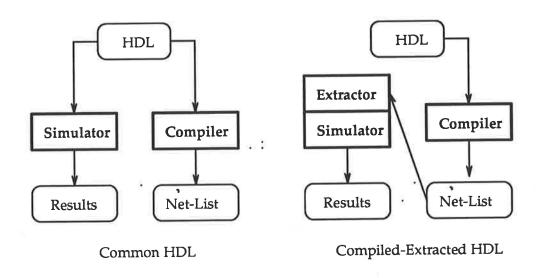

Some mention must be made of the goal of automatically synthesizing hardware from a functional description—the point where simulation and compilation meet. Silicon compilation, and general hardware synthesis (for example [McFarland86]) are busy fields in both research and development, and deservedly so. Possibly the most desirable development in VLSI design tools would be a system in which a single high level description can be both reliably compiled to hardware and subject to simulation that adequately reflects the behaviour the compiled version, rather than the more conventional case where the simulator operates on an extraction of the compiled hardware— see figure 2.10. Such systems are considered unlikely to appear for at least another two years according to [Murphy90]. The reverse operation of "decompiling"

a hardware description into a functional description ([Blaauw<sup>+</sup>89]) appears to be more immediately tractable, especially for simple boolean modules and cases where regularity and/or hierarchy can be detected and exploited.

Figure 2.10: Simulation and Compilation

## 2.4 Digital Modes

#### 2.4.1 Introduction

Anyone attempting to generate random numbers by deterministic means is, of course, living in a state of sin.

- John Von Neumann

Digital simulation of integrated circuits began in earnest at roughly the same time as the introduction of TTL. See [Seshu+62] for a venerable example. From the start, the digital simulation literature has been dominated by

attempts to broaden the digital model to faithfully handle special cases, the most prominent of which are unknown states, delays, bidirectionality and feedback. It appears that adopting the digital assumptions is something of a state of sin similar to the use of pseudo-random numbers.

The development of the field is clearly documented in review papers such as [Bening79], [Ruehli81], [Breuer+81], [d'Abreu85] (gate-level), [Smith86], [Bryant87a] (switch-level), and [Soulé+88] (parallel algorithms). For an example of an early seminal system, see [Szygenda72]. [Breuer+81] observes a notable feature of logic simulators— the steady proliferation of logic states and strengths.

There is something of a discontinuity between gate and switch level simulators—simulation of gates whose inputs uniquely determine their outputs is inherently simpler than simulation of devices which (being modelled as switches) may either connect or disconnect nodes. The heart of the problem is that the direction of flow of information across a switch is ambiguous.

## 2.4.2 Logic States

A circuit consisting of logic gates connected such that no two gate's outputs are connected together and with no cyclic connections, can be adequately simulated using the pure digital model of node values being either High or Low. Breaking the non-cyclic connection requirement allows unstable positive feedback as mentioned previously, but more importantly it allows the creation of a simple static memory element— the flip-flop. Once flip-flops are present, the question arises as to what their initial state is— the unsatisfactory nature of assigning either Hi or Lo to such nodes lead to the introduction of an "Unknown" state— often abbreviated U, or I specifically for unknown initial states (as in [Hirakawa<sup>+</sup>82]), or X.

Similarly, if outputs of gates may be connected, the possibility exists that two such gates will attempt to drive in opposite directions—creating another use for the unknown state, or perhaps even a distinct conflict state. Usually though, these different distinct motivations for separate states are combined, leaving the states Hi, Lo and X—the  $Ternary\ Logic$  model.

Introducing a new state requires consideration of its semantics as an input. In gate-oriented systems this is fairly clear— for example a two input AND gate with an unknown input will have unknown output unless the other input is Lo. Nevertheless, [Breuer72] presents a telling example where the semantics of a specific X state is sufficiently different from "either Hi or Lo" such that erroneous simulation would occur. The same example is still likely to cause recent digital simulators problems. Fortunately this evidence of the theoretical inadequacy of the digital model is not a serious practical difficulty— the problem of unknown initial states can be trivially avoided by assigning all initial states to a specific value (probably requiring more effort from the designer). Alternately, if the system under test is designed sufficiently robustly, X states may be tolerated during simulation, but their continued presence at the end of the test (or at important checkpoints such as the end of a clock period) can be considered as evidence of a design error—this is in fact a useful test.

Thus the X state is a relatively benign addition to a gate-level simulator. Its impact on the simulation of switch-like networks of transistors is rather more severe. Firstly, X is much more likely to be generated since Hi and Lo node values collide more frequently in transistor networks (often by design). Secondly, the implications of a X on a MOSFET gate node is much less obvious than for logic gates. Thirdly, no simple conflict resolution strategy exists—when an X is connected to a Hi or Lo, there are two obvious choices, either ignore the X (which is hopelessly optimistic) or allow the X to over-

ride the other value (which has the disasterous property of "polluting" the system with unwanted X states). These difficulties can be resolved only by complicating the digital model further— for example [Flake+83] uses a fifteen state logic algebra with the specific goal of arresting pessimistic propagation of X states.

Further criticism appears in [Bryant84], where the practice of assigning X to unknown initial nodes is deprecated for not obeying the Law of the Excluded Middle to which real systems are subject. In [Stevens+83] a practical attempt to improve this practice is made—the initial system is labelled with two special tagged X values which retain inversion information (that is, if one type of X is the input to an inverter, the other type will be placed on its output)—thus whole strings of X states may be removed if any one of them is identified (this is a simple example of the use of symbolic simulation [Bryant90]). Useful though this heuristic may be, Bryant remarks further that rigorous modelling of a valid-but-unknown state is equivalent to the problem of boolean satisfiability— an  $\mathcal{NP}$  complete problem [Chang+87]. The  $\mathcal{NP}$  completeness property provides a strong motivation for the use of higher level descriptions—see [Chandra+89].

A common idiom in digital design is the use of a bus to allow read/write communication between several modules. Each module with write capability must be able to "disconnect" itself from the bus <sup>2</sup>— or more precisely to set its bus connection to a sufficiently high impedance so as to pass negligible current. With additional control logic it is possible to design well-behaved systems wherein only one module at a time attempts to write to the bus. When simulating such systems it is highly desirable to distinguish cases where two or more modules are contending for the bus from the case where a single

<sup>&</sup>lt;sup>2</sup>Commonly known as the tristate condition.

module is overwriting the data placed on the bus by a previous module which has relinquished its connection. Another issue is that if the bus data is not written for some time it may decay and become unreliable. These concerns lead to the introduction of the Z or High Impedance state, to be used for nodes that are "undriven", as for example in [McDermott82].

Z exists in various forms—

- As a transistor state. An "off" transistor is sometimes labelled Z.

- As a value specifically for decayed undriven nodes.

- In three subforms, Z0, Z1, ZX indicating a node with a particular logic value which is qualified as undriven.

The semantics of a basic Z are similar to its unqualified form X. For the more precise model with Z[01X], these state's semantics are similar to their unqualified forms.<sup>3</sup> In both cases the difference is that driven forms take precedence over undriven forms. One could say that the driven forms have greater strength.

Some other states have been proposed— for example [Jea $^+79$ ] includes U and D for nodes undergoing upward and downward transitions respectively. These have in general not found much favour as they introduce more complexity than they return in improved fidelity of modelling.

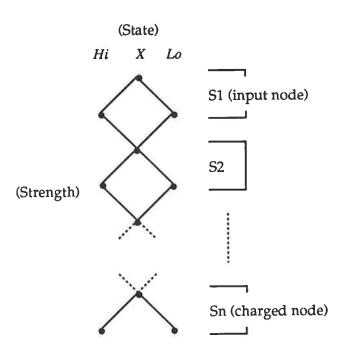

## 2.4.3 Logic Strengths

The previous section on logic states showed how the various Z states were introduced to handle cases where correct operation of a system could be achieved if some states were considered stronger than others. In fact, there

<sup>&</sup>lt;sup>3</sup>The plain Z is equivalent to ZX

is no real reason to consider Z et al as logic states, but rather to return to the earlier Hi, Lo and X logic state space, with an independent strength attribute.

Strength has a more important use than for high impedance modelling. Returning to the question of the X state, it is clear that generation and propagation of X conditions will be reduced by using multiple strengths—since many logic state conflicts will be resolved by a difference in strength. Notably in the case of nMOS networks, multiple strengths are necessary to have any hope at all of successful simulation.

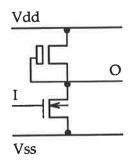

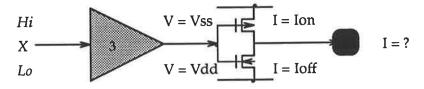

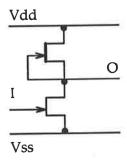

Figure 2.11: nMOS Inverter

For the simple nMOS inverter of figure 2.11, the upper "pull-up" device (depletion mode FET) is always "On", continually driving the output node to Hi. Without a strength model, the lower "pull-down" device (n-type enhancement mode FET) will be unable to change the output to anything but X. If however the depletion mode device is considered to propagate a "weaker" Hi than the Lo propagated by the enhancement mode device, then the inverter can be adequately modelled.

The example of the nMOS inverter illustrates the physical significance of the strength abstraction. The strength of a logic state is a measure of

the current driving capacity supporting the logic value of the node. An undriven bus has no supporting current maintaining its state, therefore it has the minimum strength. An externally supplied voltage rail has a probably unknown but presumably very large supporting current capacity, giving it a very high strength.

Node strength then is either an implicit property of a node (in the case of voltage rails, and perhaps other external connections), or derived from the device/s connected to the node. Indeed it appears that devices too have strength. Some quantitative modelling of device strength is necessary to clarify situations where several devices are competing— supposing the nMOS inverter had another pull-up in parallel with its existing one— are their combined strengths sufficient to overcome the pull-down? This leads to the complication of different device sizings— in the case of MOSFETs identical parallel devices are logically equivalent to a single device with gate region width to length ratio equal to the sum of the ratios of the original devices.<sup>4</sup> In systems using ratioed logic there will be multiple device strengths present.

The difficult question about strengths that it asked of every digital simulator designer is— "How many strengths is enough for accurate modelling?". [Sangster+83] uses three, [Int87] four, [Stevens+83] five, [Hodgson84] seven, [Adler86] thirty-two. Axiomatically, given N+1 types of devices, each with different driving capacities, it is possible to construct a simple network that will defy accurate simulation by a simulator which can model up to N strengths. Here we have a theoretical objection to digital simulation with non-trivial practical implications. The simulator designer must make a choice for N, which can never be guaranteed to be completely adequate,

<sup>&</sup>lt;sup>4</sup>This is only approximately true, but adequately so for most purposes under digital simulation.

and which may even result in inefficient simulation if the bulk of simulated systems require significantly fewer distinct strengths.

Bryant estimates that for most circuits a mere two strengths are adequate [Bryant81b]. Nevertheless, the presence of ratioed logic is a justification for requiring arbitrary many devices of different current driving capacity. Another supporting complication is the property of some devices to propagate different logic states with different strength— for example an n-type enhancement MOSFET passes Lo well, but Hi in an attenuated form. Certainly, the general trend in reported simulator implementations has been for increasing numbers of strengths.

Little mention has been made so far of any systematic procedure for propagating logic states and strengths throughout a system. This was in deliberate attempt to evade consideration of certain problems, of which bidirectionality is the most dire. To delay this reckoning a little longer, assume that all devices have an unambiguous direction of information flow, or equivalently, that the sign of the difference in strength of the nodes on opposite sides of a switch can be determined by static analysis. As an example consider a simple CMOS Dynamic Shift Register Cell (figure 2.12), in which the devices can be unambiguously labelled as transferring information in one direction, (and often with an easily computable range of (state, strength) pairs).

This circuit could be trivially simulated by analyzing each device's gate input to determine whether it is conducting or not, and if conducting then propagating the source state to the drain state. There is however some ambiguity in strength propagation— does a device propagate the strength of the source node or its own strength or some combination thereof?

Figure 2.12: CMOS Dynamic Shift Register Cell

## 2.4.4 Digital Simulation Algebras

Several researchers have proposed algebras for modelling switch and gate level systems. [Brzozowski+79] is a general mathematical treatment of ternary logic, while [Jea+79] formulates the problem in terms of allowable state transitions. Hayes has been particularly influential in this area—with connector/switch/attenuator networks in [Hayes82], a detailed treatment of ternary logic with strengths in [Hayes86a], and with greater refinement in [Hayes86b] which allows for discretized node voltages and bidirectionality. General mathematical equivalence between various modelling techniques is shown in [Barros+83].

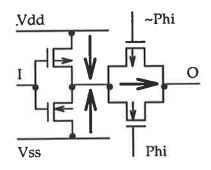

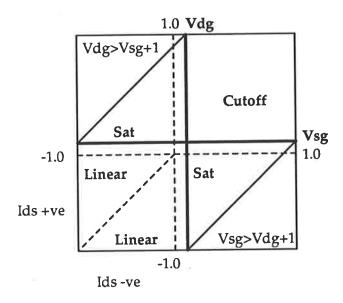

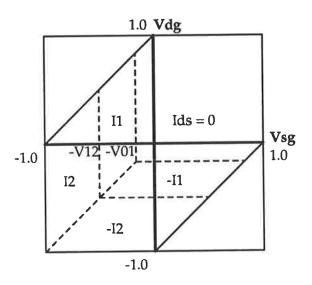

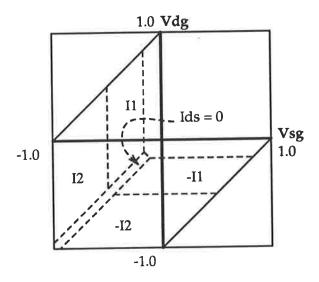

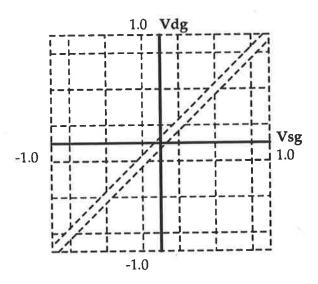

Particularly important papers in this field are those by Bryant, in which switch-level simulation was first given definitive form (with the simulator MOSSIM and its descendants). Bryant uses Hasse diagrams (figure 2.13) to define logic state and strength algebras [Bryant81a], [Bryant81b], [Bryant84]. The diagrams define a precedence of states and strengths, with collisions resolved using a least upper bound operation— for example nodes with same strength and different state generate X at the same strength, but where the strength differs, the corresponding state prevails.

Figure 2.13: Hasse diagram of an arbitrary strength logic algebra

## 2.5 Bidirectionality

One of Bryant's complaints about digital simulators is that they often artificially assign a direction of information flow to fundamentally bidirectional devices— see for example [Sherwood81]. Modelling bidirectionality has always caused trouble to simulators, and has given rise to complex special case solutions that are often inefficient. One of the better alternatives is seen in [Holt+81] which models bidirectional elements as two oppositely directed unidirectional elements— the resulting overhead is considered acceptable as it is asserted that true bidirectionality is rare in real systems.

MOSSIM is claimed to be more natural—devices are modelled purely as inherently bidirectional switches, which is a good match to MOS technology. Internally MOSSIM determines the strongest rooted path to each node—the

path through the network of switches and nodes with the greatest strength according to the strength algebra. No special case consideration of bidirectional effects is needed—however bidirectional configurations (DC connected devices/devices connected together source to drain) may require a number relaxation steps to stabilize.

MOSSIM was an impressive system, lending weight to the arguments of its supporting papers. Nevertheless, some subsequent work has continued to use unidirectional devices. An obvious reason is efficiency. Examples include [Sangster+83] (which has an explicit model for a common digital idiom—the "wired" bus), and [Almeida+84] which uses an eight-valued algebra in bidirectional areas which reduces to a five-valued case elsewhere, with bidirectional devices modelled as cross-coupled AND gates.

Similar to MOSSIM is [Stevens+83], where on an input event, a wave-front of change is propagated through the system, with wavefronts combined according to the least upper-bound algebra. Another MOSSIM derivative is [Adler86] which extends MOSSIM to handle stages driven by gate-level primitives, adds an RC delay model (requiring an event scheduler), and uses a thirty-two strength algebra.

[Dumlugöl+83] presents a system that takes the common step of partitioning the system into its DC groups. A strong O(n) relaxation algorithm is applied to produce a steady state configuration free of X states. This system is refined in [Dumlugöl+87] to perform the partitioning dynamically at boundaries defined by non-conducting devices. Special handling of feedback loops is required.

When considering the difficulty caused by bidirectionality and feedback, the question arises— "Are they worth supporting?" In [Ramachandran83] only well designed systems are considered— for which the control graphs must be acyclic in sections delimited by clocks (allowing explicit ordering of

the devices), and race conditions may not occur at any of the nodes (that is, data values may not vary with delay). In return for adopting this design discipline, the designer is promised a faster simulator with the ability to reliably detect hazards.

### 2.5.1 Delay Modelling

Digital mode shares many of the delay modelling concerns of functional mode, (mainly as both share the digital assumptions, but also due to the correspondence between a gate and a functional module). Delay models have often been added as an afterthought to existing simulators, with all the problems this approach implies.

Many delay systems have been proposed— [Jea+79] provides a range of delay services— zero or unit delay, rise/fall, min/max, min/max rise/fall (for instance, rise and fall times have distinct minima and maxima). A more electrically based, but thorough, case is [Hirakawa+82] in which the delay model includes handling of fanout.

[Bryant83] is a system for race detection. It makes the point that analog simulation does not show that a circuit will work correctly independent of delays. Delay sensitivity can be proven with a two-phase ternary logic simulation— in phase one all Hi or Lo to X transitions are performed, then in phase two all X to Hi or Lo transitions. If any X states remain a race is present.

#### 2.5.2 Other Features

In the absence of connecting themes, this discussion of digital simulators continues with an arbitrary collection of useful features. The list is by no means exhaustive. A miscellaneous paper is [Miyoshi+85], which details sev-

eral methods for speeding up gate-level simulators— such as merging gates, ignoring gates that can not change (equivalent to the constant propagation stage in an optimizing compiler), and using zero delay elements wherever it is safe to do so.

- Node discharge Nodes in MOS systems have the property of slowly discharging through the substrate. This effect is provided in [Sherwood81] via a "node time-out" event.

- Latency [Leinwand81] takes a high view of a system, considering localized "processes"— whereby events in different modules are isolated from each other (each module has its own event list and clock). This has the desirable properties of increasing locality of reference, reducing event queue operation overhead, and making the simulator more amenable to multiprocessor operation.

- Demand driven An alternate method of avoiding doing unnecessary work is given in [Smith+87], where requests for signal values are propagated backwards through the system— avoiding evaluating gates whose outputs are ignored. [Subramanian+90] is a recent system of this type adapted for multiprocessor operation.

- Flexibility It is undeniably desirable for there to be available some ability to vary the severity of modelling. [Hodgson84] for example allows several stages of algebraic complexity up to six-state seven-strength.

- Technological applicability In a rare departure from the dominance of MOS, [d'Abreu<sup>+</sup>84] is capable of handling bipolar devices.

- Analog compatibility In section 2.3.3 the event catchup problem was presented, with the simple solution of using analog waveforms. Diverse

systems such as [Jea<sup>+</sup>79] and [Schaefer85] use analog ramps to model transitions.