# High Performance RF CMOS VCOs for Wireless Communication

By

Tae Youn Kim

B.E. (EEE, Hons), The University of Adelaide, 2000

#### A Thesis

Submitted to the School of Electrical and Electronic Engineering in Fulfillment of the Requirements

for the Degree of

**Doctor of Philosophy**

Department of Electrical and Electronic Engineering

The University of Adelaide

Australia

<sup>©</sup>Copyright by Tae Youn Kim, October 2004

All rights reserved

Doctor of Philosophy (2004) (Electrical and Electronic Engineering) The University of Adelaide

Title: High Performance RF CMOS VCOs for Wireless Communication

Author: Tae Youn Kim, B.E. (EEE, Hons)

The University of Adelaide

Principal Supervisor: Chris Coleman

Associate Professor, Department of Electrical and Electronic Engineering

Co-Supervisors: Neil Weste

Adjunct Professor, Department of Electrical and Electronic Engineering

Ph.D. (The University of Adelaide)

B.Sc., B.E. (The University of Adelaide)

Andrew Adams

Principal RF Engineer, G2 Microsystems

Ph.D. (University of Leeds)

B.Sc. (University of Sydney)

B.E. (Hons) (University of Sydney

Number of Pages: 278

## **ABSTRACT**

This thesis is dedicated to develop a set of general and systematic techniques to design and produce high performance monolithic CMOS VCOs to use in modern wireless front-end chips.

In general, there are four topics covered in this research work. First, existing oscillator phase noise estimation theories are discussed. Some of these theories lead to simple and rough estimation of the phase noise, while some forms the basis for more complicated and accurate phase noise estimation performed by modern CAD tools.

Second, the operation and noise performance of a number of differential *LC* tuned VCO topologies are investigated in detail. Some common misconceptions associated with cross-coupled oscillators, including the incorrect linear oscillation amplitude expressions, nonexistence of a VCO bias region called voltage-limited region, and the non-apparent topological advantage of the complementary topology are addressed. Also, the noise sources associated with differential *LC* tuned VCOs are identified and investigated. Upconversion processes of low frequency flicker noise through various upconversion processes are discussed.

Third, based on the understandings acquired from the differential *LC* tuned oscillator analyses, a set of new optimization techniques is developed. These techniques allow for design of the best performing VCO realizable for a given process technology, chip area, and power budget. A new geometric monolithic planar spiral inductor optimization technique, an efficient way to trade between power consumption and phase

noise performance via L/C ratio scaling, appropriate sizing of the cross-coupled transistors, and a low-power, low-noise current biasing technique are among the VCO optimization techniques developed in this research work.

Lastly, the VCO optimization techniques developed are tested and validated by fabricating a number of VCOs using two different modern CMOS process technologies and analyzing their performances. The performances of these VCOs are then compared against the state-of-the-art monolithic VCOs reported in the literature. The comparison is not limited to CMOS VCOs, but extends to other competing process technologies such as bipolar technology. The comparison clearly shows the superiority of some of the VCOs designed and fabricated in this research work.

STATEMENT OF ORIGINALITY

I certify that to the best of my knowledge and belief, the thesis contains no

material previously published or written by another person, except where due reference

is made in the text and that the thesis has not been presented to any other University or

Institution.

Also, I give consent to this copy of my thesis, when deposited in the University

Library, being available for loan and photocopying.

Candidate Signature:

Date: 30 June 2005

V

## **ACKNOWLEDGMENTS**

It is my great pleasure to acknowledge the thoughtful guidance provided by my principal supervisor Professor, Christopher Coleman, and two Co-Supervisors, Professor Neil Weste and Dr. Andrew Adams, during the course of this thesis. They have provided me with the unique and valuable opportunity to pursuit my academic advancement. Without their persistent and careful supervision, assistance, encouragement, and feedback, this thesis would not have been completed.

I would like to thank Peregrine Semiconductor for the fabrication and design support of three test chips, especially the V.P. of Engineering of Peregrine Semiconductor, Dan Nobbe for his encouragement and support. Also, the support of Cadence Design Systems and Macquarie University in enabling the design of the three test chips fabricated through Peregrine Semiconductor is greatly appreciated.

Also, I am grateful to the former Wireless Networking Business Unit of Cisco Systems for providing me with the opportunity to work on their project and allowing me to publish some of the results acquired from the project.

I also would like to thank my colleagues, Dr. Jeffrey Harrison of G2 Microsystems and Dr. Said Al-Sarawi of Electrical & Electronic Engineering Department of the University of Adelaide for helpful discussions, feedback, and proofreading of the thesis.

Lastly, but not least, I would like to thank my parents and friends for their encouragement and continuing support in my academic pursuits.

# **TABLE OF CONTENTS**

| ABSTRACT                                  | III   |

|-------------------------------------------|-------|

| STATEMENT OF ORIGINALITY                  | V     |

| ACKNOWLEDGMENTS                           | VI    |

| TABLE OF CONTENTS                         | VII   |

| LIST OF FIGURES                           | XI    |

| LIST OF TABLES                            | XVII  |

| LIST OF ACRONYMS                          | XVIII |

| LIST OF SYMBOLS                           | ХХП   |

| LIST OF CONSTANTS                         | XXIVV |

| CHAPTER1: INTRODUCTION                    | 1     |

| 1.1 WIRELESS COMMUNICATIONS               | 1     |

| 1.2 MODERN RADIO TRANSCEIVER              | 2     |

| 1.2.1 Reciprocal Mixing                   | 4     |

| 1.2.2 OFDM and Phase Noise                | 7     |

| 1.3 VOLTAGE CONTROLLED OSCILLATORS        | 9     |

| 1.3.1 Monolithic CMOS VCOs                |       |

| 1.3.2 Current Monolithic VCO Performances | 14    |

| 1.4 OBJECTIVES                            | 15    |

| 1.5 SCOPES                                | 16    |

| 1.6 MAJOR CONTRIBUTIONS                   | 18    |

| 1.7 THESIS ORGANIZATION                   | 19    |

| CHPATER2: VCO PHASE NOISE                 | 22    |

| 1 1 INTRODUCTION                          | 22    |

| 2.2 PHASE NOISE                             | 24  |

|---------------------------------------------|-----|

| 2.3 LINEAR OSCILLATORS                      | 26  |

| 2.3.1 Linear LC Tuned Oscillator Analysis   | 28  |

| 2.3.2 Ring Oscillator Analysis              | 32  |

| 2.3.3 Limitations of the LTI Model          | 34  |

| 2.3.4 Figure of Merit                       | 34  |

| 2.4 NONLINEAR OSCILLATORS                   | 36  |

| 2.4.1 Linear Time-Varying Oscillator Model  | 38  |

| 2.4.2 Phase Noise Simulator                 | 42  |

| 2.4.3 Limitations of Simulator              | 44  |

| 2.5 CONCLUSIONS                             | 47  |

|                                             |     |

| CHAPTER3: DIFFERENTIAL LC TUNED OSCILLATORS | 49  |

| 3.1 INTRODUCTION                            | 49  |

| 3.2 CROSS-COUPLED OSCILLATORS               | 50  |

| 3.2.1 NMOS-Only Topology                    | 55  |

| 3.2.2 Other Cross-Coupled Topologies        | 70  |

| 3.3 FREQUENCY TUNING METHODS                | 76  |

| 3.3.1 Varactors                             | 77  |

| 3.3.2 Continuous Tuning                     | 88  |

| 3.3.3 Discrete Tuning                       | 91  |

| 3.4 PHASE NOISE SOURCES                     | 96  |

| 3.4.1 Passive Resonator Noise               | 98  |

| 3.4.2 Tail Transistor Noise                 | 100 |

| 3.4.3 Cross-Coupled Pair Noise              | 103 |

| 3.4.4 External Noise Sources                |     |

| 3.5 CONCLUSIONS                             |     |

| CHAPTER4: OPTIMIZATION TECHNIQUES           | 111 |

| 4.1 INTRODUCTION                            | 111 |

| 42 MONOL THIS INDUCTORS                     | 110 |

| 4.2.1 Active Inductors                        | 113 |

|-----------------------------------------------|-----|

| 4.2.2 Bond-Wire Inductors                     | 115 |

| 4.2.3 Planar Spiral Inductors                 | 116 |

| 4.2.4 MEMS Inductors                          | 118 |

| 4.3 SPIRAL INDUCTOR OPTIMIZATION              | 120 |

| 4.3.1 Simple Inductor Expressions             | 120 |

| 4.3.2 High Frequency Inductors                | 122 |

| 4.3.3 Geometric Inductor Optimization         | 130 |

| 4.4 L/C RATIO OPTIMIZATION                    | 135 |

| 4.5 TRANSISTOR SIZE OPTIMIZATION              | 140 |

| 4.5.1 Tail Transistor Size                    | 140 |

| 4.5.2 Cross-Coupled Oscillator Noise Analysis | 141 |

| 4.5.3 Cross-Coupled Pair Optimization         | 153 |

| 4.6 OTHER OPTIMIZATION MEASURES               | 157 |

| 4.6.1 Bypass Capacitors                       | 157 |

| 4.6.2 Low-Power, Low-Noise Current Biasing    | 159 |

| 4.7 CONCLUSIONS                               | 162 |

| CHAPTER5: HIGH PERFORMANCE SOI CMOS VCOS      | 164 |

| 5.1 INTRODUCTION                              | 164 |

| 5.2 0.5μm SOS CMOS PROCESS                    | 165 |

| 5.3 EXPERIMENTAL 5GHZ VCOS                    | 167 |

| 5.3.1 VCO Designs                             | 168 |

| 5.3.2 Inductor Designs                        | 173 |

| 5.3.3 Results                                 | 177 |

| 5.4 EXPERIMENTAL 17GHZ VCOS                   | 189 |

| 5.4.1 VCO Designs                             | 190 |

| 5.4.2 Inductor Designs                        | 192 |

| 5.4.3 Results                                 | 193 |

| 5.5 LOW-NOISE 5GHZ VCOS                       | 199 |

| 5 5 1 VCO Designs                             | 200 |

| 5.5.2 Tank Design                         | 203 |

|-------------------------------------------|-----|

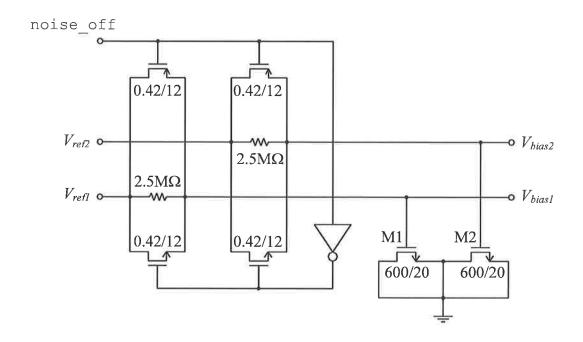

| 5.5.3 Low Noise Measures                  | 206 |

| 5.5.4 Results                             | 208 |

| 5.6 CONCLUSIONS                           | 214 |

| CHAPTER6: HIGH PERFORMANCE BULK CMOS VCOS | 218 |

| 6.1 INTRODUCTION                          | 218 |

| 6.2 0.18μm BULK CMOS PROCESS              | 219 |

| 6.3 LOW-NOISE 5GHZ VCO                    | 221 |

| 6.3.1 Inductor Design                     | 222 |

| 6.3.2 VCO Design                          | 224 |

| 6.3.3 Results                             | 228 |

| 6.4 INDUSTRIAL QUALITY 5GHZ VCO           | 232 |

| 6.4.1 Specifications                      | 233 |

| 6.4.2 Tank Design                         | 235 |

| 6.4.3 VCO Design                          | 238 |

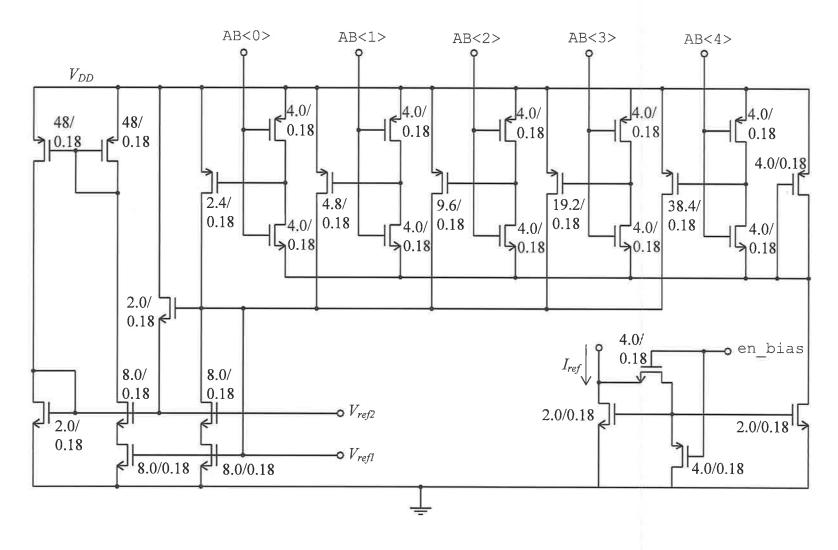

| 6.4.4 Bias Current Generator              | 241 |

| 6.4.5 Amplitude Detector                  | 245 |

| 6.4.6 Results                             | 246 |

| 6.5 VCO PERFORMANCE COMPARISON            | 257 |

| 6.6 CONCLUSIONS                           | 259 |

| CHAPTER7: CONCLUSIONS AND RECOMMENDATIONS | 260 |

| 7.1 CONCLUSIONS                           | 260 |

| 7.2 RECOMMENDATIONS                       | 264 |

| REFERENCES                                | 266 |

| APPENDIX                                  | 277 |

# **LIST OF FIGURES**

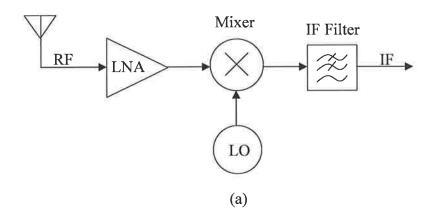

| Fig. 1.1: Superheterodyne (a) receiver and (b) transmitter.                                                        | .3 |

|--------------------------------------------------------------------------------------------------------------------|----|

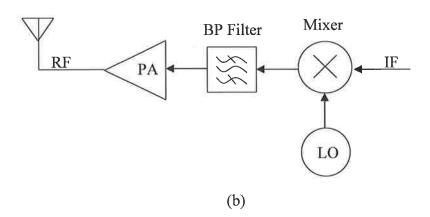

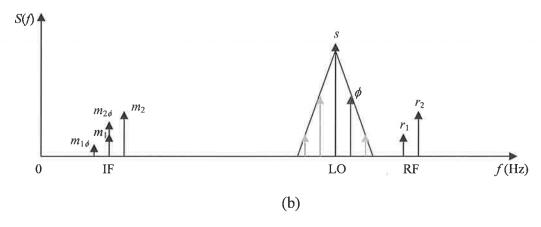

| Fig. 1.2: Downconversion with (a) noiseless LO and (b) noisy LO                                                    | 6  |

| Fig. 1.3: Maximum to minimum amplitude ratio in 64-bit QAM constellation                                           | 8  |

| Fig. 1.4: Typical frequency tuning curve of a VCO                                                                  | 0  |

| Fig. 1.5: Frequency bands allocations for (a) IEEE 802.11b/g, (b) IEEE 802.11a and                                 |    |

| HiPERLAN II, and (c) HiPERLINK wireless communication standards1                                                   | 7  |

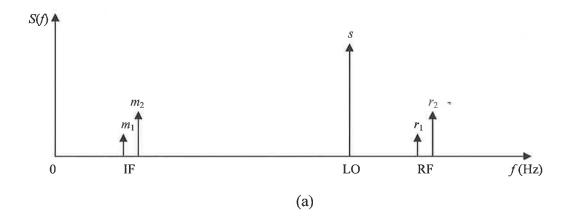

| Fig. 2.1: Power spectral density of a VCO output.                                                                  | 4  |

| Fig. 2.2: Phase noise plot of a typical electronic oscillator.                                                     | .7 |

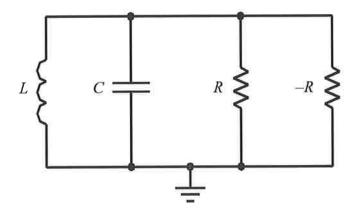

| Fig. 2.3: Simple negative resistance <i>LC</i> tuned oscillator.                                                   | 9  |

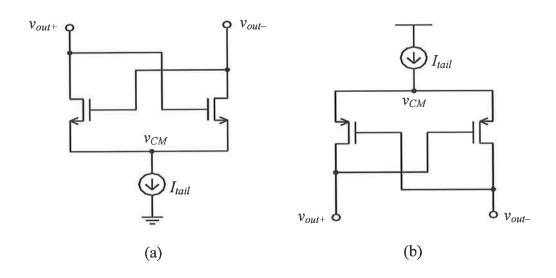

| Fig. 3.1: (a) NMOS cross-coupled pair (b) PMOS cross-coupled pair5                                                 | 1  |

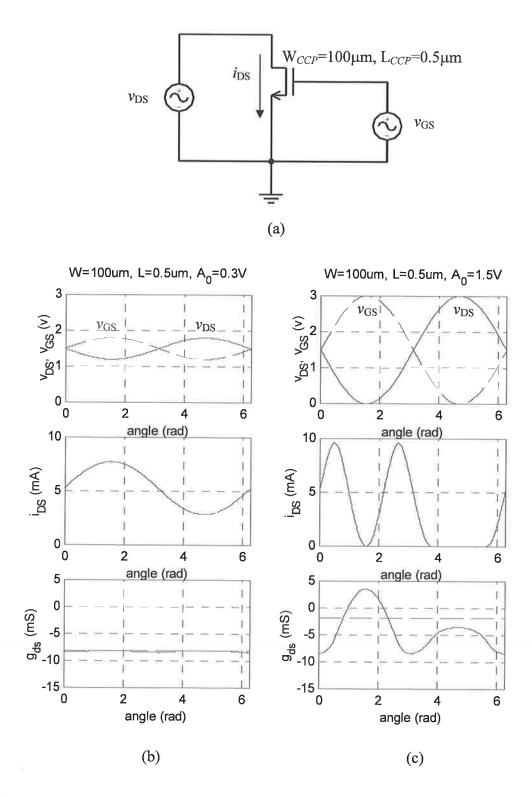

| Fig. 3.2: (a) One of cross-coupled transistors set up for transient simulations, (b) small-                        |    |

| signal transient simulation result, and (c) large-signal transient simulation                                      |    |

| result5                                                                                                            | 2  |

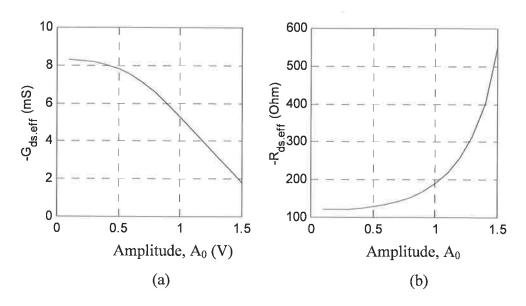

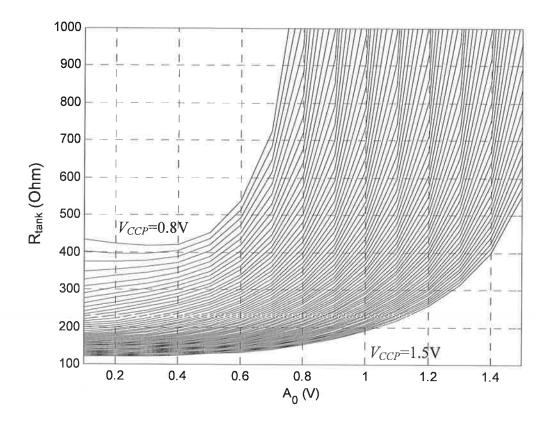

| Fig. 3.3: (a) Effective negative drain-source conductance, $-G_{ds.eff}$ and (b) its inverse,                      |    |

| $R_{ m ds,eff}$ are plotted against oscillation amplitude, $A_0$ .                                                 | 4  |

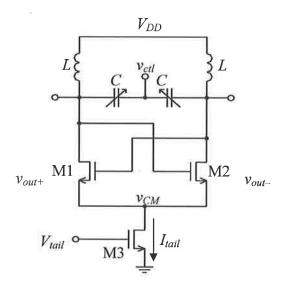

| Fig. 3.4: Typical NMOS-only topology.                                                                              | 6  |

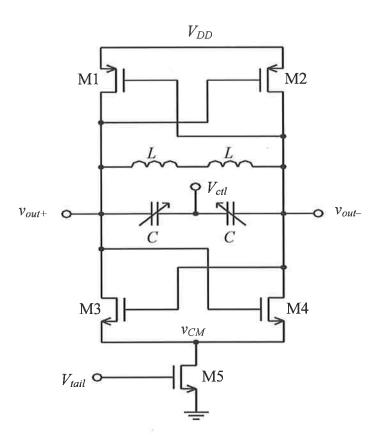

| Fig. 3.5: Top biased NMOS-only topology5                                                                           | 9  |

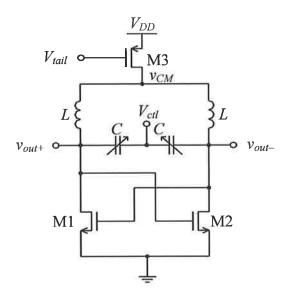

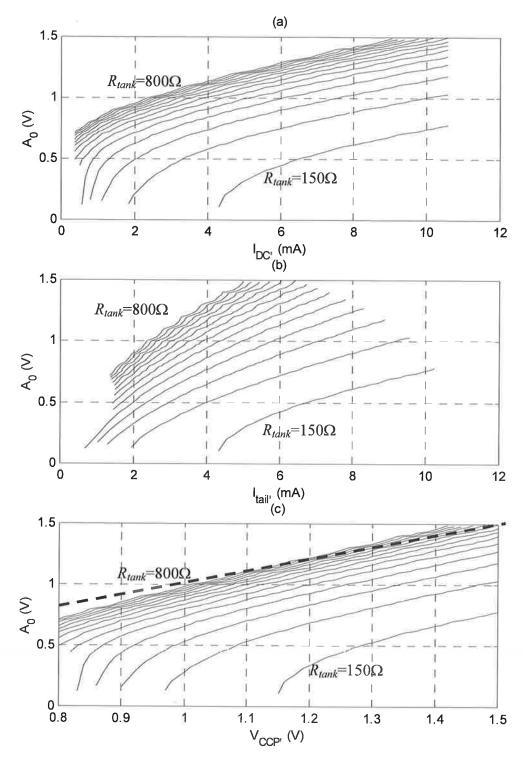

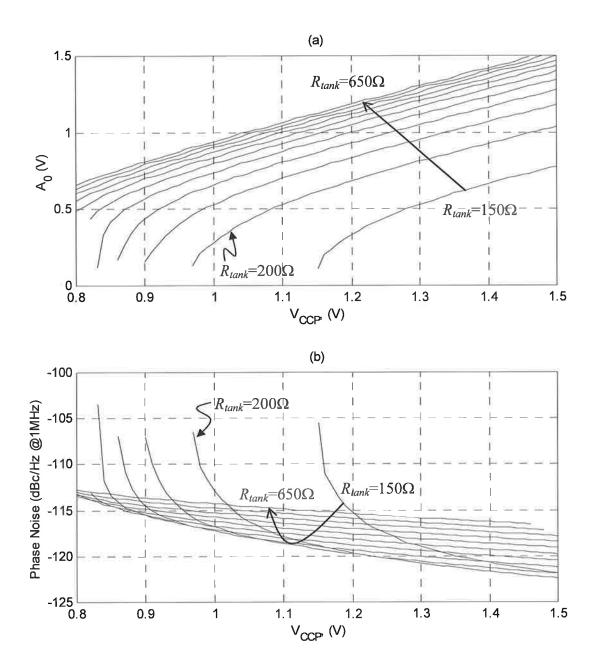

| Fig. 3.6: $R_{tank}$ versus $A_0$ , while sweeping $V_{CCP}$ from 0.8V to 1.5V in 10mV steps6                      | 2  |

| Fig. 3.7: (a) Amplitude versus DC bias current, (b) amplitude versus average bias                                  |    |

| current, and (b) amplitude versus cross-couples pair bias potential, while                                         |    |

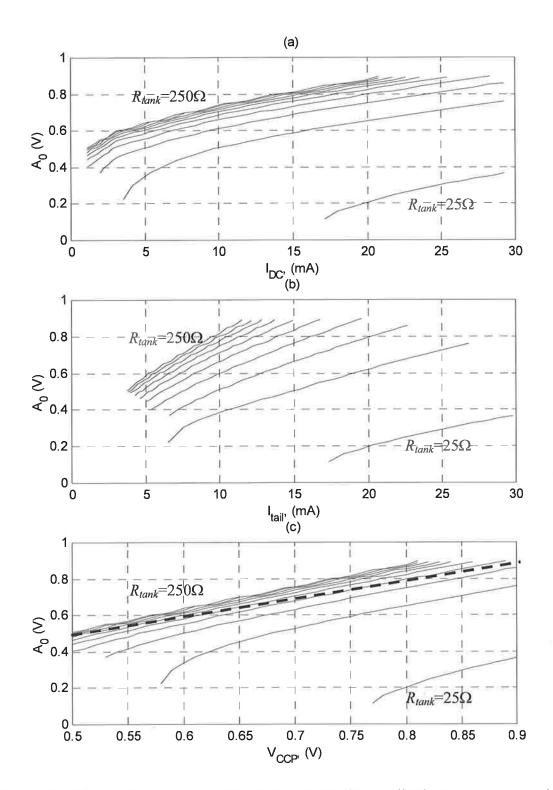

| sweeping $R_{tank}$ from 150 $\Omega$ to 800 $\Omega$ in 50 $\Omega$ intervals6                                    | 4  |

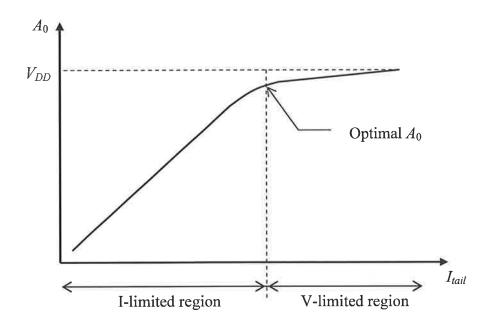

| Fig. 3.8: Classical oscillation amplitude variation with respect to tail bias current6                             | 5  |

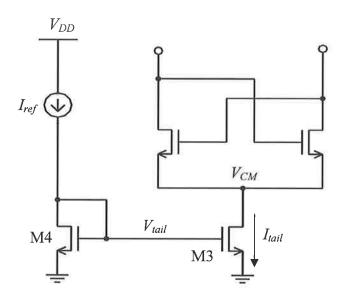

| Fig. 3.9: Simple tail current bias scheme for a cross-coupled pair6                                                | 6  |

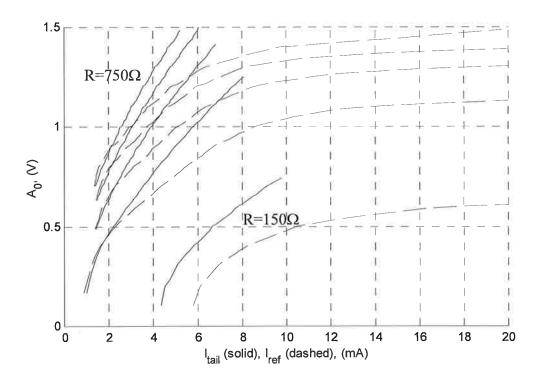

| Fig. 3.10: $A_0$ versus $I_{tail}$ (solid line) and $A_0$ versus $I_{ref}$ (dashed line), while varying $R_{tank}$ |    |

| from $150\Omega$ to $750\Omega$ in $150\Omega$ intervals.                                                          | 7  |

| Fig. 3.11 | : (a) Amplitude versus DC bias current, (b) amplitude versus average bias             |

|-----------|---------------------------------------------------------------------------------------|

|           | current, and (b) amplitude versus cross-coupled pair bias potential, while            |

|           | sweeping $R_{tank}$ from 25 $\Omega$ to 250 $\Omega$ in 25 $\Omega$ intervals         |

| Fig. 3.12 | : PMOS-only topology70                                                                |

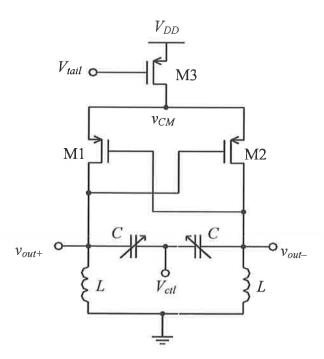

| Fig. 3.13 | : Complementary CMOS VCO topology73                                                   |

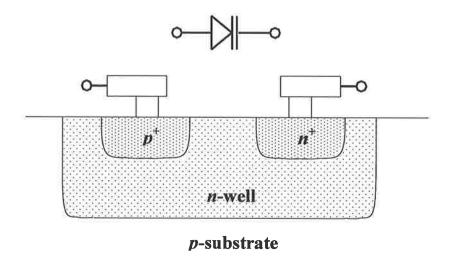

| Fig. 3.14 | : p <sup>+</sup> -n junction diode symbol and cross-section side view                 |

| Fig. 3.15 | : A cross-coupled NMOS-only VCO utilizing a pair of $p^+$ - $n$ junction diodes for   |

|           | a continuous frequency tuning                                                         |

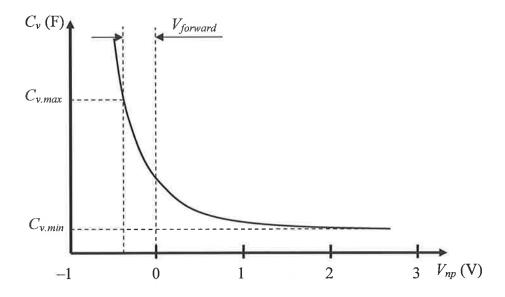

| Fig. 3.16 | : Reverse biased diode junction capacitance variation                                 |

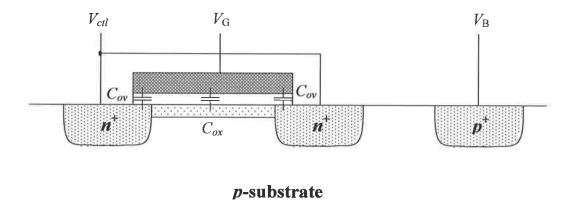

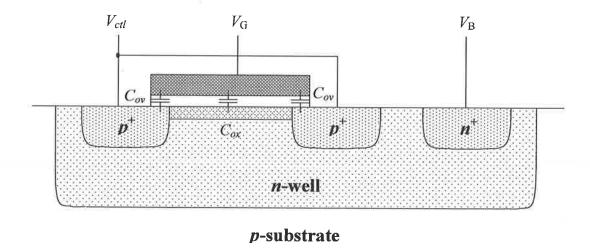

| Fig. 3.17 | : Inversion mode NMOS varactor                                                        |

| Fig. 3.18 | : A cross-coupled NMOS-only VCO utilizing a pair of inversion mode NMOS               |

|           | varactors for frequency tuning                                                        |

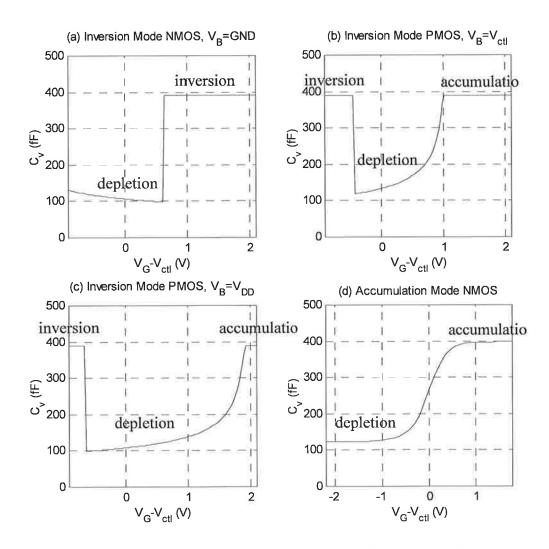

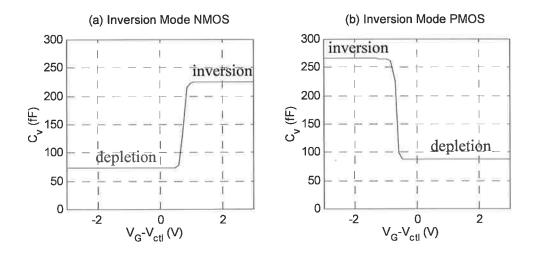

| Fig. 3.19 | : MOS varactor tuning characteristics: (a) inversion mode NMOS varactor, (b)          |

|           | inversion mode PMOS varactor with $V_B=V_{ctl}$ , (c) inversion mode PMOS             |

|           | varactor with $V_B=V_{DD}$ , and (d) accumulation mode NMOS varactor83                |

| Fig. 3.20 | : Inversion mode PMOS varactor                                                        |

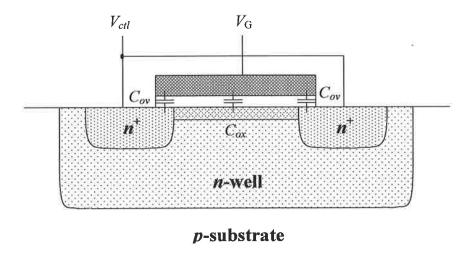

| Fig. 3.21 | : Accumulation mode NMOS varactor85                                                   |

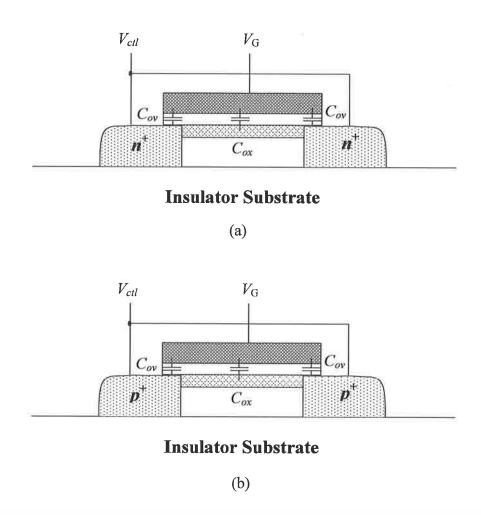

| Fig. 3.22 | : SOI (a) NMOS transistor and (b) PMOS transistor whose source and drain are          |

|           | connected together to work as varactors                                               |

| Fig. 3.23 | : Varactor capacitance variation in a SOI process: (a) inversion mode NMOS            |

|           | varactor, and (b) inversion mode PMOS varactor87                                      |

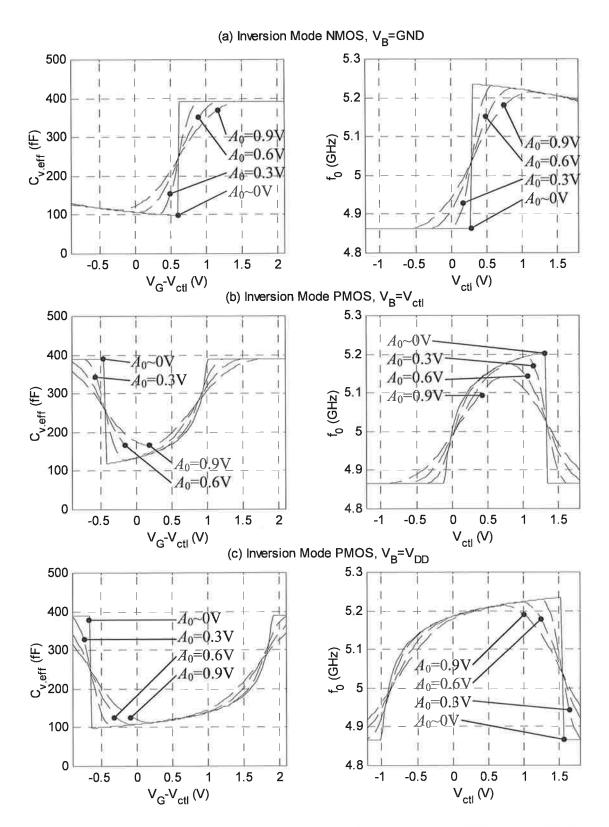

| Fig. 3.24 | : $C_{v.eff}$ curves and VCO frequency-tuning curves at different oscillation         |

|           | amplitudes: (a) inversion mode NMOS, (b) inversion mode PMOS with $V_{\rm B}$ =       |

|           | $V_{ctl}$ , and (c) inversion mode PMOS with $V_B=V_{DD}$ 89                          |

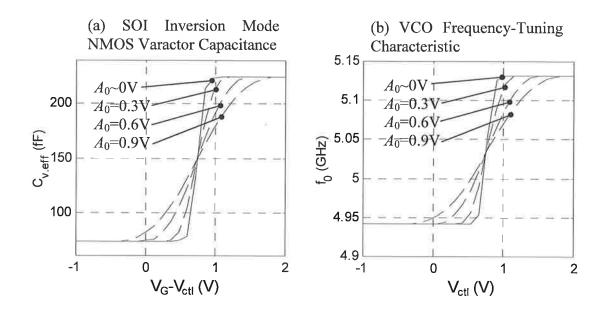

| Fig. 3.25 | : (a) $C_{v.eff}$ curves and (b) VCO frequency-tuning curves at different oscillation |

|           | amplitudes, using inversion mode NMOS varactors from a SOI process90                  |

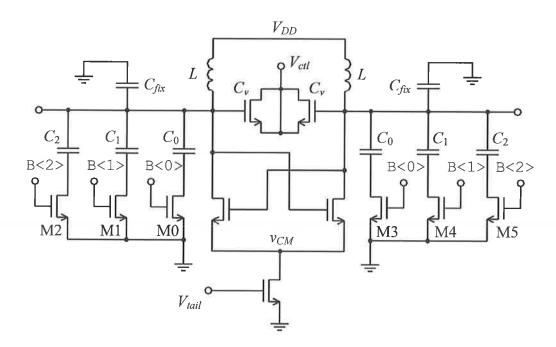

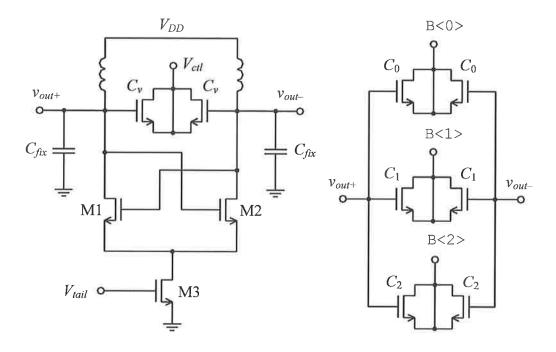

| Fig. 3.26 | : NMOS-only VCO with 3-bit binary weighted switched capacitors for discrete           |

|           | and wider frequency tuning92                                                          |

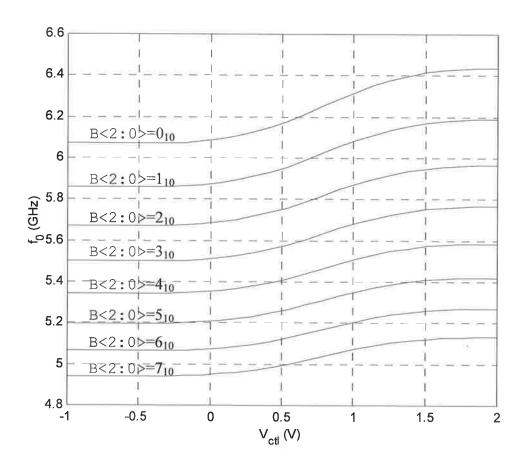

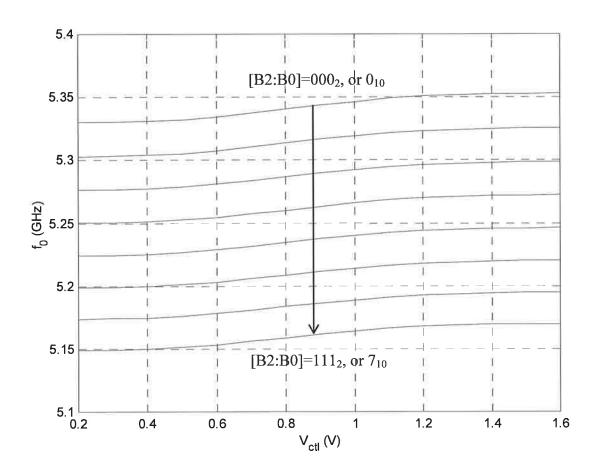

| Fig. 3.27 | : Frequency tuning curves of a VCO with 3-bit switched capacitor bank94               |

| Fig. 3.28 | : 3-bit switched capacitor bank implemented with SOI MOS varactors96                  |

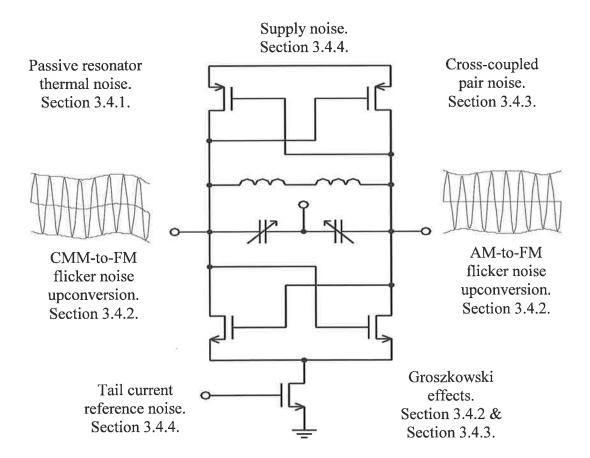

| Fig. 3.29 | Noise sources and processes affecting the oscillator phase noise                      |

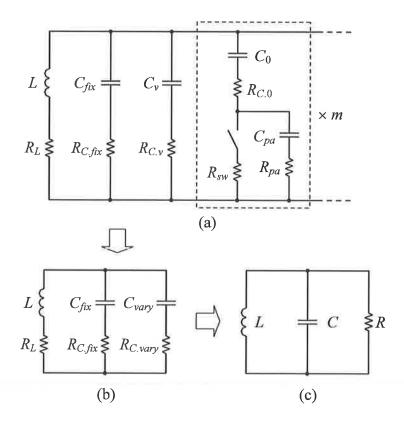

| Fig. 3.30: Equivalent circuits of a passive LC resonator with an m-bit switched capacitor                          |

|--------------------------------------------------------------------------------------------------------------------|

| bank98                                                                                                             |

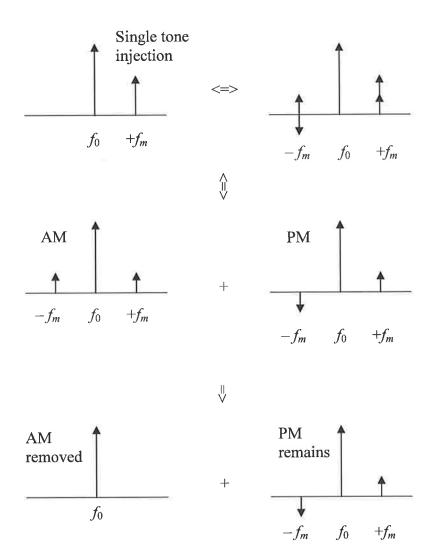

| Fig. 3.31: Single tone injected near the carrier transforms to phase noise due to                                  |

| amplitude limiting property of a real VCO                                                                          |

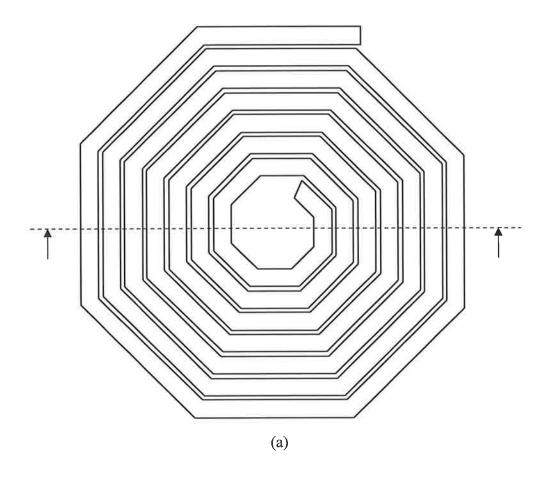

| Fig. 4.1: (a) Top view, and (b) cross-sectional side view of an octagonal planar spiral                            |

| inductor                                                                                                           |

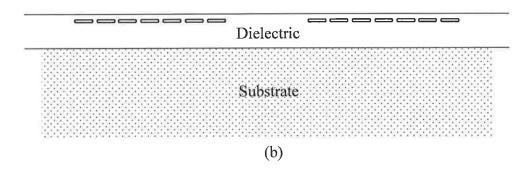

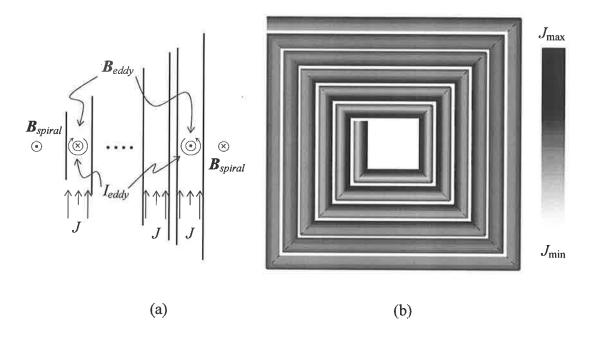

| Fig. 4.2: (a) Eddy current generation, and (b) resulting current density plot generated by                         |

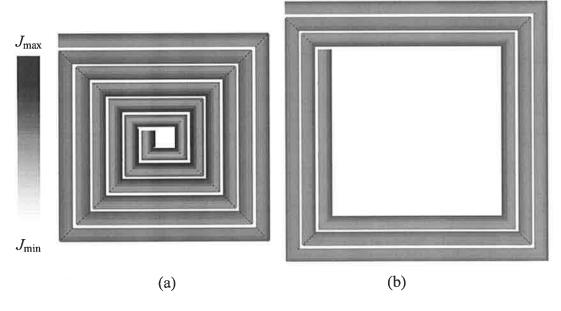

| ASITIC124                                                                                                          |

| Fig. 4.3: Current crowding reduction by hollow spiral geometry125                                                  |

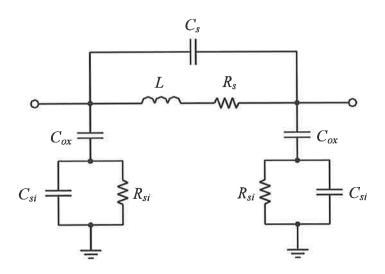

| Fig. 4.4: Physical $\Pi$ model of a spiral inductor on a lossy substrate                                           |

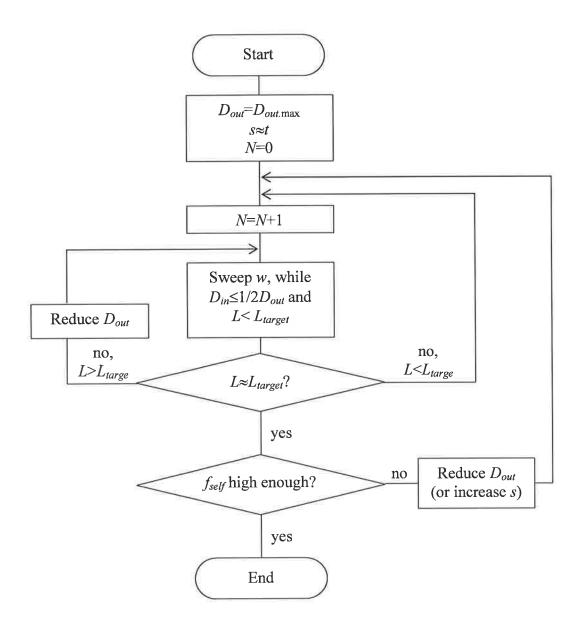

| Fig. 4.5: $C_{ox}$ , $C_{si}$ and $R_{si}$ replaced with a parallel combination of $C_p$ and $R_p$ for simplicity. |

|                                                                                                                    |

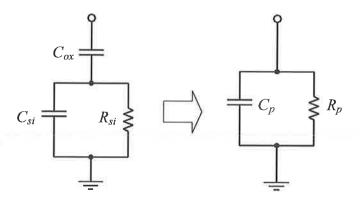

| Fig. 4.6: Spiral inductor optimization flowchart.                                                                  |

| Fig. 4.7: Square, octagonal, and circular shapes have the same area to perimeter ratio.                            |

|                                                                                                                    |

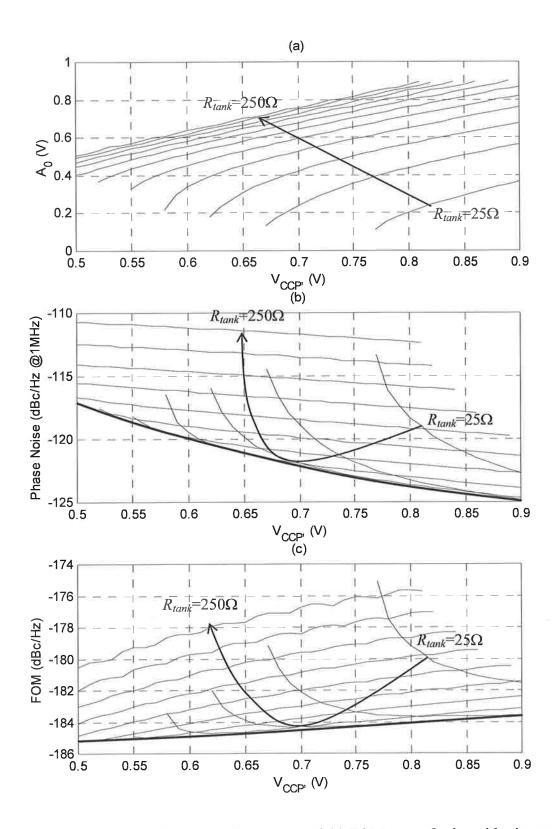

| Fig. 4.8: (a) bias space, (b) phase noise space, and (c) FOM space for logarithmic sweep                           |

| of $R_{tank}$ from 25 $\Omega$ to 250 $\Omega$ over 11 steps, while $W_{CCP}$ is held constant at                  |

| 100μm                                                                                                              |

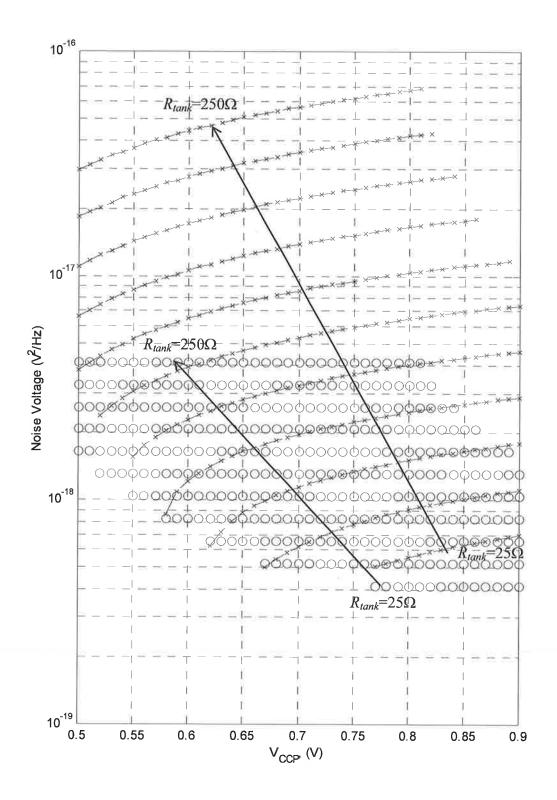

| Fig. 4.9: Noise contributions from passive tank (o) and active cross-coupled transistors                           |

| (×) at different sizes of $R_{tank}$                                                                               |

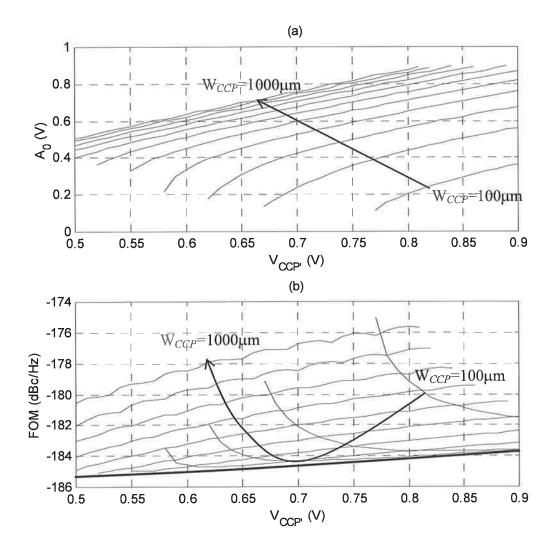

| Fig. 4.10: VCO (a) bias space and (b) FOM space for $R_{tank}$ =25 $\Omega$ and $Q_{tank}$ =7, while               |

| logarithmically sweeping $W_{CCP}$ from 100 $\mu$ m to 1000 $\mu$ m over 11 steps149                               |

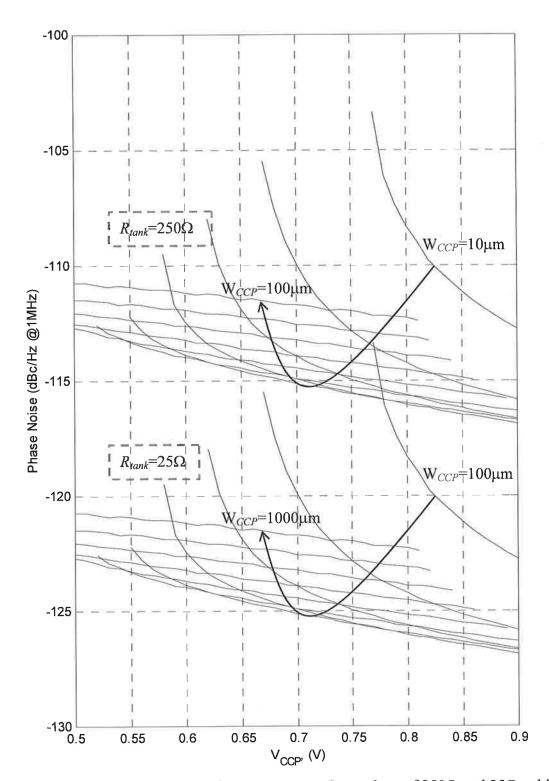

| Fig. 4.11: Two phase noise spaces for two constant $R_{tank}$ values of 250 $\Omega$ and 25 $\Omega$ , while       |

| logarithmically sweeping $W_{CCP}$ from 10 $\mu$ m to 100 $\mu$ m and 100 $\mu$ m to 1000 $\mu$ m                  |

| respectively.                                                                                                      |

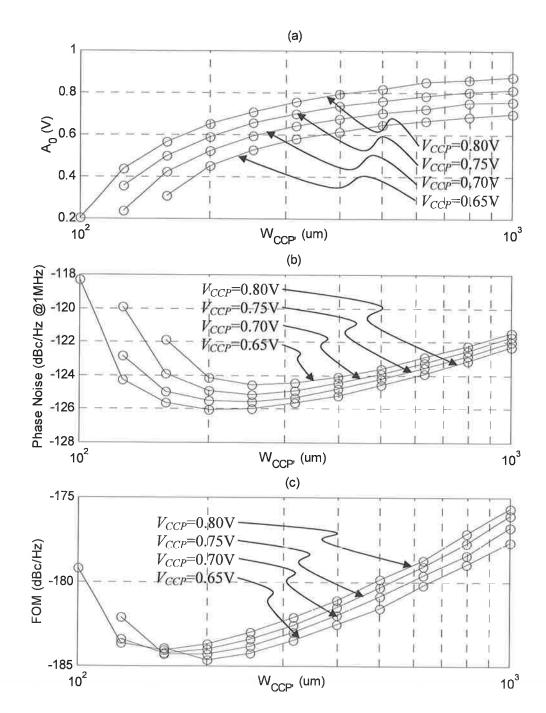

| Fig. 4.12: (a) $A_0$ , (b) phase noise, and (c) FOM variation with respect to $W_{CCP}$ for a                      |

| given tank and under 4 different $V_{CCP}$ bias voltages                                                           |

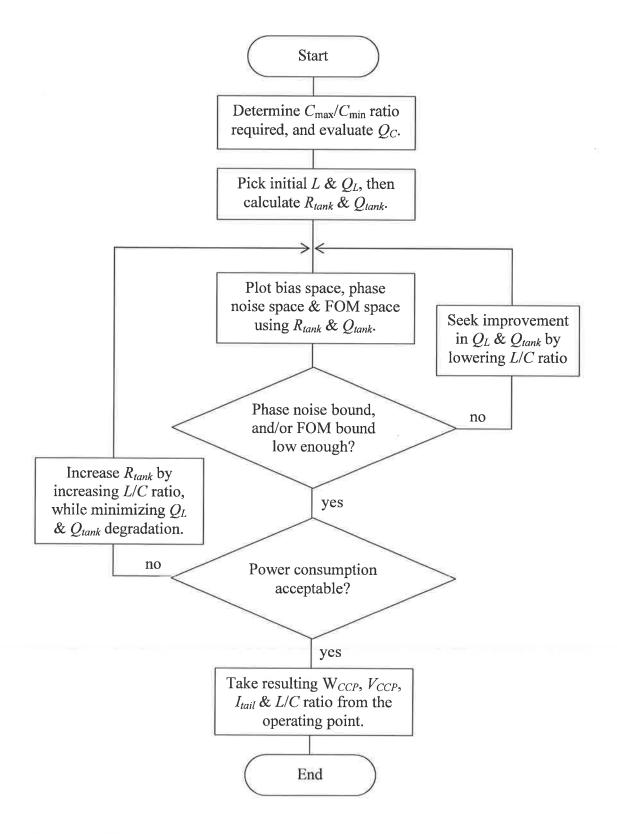

| Fig. 4.13: High performance VCO optimization flowchart                                                             |

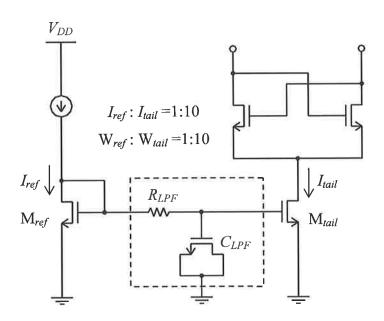

| Fig. 4.14: Use of a RC low-pass filter to attenuate noise from reference current                                   |

| generator                                                                                                          |

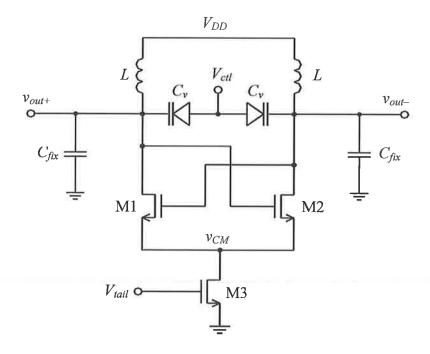

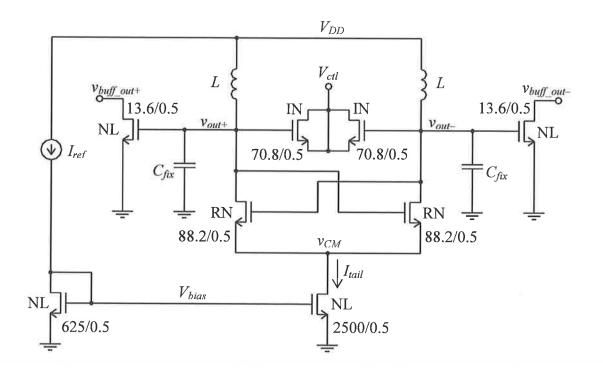

| Fig. 5.1: Schematic diagram of VCO1 and VCO2                                                                       |

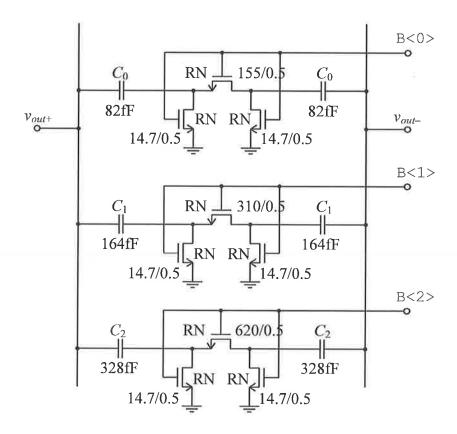

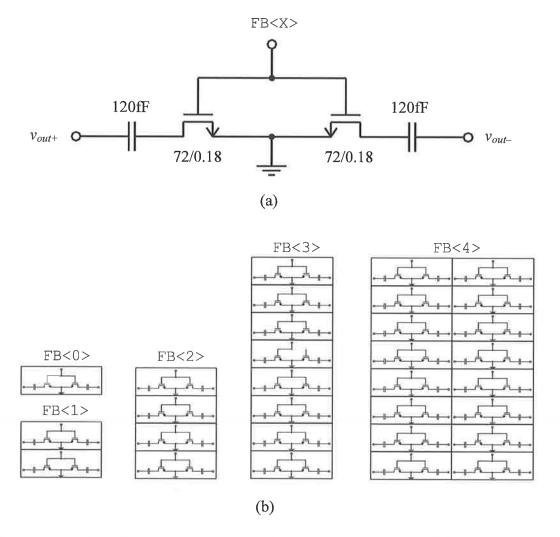

| Fig. 5.2: 3-bit switched capacitor bank for VCO3                                                            |

|-------------------------------------------------------------------------------------------------------------|

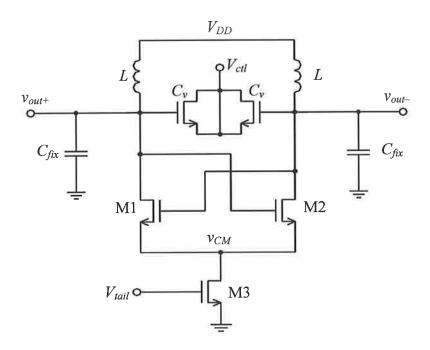

| Fig. 5.3: VCO4 schematic diagram                                                                            |

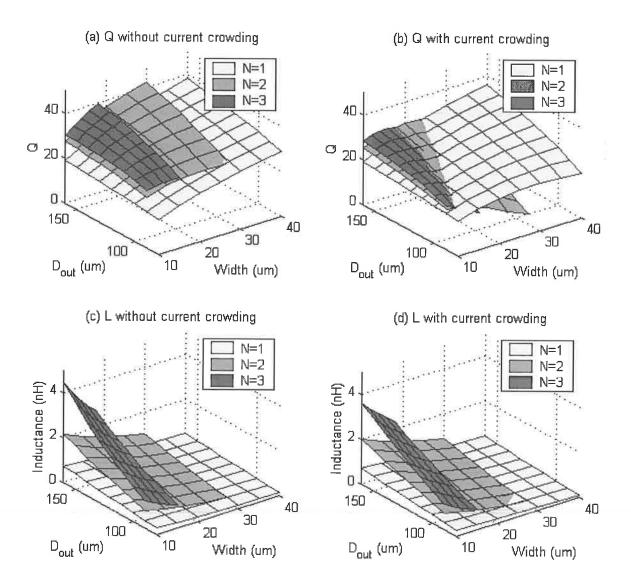

| Fig. 5.4: Inductor quality factor simulation results (a) with or (b) without the high                       |

| frequency effects. Inductance simulation results (c) with or (d) without the                                |

| high frequency effects174                                                                                   |

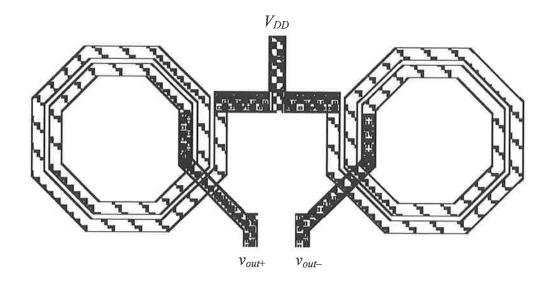

| Fig. 5.5: Spiral inductor pair for differential operation                                                   |

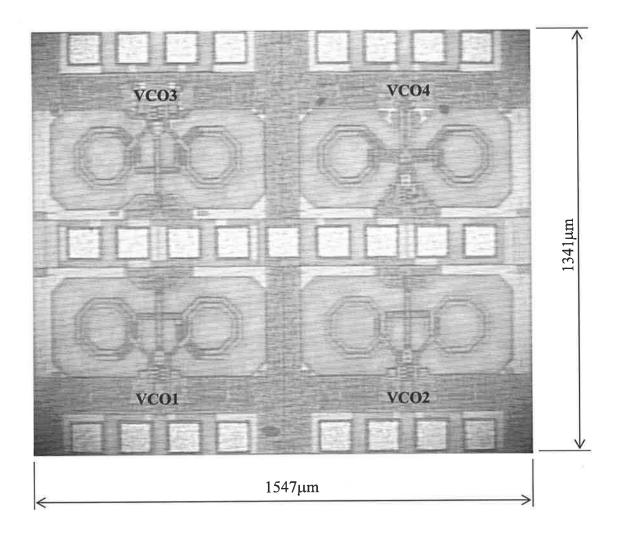

| Fig. 5.6: Four experimental 5GHz VCO microphotograph                                                        |

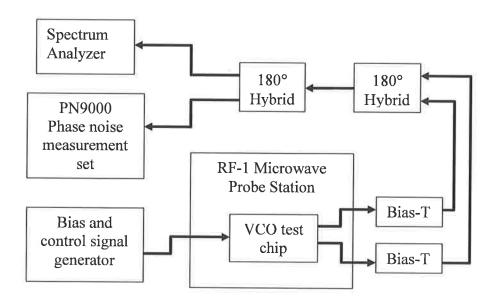

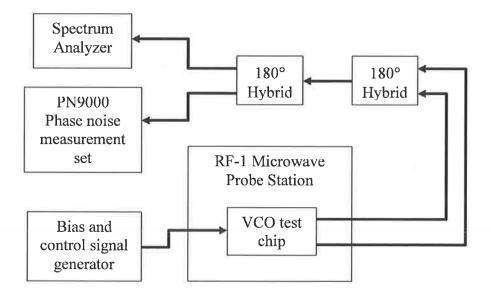

| Fig. 5.7: Phase noise measurement setup for experimental 5GHz VCOs178                                       |

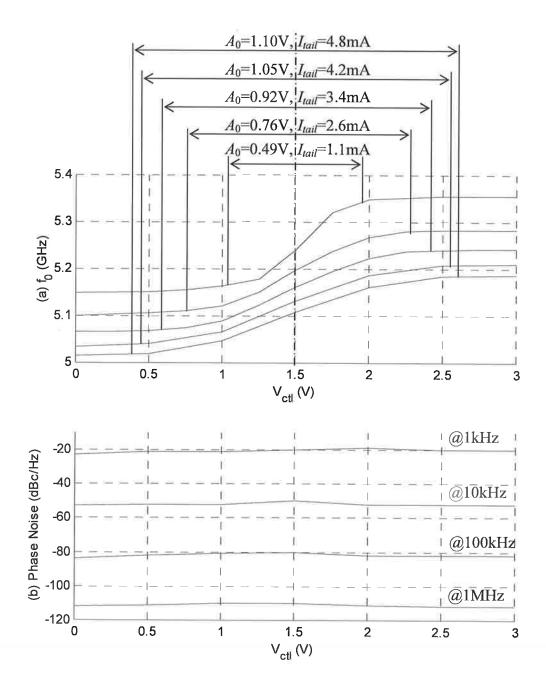

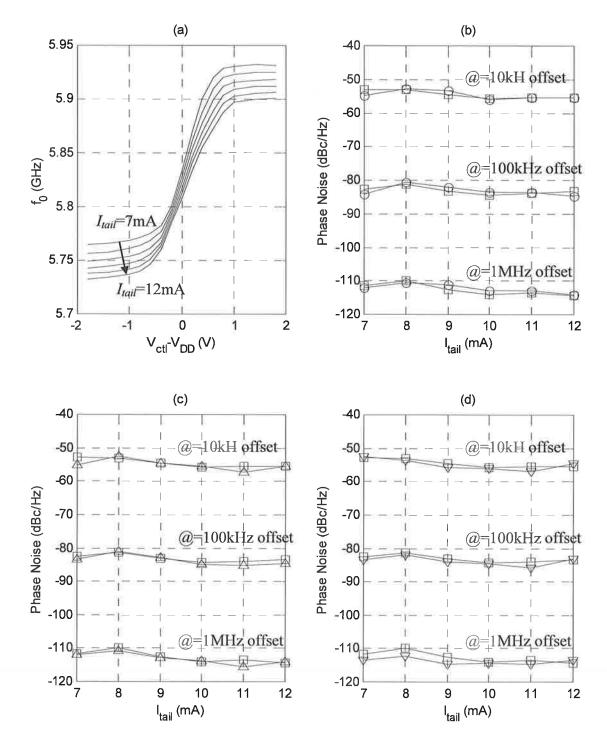

| Fig. 5.8: (a) $f_0$ versus $V_{ctl}$ at various $I_{tail}$ and (b) phase noise across full tuning range for |

| VCO2 with I <sub>tail</sub> =1.1mA180                                                                       |

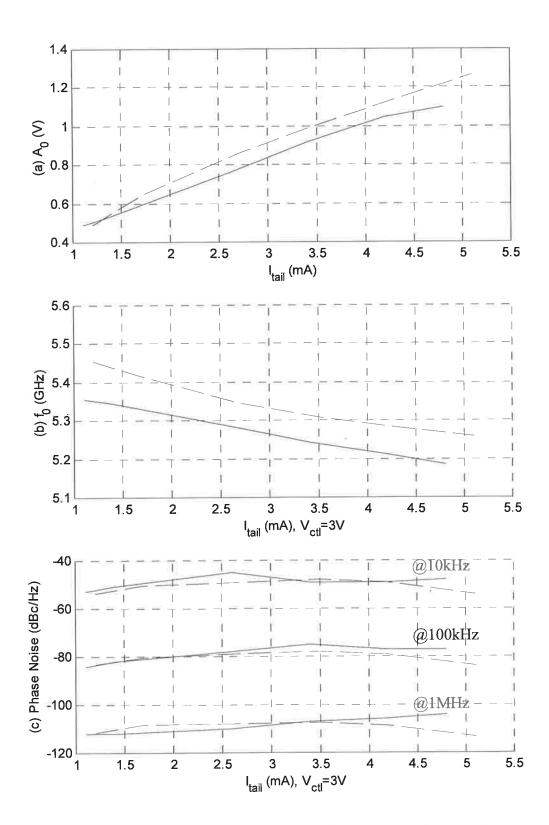

| Fig. 5.9: Measured (solid) and simulated (dashed) (a) $A_0$ , (b) $f_0$ , and (c) phase noise               |

| versus $I_{tail}$ for VCO2 with $V_{cll}=3V$                                                                |

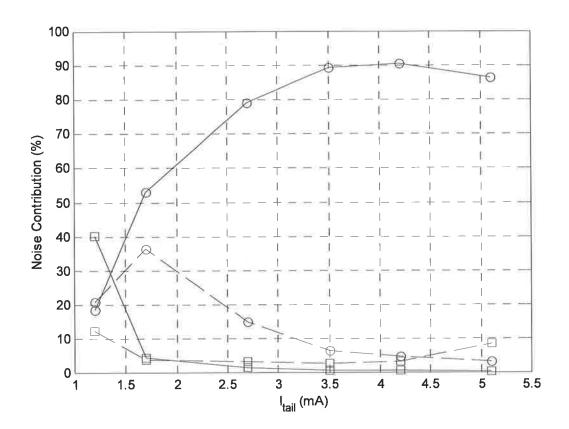

| Fig. 5.10: Simulated flicker noise (solid) and while noise (dashed) contributions from                      |

| tail current bias network (O) and cross-coupled pair ( $\square$ ) versus $I_{tail}$ for VCO2               |

| at 1MHz offset                                                                                              |

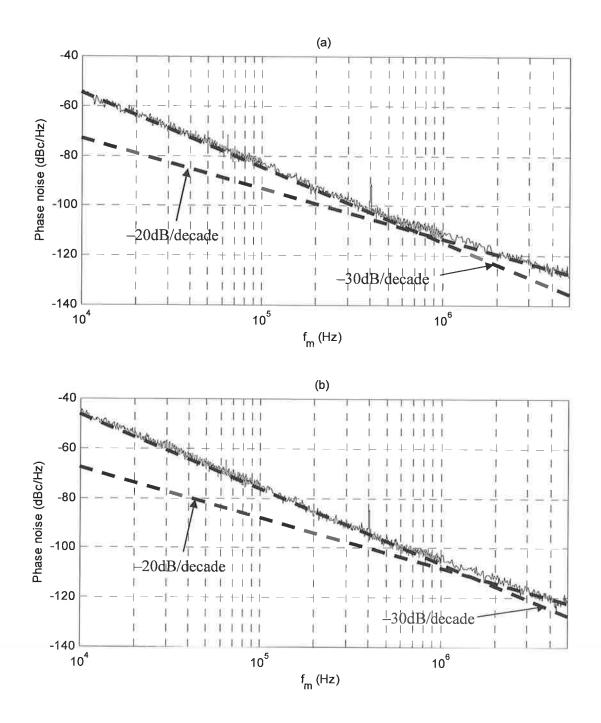

| Fig. 5.11: Spectral plots of measured phase noise of VCO2 at (a) $I_{tail}$ =1.1mA, and (b)                 |

| $I_{tail}$ =4.8mA                                                                                           |

| Fig. 5.12: VCO2 (a) bias space, and (b) phase noise space with constant $R_{tank}$ of 550 $\Omega$ .        |

|                                                                                                             |

| Fig. 5.13: (a) Measured $f_0$ versus $V_{ctl}$ across full tuning range and (b) measured phase              |

| noise versus 3-bit digital frequency control input for VCO3186                                              |

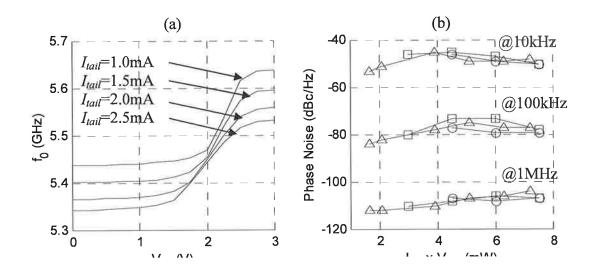

| Fig. 5.14: (a) $f_0$ versus $V_{ctl}$ at various $I_{tail}$ for VCO4, and cross comparison of phase         |

| noise of VCO2 (△), VCO3 (□), and VCO4 (O) over a range of DC power                                          |

| consumption187                                                                                              |

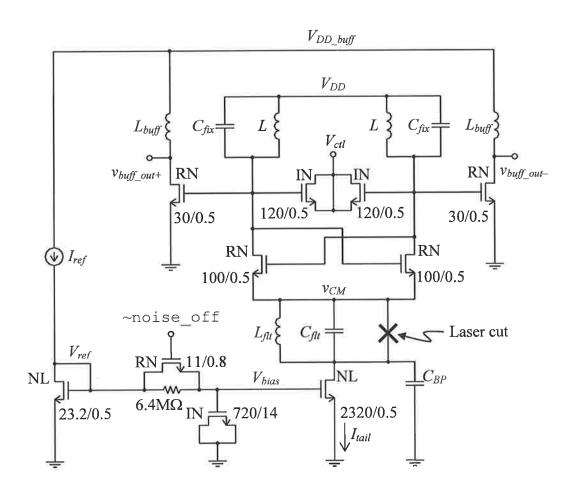

| Fig. 5.15: Schematic diagram of VCO5 and VCO6                                                               |

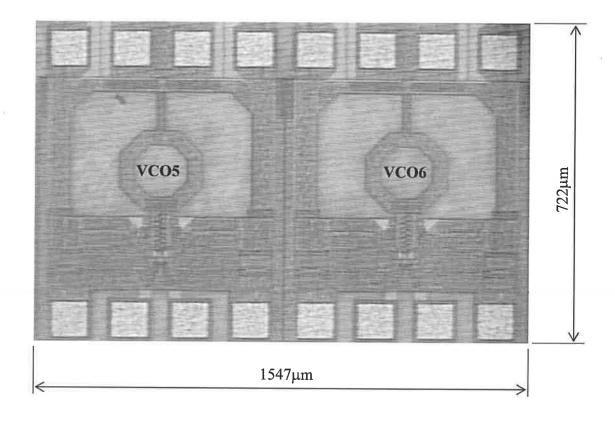

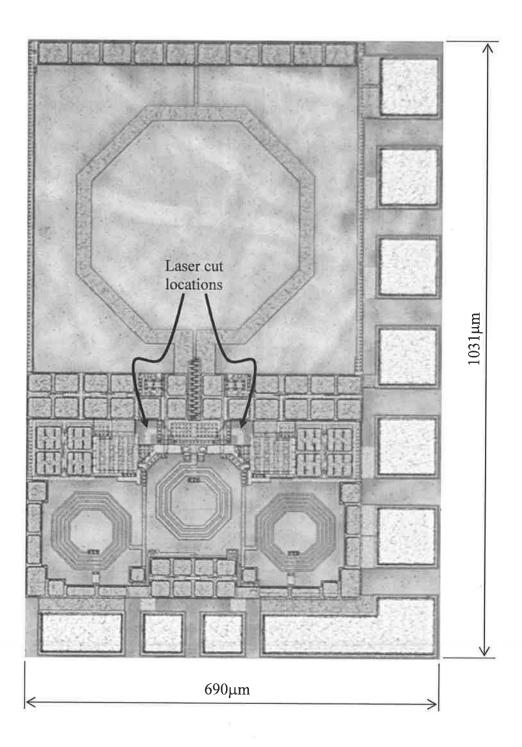

| Fig. 5.16: Microphtograph of VCO5 and VCO6                                                                  |

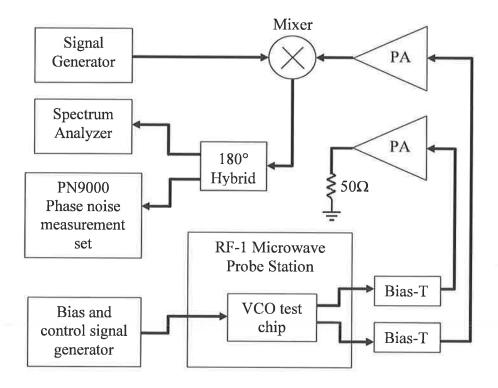

| Fig. 5.17: Phase noise measurement setup for experimental 17GHz VCOs194                                     |

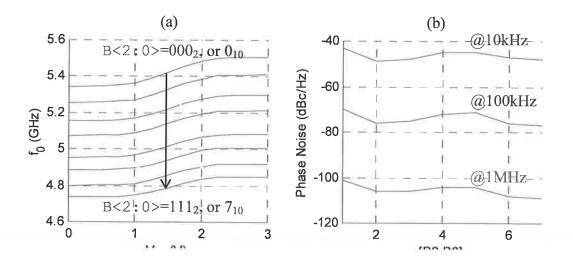

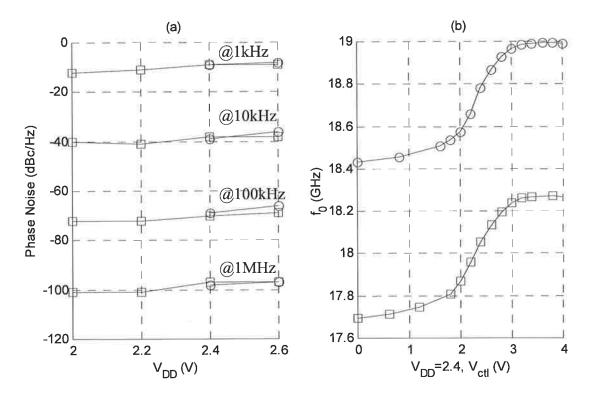

| Fig. 5.18: (a) Phase noise plot and (b) frequency tuning curves of VCO5 ( $\square$ ) and VCO6              |

| (O)195                                                                                                      |

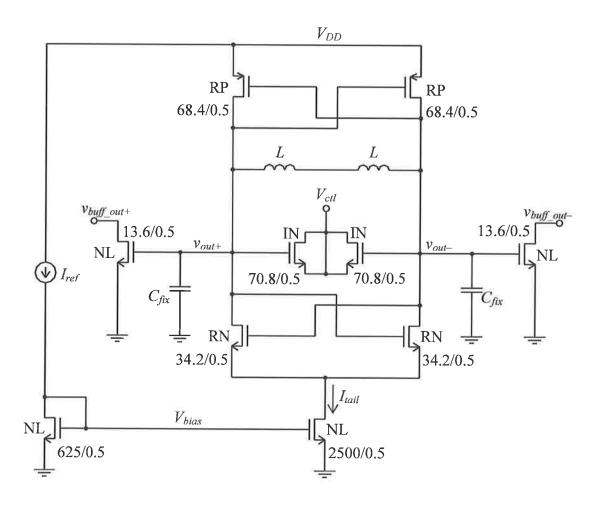

| Fig. 5.19: Schematic diagram for VCO7 and VCO8                                                              |

| Fig. 5.20: Microphotograph of VCO7 and VCO8202                                                              |

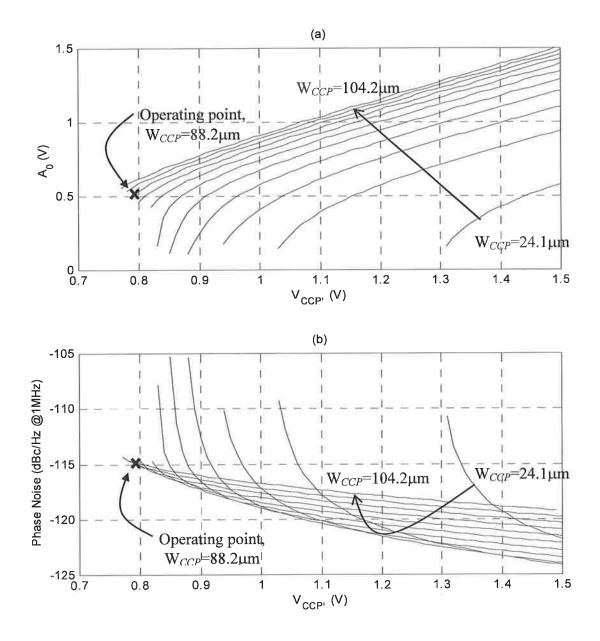

| Fig. 5.21: (a) Bias space and (b) phase noise space of VCO7 and VCO8 for                                        |

|-----------------------------------------------------------------------------------------------------------------|

| $W_{CCP}=100 \mu m$                                                                                             |

| Fig. 5.22: Phase noise measurement setup for VCO7 and VCO8                                                      |

| Fig. 5.23: (a) Frequency tuning curves for VCO7, (b) phase noise plots comparing                                |

| $\sim$ noise_off=0 ( $\square$ ) and $\sim$ noise_off=1 (0), (c) phase noise plots                              |

| comparing $\sim$ noise_off=0 ( $\square$ ) and no tail transistor ( $\triangle$ ), and (d) phase                |

| noise plots comparing $\neg noise\_off=0$ ( $\square$ ) and Hegazi's filter activated ( $\triangledown$ ).      |

| 210                                                                                                             |

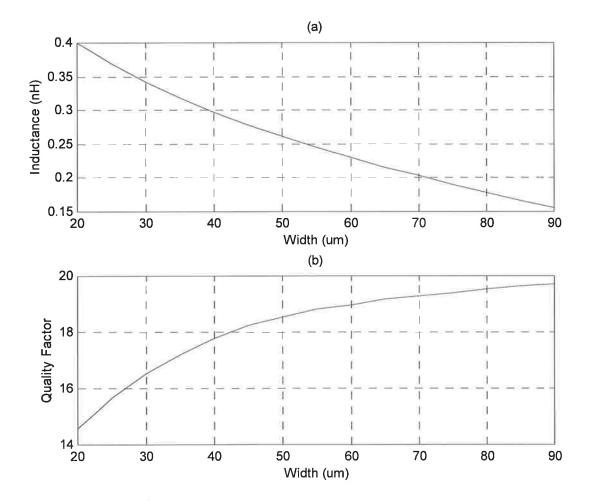

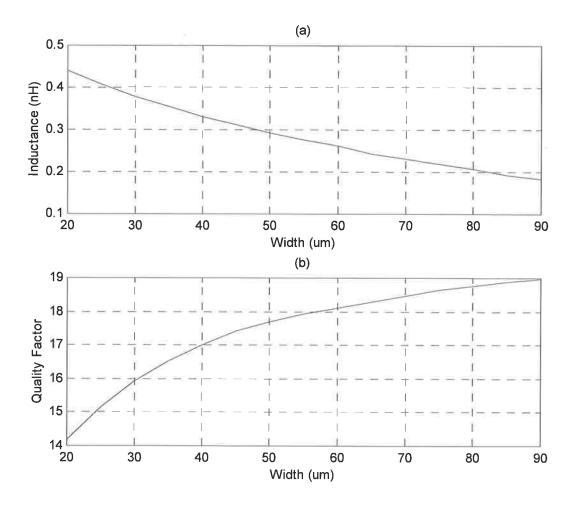

| Fig. 6.1: Simulated (a) inductance and (b) quality factor of a single turn octagonal                            |

| inductor with constant $D_{out}$ of 400 µm, while varying w                                                     |

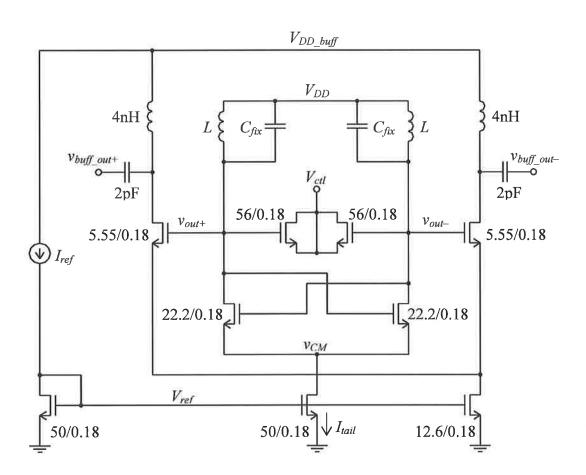

| Fig. 6.2: VCO9 schematic diagram.                                                                               |

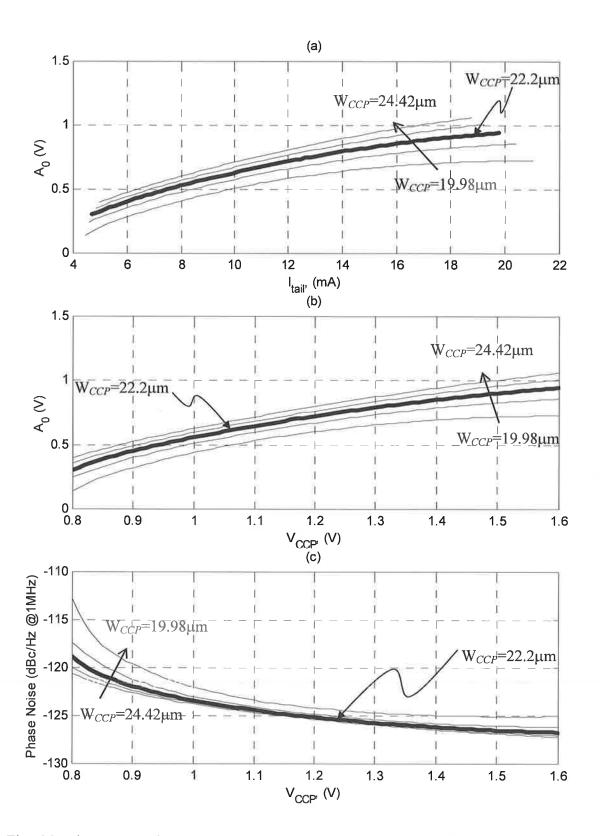

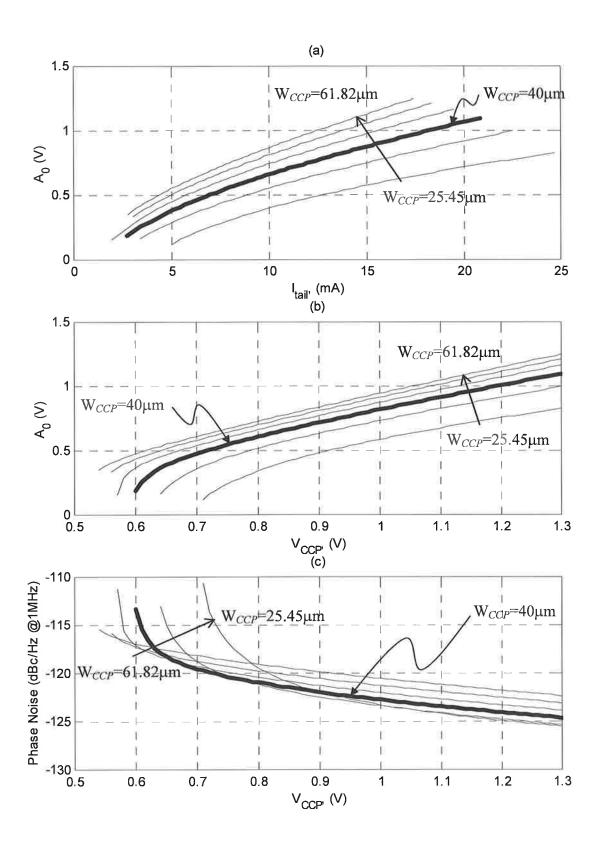

| Fig. 6.3: Bias spaces of (a) $A_0$ versus $I_{tail}$ , (b) $A_0$ versus $V_{CCP}$ , and (c) phase noise space   |

| for constant $R_{tank}$ of 100 $\Omega$ , while varying W <sub>CCP</sub> from 19.98 $\mu$ m to 24.42 $\mu$ m.   |

|                                                                                                                 |

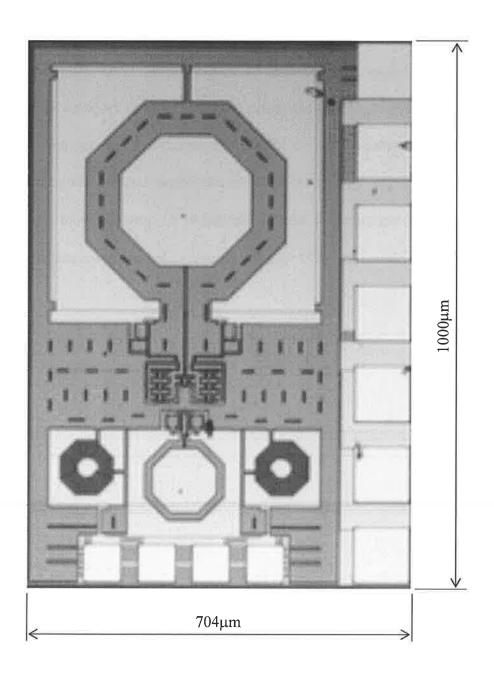

| Fig. 6.4: Low-Noise 5GHz bulk CMOS VCO microphotograph                                                          |

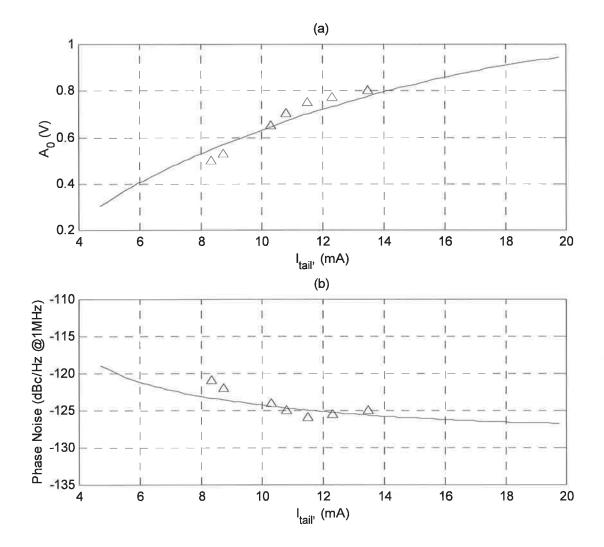

| Fig. 6.5: VCO9 simulation (–) and measurement ( $\triangle$ ) results of (a) oscillation amplitude              |

| and (b) phase noise with respect to tail bias current229                                                        |

| Fig. 6.6: Spectral plot of VCO9 phase noise, when $V_{DD}=1.5$ V and $I_{tait}=11.5$ mA230                      |

| Fig. 6.7: Measured frequency-tuning curves of VCO9.                                                             |

| Fig. 6.8: (a) Schematic diagram of each switched capacitor cell, and (b) binary weighted                        |

| grouping of all 31 cells                                                                                        |

| Fig. 6.9: Simulated (a) inductance and (b) quality factor of a single turn inductor with                        |

| constant $D_{out}$ of 430 µm, and varying $w$                                                                   |

| Fig. 6.10: Bias spaces of (a) $A_0$ versus $I_{tail}$ , (b) $A_0$ versus $V_{CCP}$ , and (c) phase noise space  |

| for a constant $R_{tank}$ of 110 $\Omega$ , while varying W <sub>CCP</sub> from 25.45 $\mu$ m to 61.82 $\mu$ m. |

|                                                                                                                 |

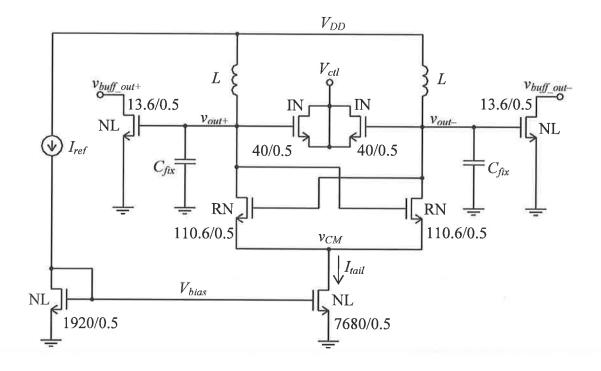

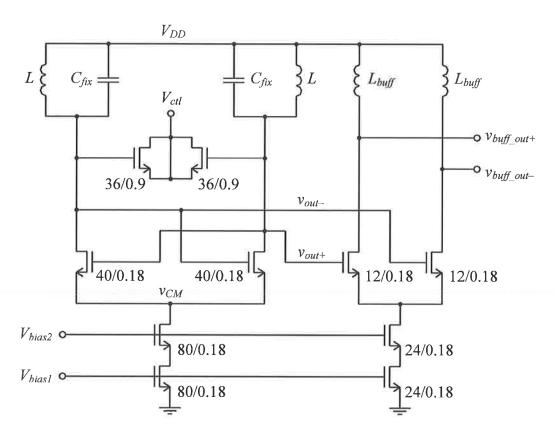

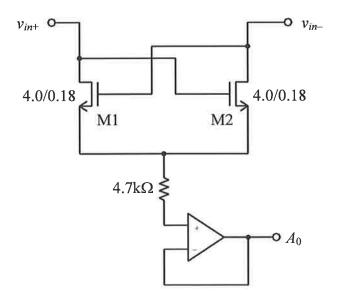

| Fig. 6.11: Schematic diagram of VCO10 and its output buffer                                                     |

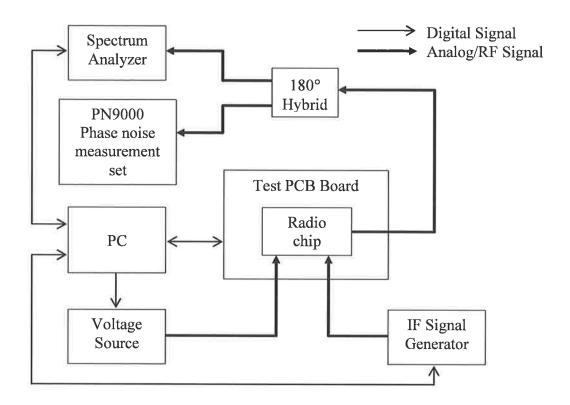

| Fig. 6.12: Bias generator for VCO10.                                                                            |

| Fig. 6.13: Low-power, low-noise current biasing for VCO10244                                                    |

| Fig. 6.14: Oscillation amplitude detector                                                                       |

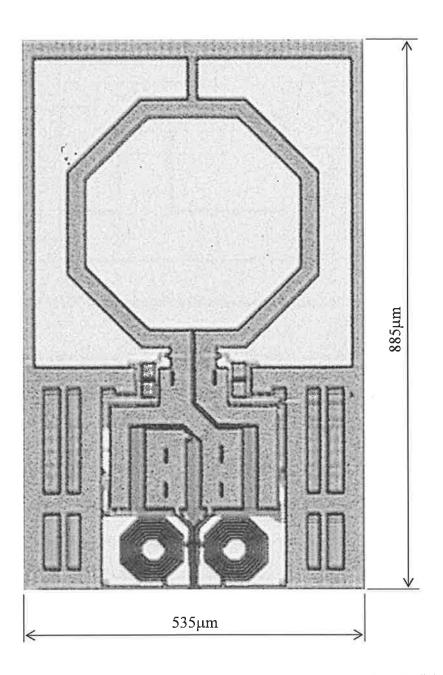

| Fig. 6.15: Microphotograph of 5GHz bulk CMOS VCO for IEEE 802.11a/b/g and                 |

|-------------------------------------------------------------------------------------------|

| HiPERLAN II applications247                                                               |

| Fig. 6.16: Phase noise measurement setup for experimental 5GHz VCOs248                    |

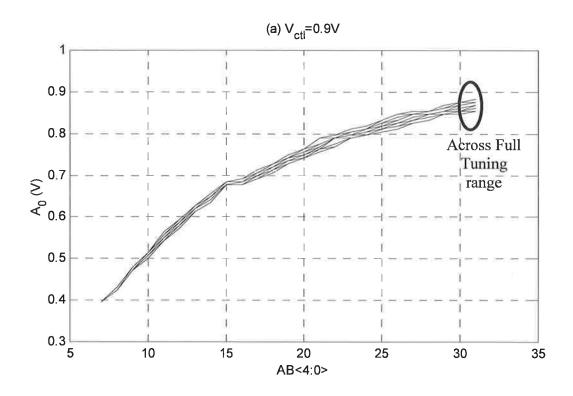

| Fig. 6.17: Measured (a) oscillation amplitude across full frequency tuning range, and (b) |

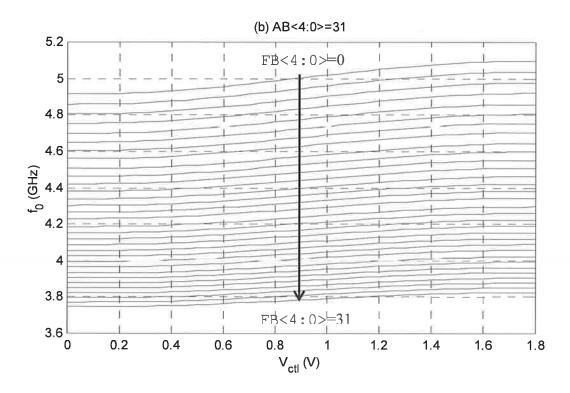

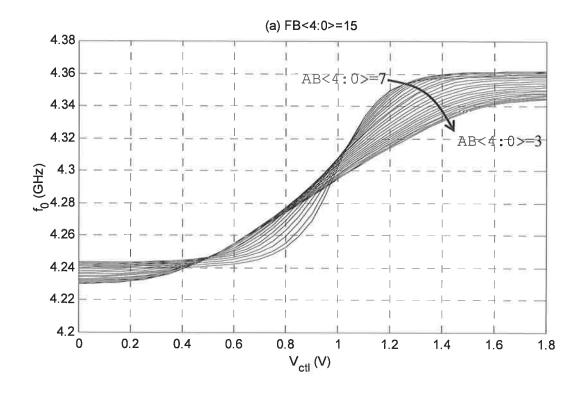

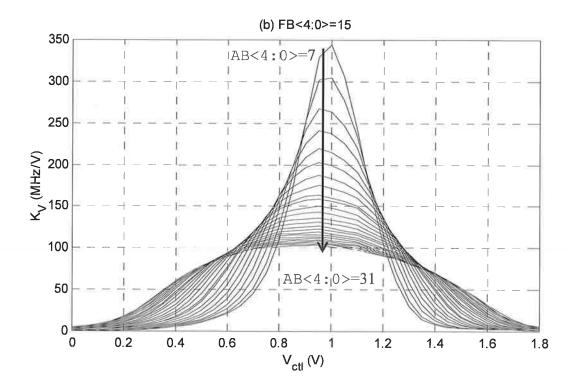

| entire frequency tuning range of VCO10                                                    |

| Fig. 6.18: Measured (a) frequency tuning curves and (b) VCO gain curves at different      |

| oscillation amplitudes of VCO10                                                           |

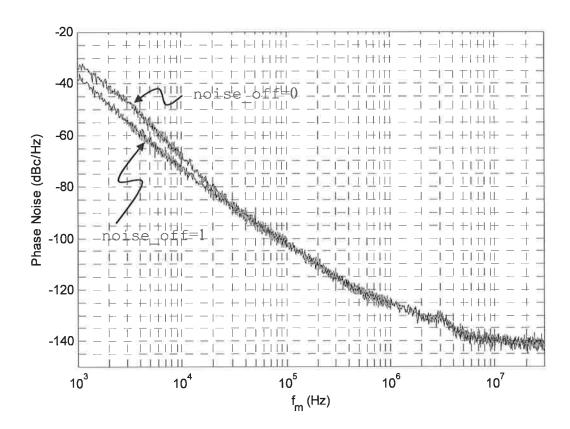

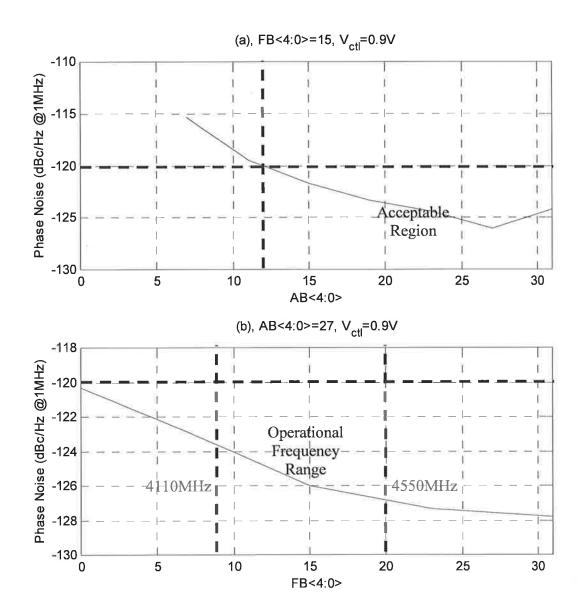

| Fig. 6.19: Measured phase noise spectral plots when noise_off=0 and                       |

| noise_off=1. AB<4:0> and FB<4:0> are held at 27 and 15 respectively,                      |

| and $V_{cll}$ is set to 0.9V                                                              |

| Fig. 6.20: Measured phase noise (a) across full amplitude range, and (b) across full      |

| frequency range                                                                           |

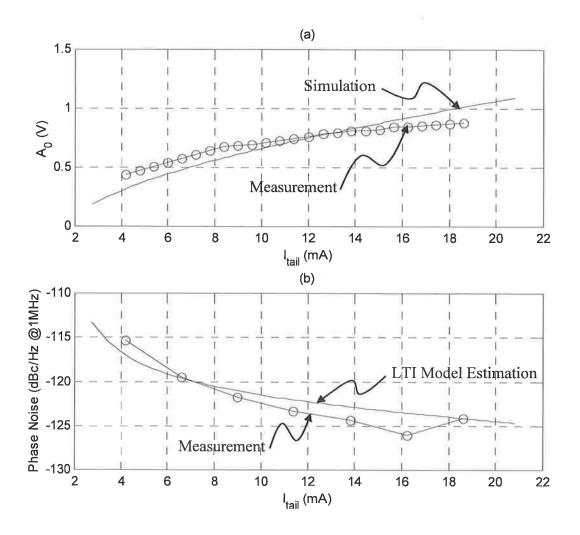

| Fig. 6.21: (a) Oscillation amplitude comparison between simulation and measurement        |

| and (b) phase noise comparison between LTI model estimation and                           |

| measurement256                                                                            |

# LIST OF TABLES

| Table 1.1: Comparison of monolithically implemented modern VCOs        | 14  |

|------------------------------------------------------------------------|-----|

| Table 4.1: Coefficients for modified Wheeler Expression                | 121 |

| Table 4.2: Geometric properties of three common spiral inductor shapes | 134 |

| Table 5.1: SOS transistor types.                                       | 166 |

| Table 5.2: VCO2 phase noise performance comparison.                    | 188 |

| Table 6.1: VCO10 specifications.                                       | 233 |

| Table 6.2: VCO performance comparison.                                 | 258 |

## LIST OF ACRONYMS

AC Alternate Current

ADS Advanced Design Systems

AGC Automatic Gain Control

AM Amplitude Modulation

AP Access Point

ASITIC Analysis and Simulation of Inductors and Transformers in

**Integrated Circuits**

BiCMOS Bipolar CMOS

BP Band-Pass

BSIM Berkeley Short-Channel IGFET Model

CAD Computer Aided Design

CCP Cross-Coupled Pair

CMM Common Mode Modulation

CMOS Complementary Metal Oxide Semiconductor

DC Direct Current

DCR Data Clock Recovery

FET Field-Effect Transistor

FM Frequency Modulation

FOM Figure of Merit

GPIB General Purpose Interface Bus

HBT Heterojunction Bipolar Transistor

HiPERLAN High Performance Radio Local Area Network

HiPERLINK High Performance Radio Link

IC Integrated Circuit

ICI Inter-Carrier Interference

IEEE Institute of Electrical and Electronic Engineering

IF Intermediate Frequency

XVIII

ISF Impulse Sensitivity Function

LNA Low Noise Amplifier

LO Local Oscillator

LP Low-Pass

LTI Linear Time Invariant

LTV Linear Time Varying

MEMS Micro-Electro-Mechanical System

MIM Metal-Insulator-Metal

MMIC Monolithic Microwave Integrated Circuit

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

NMOS N-type Metal Oxide Semiconductor

OFDM Orthogonal Frequency Division Multiplex

PA Power Amplifier

PC Personal Computer

PCM Process Control Monitor

PGS Patterned Ground Shield

PMOS P-type Metal Oxide Semiconductor

PSD Power Spectral Density

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase-Shift Keying

RF Radio Frequency

SAW Surface Acoustic Wave

SER Symbol Error Rate

SNR Signal to Noise Ratio

SNR Signal to Noise Ratio

SOC System On Chip

SOI Silicon On Insulator

SOS Silicon On Sapphire

SPICE Simulation Program with Integrated Circuit Emphasis

SS Single-Sided

SSB Single Side Band

STI Shallow Trench Isolation

TSMC Taiwanese Semiconductor Manufacturing Company

VCO Voltage Controlled Oscillator

VLSI Very Large Scale Integration

WLAN Wireless Local Area Network

WNBU Wireless Networking Business Unit

# LIST OF SYMBOLS

| $\sigma$                         | Conductivity (S/m)                                           |

|----------------------------------|--------------------------------------------------------------|

| ξ                                | $C_{v,max}$ to $C_{v,min}$ ratio                             |

| Γ                                | Impulse sensitivity function                                 |

| γ                                | Transistor channel noise factor                              |

| $\Delta C_{ u}$                  | $C_{v,max}$ – $C_{v,min}$ (F)                                |

| $\delta_{s}$                     | Skin depth (m)                                               |

| $A_0$                            | Single-ended oscillation amplitude (V)                       |

| $C_{fix}$                        | Fixed capacitance (F)                                        |

| $C_{ov}$                         | Gate overlap capacitance (F)                                 |

| $C_{ox}$                         | Unit gate oxide capacitance                                  |

| $C_{ u}$                         | Varactor capacitance (F)                                     |

| $C_{v.e\!f\!f}$                  | Effective varactor capacitance (F)                           |

| $C_{ u,max}$                     | Maximum varactor capacitance (F)                             |

| $C_{ u, { m min}}$               | Minimum varactor capacitance (F)                             |

| $D_{in}$                         | Inner diameter of a spiral (µm)                              |

| $D_{out}$                        | Outer diameter of a spiral (µm)                              |

| F                                | Oscillator Noise factor                                      |

| $f_0$ , $\omega_0$               | Frequency of oscillation (Hz, rad/s)                         |

| $f_{1/f}$ , $\omega_{1/f}$       | Flicker noise corner frequency (Hz, rad/s)                   |

| $f_m, \omega_m$                  | Frequency offset from carrier (Hz, rad/s)                    |

| $f_{ m max}$ , $\omega_{ m max}$ | Unit power gain frequency of transistor (Hz, rad/s)          |

| $f_{self}$                       | Self-resonant frequency (Hz)                                 |

| $f_{ m T}$                       | Transition frequency, where current gain falls to unity (Hz) |

| $f_T$ , $\omega_T$               | Unit current gain frequency of transistor (Hz, rad/s)        |

| $G_{ m DS}$                      | Average transistor drain-source conductance (S)              |

| $g_{ m ds}$                      | Transistor drain-source conductance (S)                      |

| $G_{ m ds.eff}$                  | Effective drain-source conductance of cross-coupled pair (S) |

|                                  |                                                              |

Small-signal transistor drain-source conductance at  $V_{DS}$ =0 (S)  $g_{ds0}$ Transistor transconductance (S)  $g_m$ Noise current (A $/\sqrt{Hz}$ )  $i_n$ Reference current for tail bias current (A)  $I_{ref}$ Cross-coupled LC tuned oscillator bias current (A)  $I_{tail}$ VCO constant, or VCO gain (Hz/V)  $K_{V}$ Phase noise (dBc/Hz @  $\omega_m$ ,  $f_m$  offset from carrier)  $\mathcal{L}\{\omega_m\}, \mathcal{L}\{f_m\}$ Cross-coupled pair transistor length (µm)  $L_{CCP}$ N, nNumber of spiral turns Transistor gate oxide trap density (units/m<sup>2</sup>)  $N_{ot}$  $P_{DC}$ DC power Oscillator sideband noise power with respect to carrier  $P_{SBC}$ (W/Hz)Single-ended oscillation power (W)  $P_{sig}$ QQuality factor Capacitor quality factor  $Q_C$ Inductor quality factor  $Q_L$ Loaded Q of LC tuned circuit  $Q_{tank}$ Transistor drain-source resistance  $(\Omega)$  $r_{\rm DS}$ Effective drain-source resistance of cross-coupled pair  $(\Omega)$  $R_{\rm ds.eff}$ Parallel equivalent resistance of lossy LC tuned circuit ( $\Omega$ )  $R_{tank}$ Gap between spiral turns (µm) S Noise current  $(A^2/Hz)$  $S_i$ Transistor flicker noise current density (A<sup>2</sup>/Hz)  $S_{i_{\scriptscriptstyle A}^2.1/f}$ Noise voltage (V<sup>2</sup>/Hz)  $S_{\nu}$ TAbsolute Temperature (K)  $V_{\rm B}$ Transistor bulk potential (V)  $V_{CCP}$ Cross-coupled pair bias potential (V)  $V_{ctl}$ Frequency control voltage (V)

Supply voltage (V)

$V_{DD}$

$v_{\rm DS}$  Transistor drain-source voltage (V)

$V_{\rm G}$  Transistor gate potential (V)

$v_{\rm GS}$  Transistor gate-source voltage (V)

$v_{out+}, v_{out-}$  Differential oscillator output signals (V)

$V_{tail}$  Cross-coupled VCO tail transistor gate bias potential (V)

$V_{TH}$  Transistor threshold voltage (V)

w Spiral inductor conductor width (μm)

$\omega_{1/f^3}$  Corner frequency between -30dB/decade region and

-20dB/decade region in a plot of oscillator phase noise.

W<sub>CCP</sub> Cross-coupled pair transistor width (μm)

$v_n$  Noise voltage ( $V/\sqrt{Hz}$ )

# LIST OF CONSTANTS

$k=1.381\times10^{25} \text{ J/K}$

Boltzmann's constant

$\mu_0$ =1.257×10<sup>-6</sup> H/m

Magnetic permeability of free space

## **Chapter 1**

## **INTRODUCTION**

#### 1.1 WIRELESS COMMUNICATIONS

Beginning in the late 1890s, Italian scientist Guglielmo Marconi successively sent and detected electromagnetic waves across a room. Marconi gradually increased the range, and in 1901, he was able to demonstrate successfully sending the letter 'S' in Morse code over the Atlantic Ocean without wires. Ever since, many other players, namely Lee de Forest, the inventor of the vacuum tube, and Edwin Armstrong, the inventor of superheterodyne system and FM radio competed in the wireless communications race. Like many other industries propelled by wars, the First and the Second World War had accelerated the progress of wireless technology.

The first generation solid-state semiconductor named the transistor, invented by Schockley, Brittain, and Bardeen of the Bell Labs in 1947, opened a new era for the radio industry. Much smaller, efficient, and reliable transistors replaced vacuum tubes. This subsequently reduced the cost and dimensions of the primary power supply, cooling, and equipment accommodation.

Another major step in the semiconductor technology was the development of the technique that came to be known as an Integrated Circuit (IC) by Jack Kilby of Texas Instruments in 1958. IC technology made it possible to integrate transistors and other passive devices like resistors and capacitors all on the same substrate. This did not have immediate impact on the advancement of the wireless technology until Very Large Scale Integration (VLSI) technique gained sufficient momentum starting from the late 1960s. Towards the early 1980s, Monolithic Microwave Integrated Circuits (MMIC) started to appear. MMIC chips integrate much of the radio circuit modules, namely RF amplifier, mixer, and Local Oscillator (LO). Later in the 1990s, monolithic implementation of radio circuit modules was made possible using digital processes, which integrated digital circuit modules for controlling, sampling, and processing of data all in a single chip. This System-On-Chip (SOC) approach allowed for reduction in system form factor and cost.

#### 1.2 MODERN RADIO TRANSCEIVER

Since the birth of superheterodyne system in 1917 by Edwin Armstrong, virtually every wireless communication systems employed the superheterodyne principle to date. A tunable oscillator or a frequency synthesizer is one of the compulsory building blocks in a superheterodyne system along with RF amplifiers and mixers.

The superheterodyne system is able to tune to the frequency under interest, and up or downconvert to frequencies where subsequent filtering or

modulation/demodulation can be performed easily. The frequency translation property of the superheterodyne system is what makes it popular and essential in modern wireless communication systems.

In a superheterodyne receiver shown in Fig. 1.1(a), the received radio frequency (RF) signal through the antenna is often weak, and needs significant boost before it can be processed any further. The low-noise-amplifier (LNA) provides much of the required amplification while minimizing the noise figure.

Fig. 1.1: Superheterodyne (a) receiver and (b) transmitter.

A mixer accepts two separate input signals (RF+LO) and outputs the sum or difference of the two input signals (RF-LO, RF+LO,) in the frequency domain. The mixer can be either active or passive. In either case, a mixer usually has a high noise figure compared to an LNA. Nonetheless, as long as the LNA provides sufficient amplification, use of a mixer with relatively poor noise figure can be tolerated.

The IF filter at the output of the mixer is there to filter out unwanted frequency components of the mixer output.

In the transmit path, as shown in Fig. 1.1(b), the intermediate frequency (IF) signal is given sufficient signal-to-noise ratio (SNR) to prepare for degradation of its SNR after passing through the mixer.

The band-pass (BP) filter selectively passes the desired signal from the mixer output to the power-amplifier (PA) for transmitting via the antenna.

By being able to vary the frequency of the LO, the receiver can selectively downconvert the desired signal received via the antenna, and the transmitter can transmit the signal on the desired frequency channel.

### 1.2.1 Reciprocal Mixing

Noise introduced by an LNA or a mixer is usually amplified thermal noise. Therefore, its noise spectral density characteristic is flat within the pass-band. However, noise introduced by an LO is somewhat different. What contributes to the LO noise are not only the thermal noise, but also the pink noise (1/f noise or flicker noise near DC) of active devices, as well as the spurs from the frequency reference source. The LO

noise near the carrier frequency is considerably larger in magnitude compared to the thermal noise floor of other RF circuit modules.

Ideally, the Fourier representation of a sinusoidal LO signal is represented by a pair of delta functions in the frequency domain. RF/IF signals mixed in the time domain or convoluted in the frequency domain at the mixer with an ideal LO signal is replicated at IF/RF with appropriate amplification. For example, LO signal

$$s(t) = A_0 \cos(\omega_0 t) \tag{1.1}$$

mixed with a pair of RF signals

$$r_1(t) = M_1 \cos(\omega_1 t) \tag{1.2}$$

and

$$r_2(t) = M_2 \cos(\omega_2 t) \tag{1.3}$$

would produces two pairs of IF signals

$$m_{1}(t) + m_{2}(t) = s(t)[r_{1}(t) + r_{2}(t)]$$

$$= A_{0} \cos(\omega_{0}t)[M_{1} \cos(\omega_{1}t) + M_{2} \cos(\omega_{2}t)]$$

$$= \frac{1}{2}A_{0}M_{1}[\cos(\omega_{0} + \omega_{1})t + \cos(\omega_{0} - \omega_{1})t]$$

$$+ \frac{1}{2}A_{0}M_{2}[\cos(\omega_{0} + \omega_{2})t + \cos(\omega_{0} - \omega_{2})t]$$

(1.4)

A low-pass (LP) filter placed at the output of the mixer filters out the frequency components above  $\omega_0$ , and the resulting IF signals become

$$m_1(t) = \frac{1}{2} A_0 M_1 \cos(\omega_1 - \omega_0) t$$

(1.5)

and

$$m_2(t) = \frac{1}{2} A_0 M_2 \cos(\omega_2 - \omega_0) t$$

(1.6)

Fig. 1.2(a) illustrates this ideal downconversion process in the frequency domain.  $r_1(t)$  and  $r_2(t)$  represent received signals adjacent to each other. They can have different levels of power depending on the locations of their transmitters or the modulation scheme used.

When a noisy LO is used, a problem may arise when  $r_1(t)$  and  $r_2(t)$  are closely spaced and one is much stronger than the other. Phase noise of an oscillator has a symmetric skirt shape centered about the carrier frequency. The shape of the noise skirt near the carrier is affected by the frequency locking technique employed. For the time being, a simple noise skirt shape as shown in Fig. 1.2(b) is assumed.

Fig. 1.2: Downconversion with (a) noiseless LO and (b) noisy LO.

During the downconversion process of  $r_1(t)$  and  $r_2(t)$ , the phase noise frequency component  $\phi(t)$  mixes with  $r_1(t)$  and  $r_2(t)$ , just as the carrier s(t) does, and produces IF components  $m_1\phi(t)$  and  $m_2\phi(t)$ .  $m_2\phi(t)$  superimposed on top of  $m_1(t)$  is considered as noise or interference. The consequence is degraded SNR of the received signal  $m_1(t)$ .

This is called reciprocal mixing [1]. It can be a serious problem for both upconverters and downconverters, because it desensitizes the receiver and degrades the transmitted signal integrity. The effect of reciprocal mixing can be reduced either by lowering the oscillator phase noise or increasing the signal spacing in the frequency domain. The latter approach is counterintuitive in the sense that spectral efficiency decreases. Because of the ever-increasing number of wireless devices, efficient use of the RF spectrum is highly desired to accommodate as many wireless devices as possible. Therefore the reduction of the phase noise of the LO should be pursued fervently.

#### 1.2.2 OFDM and Phase Noise

The Orthogonal Frequency Division Multiplexing (OFDM) modulation scheme employed in IEEE 802.11a and HiPERLAN Type 2 standards utilizes 52 sub-carriers per channel. Each channel is 20MHz wide and sub-carrier spacing ( $\Delta f$ ) is 312.5kHz. Both standards support Binary Phase Shift Keying (BPSK), Quadrature Phase Shift Keying (QPSK), 16-bit Quadrature Amplitude Modulation (QAM), and 64-bit QAM [2], [3].

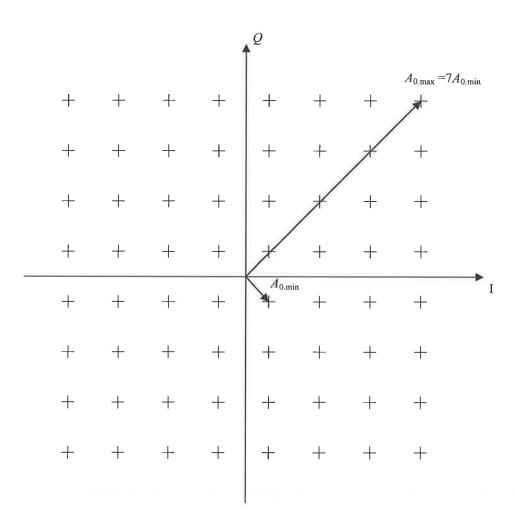

For example, when 64-bit QAM is selected for the maximum bit rate of 54Mbits/s, adjacent sub-carriers can have a maximum of 20log(7/1)≈16.9dB difference in their power levels as the maximum amplitude is 7 times the minimum. This is illustrated in the 64-bit QAM constellation diagram in Fig. 1.3.

Fig. 1.3: Maximum to minimum amplitude ratio in 64-bit QAM constellation.

Due to the relatively close spacing and the large amplitude difference of subcarriers in the 64-bit QAM OFDM signal, the system is highly susceptible to the phase noise of the LO. The LO phase noise components at different frequency offsets mix with all 52 sub-carriers, and through reciprocal mixing, superimpose on top of the up or downconverted sub-carriers as interferences or noise. The interference resulting from the phase noise components less than  $\Delta f$  away from the carrier frequency mostly results in common phase error [4]. Since this is constant for all sub-carriers, and the result is a phase rotation of the constellation, it can be corrected by observing the 4 pilot tones among the 52 sub-carriers [4].

However, phase noise components at around or outside of  $\Delta f$  offset from the carrier result in inter-carrier interference (ICI), which has the appearance of random Gaussian noise [4]. ICI causes loss of orthogonality, resulting in increased symbol error rate (SER). Unfortunately, ICI cannot be corrected due to its random nature, unlike the common phase error [4]. Therefore, in order to minimize the SER and maximize the data throughput, the LO should exhibit low phase noise, especially at frequency offsets around and beyond  $\Delta f$  from the carrier frequency.

#### 1.3 VOLTAGE CONTROLLED OSCILLATORS

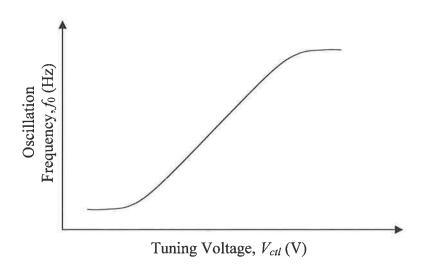

A Voltage Controlled Oscillator (VCO) is a circuit module used in a system whose oscillating output frequency is monotonically determined by its input voltage over a finite range. The frequency control signal is in the form of electric potential, and hence the name VCO. A VCO is a very popular choice for the implementation of the LO in a wireless communication system. A typical frequency tuning curve of a VCO is shown in Fig. 1.4.

A VCO is usually used in a phase-locked loop (PLL) rather than on its own to continually correct for its output phase error accumulated over time, and also to be able to tune the VCO to a desired frequency of oscillation.

High performance wireless communication systems often demand a more stringent set of requirements on the VCOs than digital processors. This is because performance of wireless communication systems depends on the spectral purity of signals transmitted or received, and this purity is directly related to the spectral purity of the VCOs used, which is illustrated in the previous section.

Fig. 1.4: Typical frequency tuning curve of a VCO.

#### 1.3.1 Monolithic CMOS VCOs

Higher levels of integration help to reduce the system production cost, especially when a mass production is needed. This is how VLSI technology overtook discrete component implementations of digital circuits in the past.

As mentioned in the first section, the SOC technology of the modern processes have given designers the ability to integrate a complete or a near complete wireless communication system on a single chip. Monolithic implementation of a VCO along with other RF circuit modules using the SOC technology, without having to compromise the specifications, is highly desirable to lower the production cost of the system.

Complementary-Metal-Oxide-Semiconductor (CMOS) technology is the cheapest brew of VLSI technology available nowadays, and modern CMOS technologies can be used to realize SOC. Therefore, CMOS is the choice of technology for this work despite some difficulties it posses for implementation of high performance analog/RF circuits such as the VCO.

Historically the primary driving forces behind the CMOS industry have been digital VLSI circuits. The majority of CMOS processes have been optimized to implement digital circuits, where all transistors are considered as switches. Speed, size, yield and power dissipation are the prime interests for digital designers. For analog/RF designers however, noise, process variation, gain, linearity, dynamic range, and individual device characteristics are considered equal, if not more important.

Analog/RF circuits make use of on-chip passive devices much more extensively than the digital circuits. Often detailed characterizations of passive elements are not

readily available to designers. Although many modern digital CMOS processes do provide some support for analog/RF circuit designers, the level of support is considered second priority. This makes it even more difficult to design high quality analog/RF circuits in CMOS technology.

Despite the disadvantages of CMOS processes for analog/RF circuits, CMOS is often the choice of technology for many SOC solutions. Their mass productivity at low cost is one of the best selling points. Another attractive aspect of CMOS is their natural ability to integrate high quality digital circuits on the same chip, that work with the analog/RF circuits. This provides the basis for a complete system-on-chip solution, and drastically reduces the cost of the system due to the high level of integration.

Most of analog/RF circuit modules such as amplifiers, mixers, and filters can be integrated relatively easily. Exceptions to this would be circuits that require very large passive components, such as an LP filter with very low cutoff frequency (often used as the loop filter in a PLL), or circuits that require materials that are not available on-chip, such as the surface acoustic wave (SAW) filters that provide excellent frequency selectivity. Some high gain PAs have also proven to be difficult to implement in CMOS due to the insufficient gain of CMOS transistors for the intended application.

A VCO is easy to implement in a CMOS process. There is nothing fundamentally difficult about generating oscillation at the frequency of interest as long as the transistors are sufficiently fast. However, implementing a low-noise, low-power VCO in a CMOS process is a very challenging task. This is because most CMOS processes are optimized with digital circuits in mind and not as much consideration is given for a low-noise operation, critical to the VCO phase noise performance. Therefore, it is left to designers to work around the problems, and the monolithic implementation

of VCOs in CMOS processes has become a very active research area over the past few decades.

Nonetheless, not every VCO known to exist could easily be integrated cost effectively. For example, various cavity, dielectric or SAW resonators require their sizes to be of the order of half-wavelength of the frequency under interest. For 5GHz operation, a half-wavelength is around 30mm in free space. Even with a help of a dielectric to slow down the speed of propagation by the square root of the relative dielectric constant, the required geometry of the resonator would be still too large for a compact integration. Furthermore, use of non-standard materials or processing steps increases the cost of wafer production. For example, cavity resonators would require extra processing steps such as micromachining to create the cavity and metallization of the internal walls. Integration of physical resonator structures would become feasible once the frequency of operation exceeds 100GHz or more [5], unless chip area efficiency or cost is considered unimportant [6].

Monolithic VCOs in CMOS processes that have proven to be area efficient, and cost effective, are digital ring oscillators and inductor-capacitor (*LC*) tuned circuit based oscillators [7]-[12]. Ring oscillators are often used as clock signal generators in digital circuits or in communication systems with relatively relaxed clock jitter or phase noise requirements [8], [11], [12]. Although a typical ring oscillator features relatively large tuning range and smaller chip area compared to tuned circuit based oscillators, in general they cannot be used for high performance communication applications, where system performance depends on the quality of the LO signal. On the other hand, especially for microwave frequencies, the *LC* tuned circuit based oscillators are superior

in terms of phase noise performance, and widely used in high performance wireless communication systems [9], [14], [15].

### 1.3.2 Current Monolithic VCO Performances

As mentioned in the previous section, VCOs used in high performance wireless communication systems are of the *LC* tuned circuit type. Table 1.1 shows a list of high performance multigigahertz monolithic VCOs reported in the literature to date. It should be noted that the list is not limited to CMOS VCOs, but includes VCOs from other competing technologies such as bipolar technology.

While the phase noise values cannot be directly compared, the figure-of-merit (FOM) should give a rough indication as to how they compare one another. It is clear from Table 1.1 that in general, the LC tuned oscillators have better phase noise performance than the ring oscillators listed at the end of the table.

Table 1.1: Comparison of monolithically implemented modern VCOs.

| Reference | Process Technology | f <sub>0</sub> (MHz) | Tuning<br>Range<br>(MHz) | P <sub>DC</sub> (mW) | Phase Noise<br>(dBc/Hz @1MHz) | FOM (dBc/Hz) |

|-----------|--------------------|----------------------|--------------------------|----------------------|-------------------------------|--------------|

| [26]      | 0.25μm CMOS        | 3945                 | 350                      | 4.08                 | -99.2                         | -165.1       |

| [16]      | 0.5μm BiCMOS       | 4900                 | 310                      | 57.2                 | -107.0                        | -163.2       |

| [26]      | 0.35μm CMOS        | 4887                 | 500                      | 9.00                 | -107.3                        | -171.5       |

| [17]      | Si Bipolar         | 5765                 | 350                      | 255                  | -110.0                        | -161.2       |

| [18]      | 0.12μm CMOS        | 3980                 | 1060                     | 1.50                 | -113.0                        | -183.2       |

| [17]      | SiGe HBT           | 4765                 | 330                      | 132                  | -114.0                        | -166.4       |

| [19]      | SiGe HBT           | 3910                 | 350                      | 17.5                 | -114.0                        | -173.4       |

| [20]      | 0.13μm SOI CMOS    | 5612                 | 2600                     | 2.50                 | -114.5                        | -185.5       |

| [21]  | 0.35μm BiCMOS | 4700 | 1000 | 25.0 | -115.5          | -174.9 |

|-------|---------------|------|------|------|-----------------|--------|

| [10]  | 0.25μm CMOS   | 5462 | 285  | 6.90 | -116.0          | -182.4 |

| [22]  | 0.25μm CMOS   | 5230 | 310  | 7.05 | -116.5          | -182.4 |

| [23]  | 0.25μm CMOS   | 4000 | 990  | 18.8 | -117.0          | -176.3 |

| [24]  | 0.25μm CMOS   | 5000 | 1100 | 7.25 | -117.0          | -182.4 |

| [22]  | 0.25μm CMOS   | 5350 | 354  | 7.05 | -117.0          | -183.1 |

| [25]  | 0.25μm CMOS   | 4600 | 230  | 9.40 | -118.1          | -181.6 |

| [15]  | 0.5μm BiCMOS  | 4405 | 620  | 21.6 | -119.0          | -178.5 |

| [17]  | SiGe HBT      | 4765 | 270  | 32.0 | -120.0          | -178.5 |

| [27]  | 0.25μm CMOS   | 4880 | 780  | 21.9 | -124.5          | -184.9 |

| *[28] | 0.6μm BiCMOS  | 2200 | 100  | 1.30 | <del>-7</del> 5 | -141   |

| *[29] | 0.5μm CMOS    | 2200 | N/A  | 11.8 | -94             | -150   |

| *[30] | 0.25μm CMOS   | 4595 | 1470 | 40.0 | -95.3           | -153.3 |

<sup>\*</sup> Ring oscillators

### 1.4 OBJECTIVES

The ultimate goal of this thesis is to develop a systematic way to design and produce high performance monolithic CMOS VCOs to use in modern wireless front-end chipsets. High performance in the context of this thesis is defined as reliable, high frequency, low cost, low power, low noise, and temperature/process variation tolerant.

In general, there are four topics presented in this research work. First, existing VCO phase noise theories are to be reviewed. Their properties and usefulness in predicting the phase noise of a VCO are to be discussed. In addition, the limitations of some of the modern computer aided design (CAD) tools in predicting the VCO phase noise will be discussed.

Second, the workings of various differential LC tuned VCO topologies are to be thoroughly investigated. Some of the common misunderstandings of cross-coupled LC tuned oscillators found in the literature are addressed. This includes the commonly accepted oscillation amplitude expressions, the so-called 'voltage-limited region' of a VCO bias region, and the topological superiority of the complementary topology over other topologies often claimed in the literature.

Third, a set of optimization techniques is to be developed to design the best performing VCO realizable for a given process technology, die area, and power budget. A monolithic planar spiral inductor optimization technique, efficient tradeoff between power and noise via L/C ratio scaling, appropriate sizing of the cross-coupled transistors, and a low-power, low-noise current biasing technique are among the VCO optimization techniques to be developed.

Lastly, the VCO optimization techniques developed are to be tested and validated by fabricating a number of VCOs and analyzing their measurement results. Also, the performances of these VCOs are to be compared against the leading monolithic VCO designs reported in the literature. That is deemed to be the only reliable and accurate way to prove the effectiveness of the optimization techniques developed in this research work.

### 1.5 SCOPES

The type of oscillators studied in this thesis is cross-coupled LC tuned negative conductance oscillator with differential outputs.

Fabrication technologies used are a Silicon-On-Insulator (SOI) CMOS process and a bulk silicon substrate CMOS process.

VCO topologies covered include, N-type Metal Oxide Semiconductor (NMOS) only topology, complementary topology, where both cross-coupled NMOS and P-type Metal Oxide Semiconductor (PMOS) devices are used in complementary fashion, and other variants of the two aforementioned topologies.

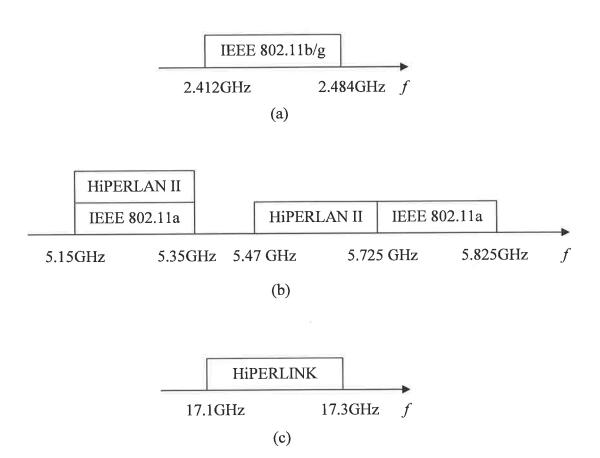

Fig. 1.5: Frequency bands allocations for (a) IEEE 802.11b/g, (b) IEEE 802.11a and HiPERLAN II, and (c) HiPERLINK wireless communication standards.

Target applications for VCOs studied in this thesis include wireless communication systems operating with the IEEE 802.11b/g or IEEE 802.11a or High Performance Radio Local Area Network Type 2 (HiPERLAN II) or High Performance

Radio Link (HiPERLINK) standards. Their operating frequency ranges from 2.412GHz to 2.484GHz for IEEE 802.11b/g standards, 5.15GHz to 5.825GHz for IEEE 802.11a and HiPERLAN II standards, and 17.1GHz to 17.3GHz for HiPERLINK standard [2], [3], [13], [32]. Fig. 1.5 shows spectrum allocations for the three standards.

### 1.6 MAJOR CONTRIBUTIONS

The VCO optimization techniques newly developed in this research work allow for the design of the best performing monolithic VCO for a given CMOS process technology, power consumption, and chip area. Thorough understanding of the cross-coupled *LC* tuned VCOs acquired in Chapter 2 and 3 lead to the development of a number of new optimization techniques for monolithic CMOS VCOs in Chapter 4. The techniques are applied to nine experimental VCOs presented in Chapter 5 and 6 to verify the effectiveness of the techniques. The tenth VCO presented in Chapter 6 is an industrial quality, high performance, CMOS VCO designed with the new optimization techniques. This VCO outperforms all VCOs listed in Table 1.1, and it is a tangible proof that the newly developed VCO optimization techniques have advanced the performance barrier of modern monolithic CMOS VCOs.

The following list summarizes the major contributions made by this thesis.

1) Commonly used linear oscillation amplitude estimation equations for cross-coupled LC tuned oscillators are proven to be largely in error (section 3.2.1).

- 2) The voltage-limited region frequently and unsuspectingly mentioned in the literature is proven to be nonexistent for cross-coupled *LC* tuned oscillators (section 3.2.1).

- 3) Topological superiority of the complementary topology over NMOS-only topology claimed in the literature is proven to be misleading (section 3.2.2).

- 4) A new geometric optimization technique for monolithic planar spiral inductors is developed (section 4.3).

- 5) A new and efficient tradeoff technique that involves a tradeoff between power consumption and phase noise performance through L/C ratio scaling is developed (section 4.4).

- 6) A new cross-coupled transistor size optimization technique is developed (section 4.5).

- 7) A new low-power, low-noise VCO current biasing technique is implemented and tested (section 4.6.2).

- A new accurate RF oscillation amplitude detector is devised and tested (section 6.4).

### 1.7 THESIS ORGANIZATION

The thesis consists of six chapters. Chapter 1 has described the motive and the objectives of this research work, followed by the scope of the work, list of major contributions and the organization of the thesis.

Chapter 2 reviews two different VCO phase noise theories from the literature, and discusses their validity, accuracy, and limitations. Also, the limitations of modern CAD tools in estimating phase noise performance are discussed.

Chapter 3 studies various differential *LC* tuned oscillator topologies. The workings of cross-coupled oscillators are thoroughly investigated and, through this process, a better understanding on how the oscillation amplitude can be determined is acquired. Also, some common misunderstandings associated with cross-coupled oscillators frequently described in the literature are addressed.

Then various frequency-tuning methods available in modern CMOS processes are investigated.

After that, noise sources that contribute to the VCO phase noise are identified. Also, the important flicker noise upconversion processes are investigated. Understandings acquired from these investigations provide solid grounds for the development of the VCO optimization techniques described in Chapter 4.

Chapter 4 develops various VCO optimization techniques to assist design of high performance VCOs. A monolithic planar spiral inductor is identified as the most cost effective way to implement the inductance required by a tuned circuit. Also, a new geometric optimization technique has been developed for the implementation of the highest quality inductors realizable for a given area budget and process technology.

After that, a technique that efficiently trades increased power consumption for improved phase noise performance through L/C ratio scaling is developed. Also, an optimal cross-coupled transistor sizing technique is developed.

A new low-power, low-noise VCO current biasing technique has been developed to reduce the power consumption in the bias circuit while not compromising the phase noise performance.

Chapter 5 presents eight experimental VCOs, designed and fabricated using a Silicon-On-Insulator (SOI) CMOS process technology. Of these, two are designed to operate at 17GHz and the rest at 5GHz.

The various ideas developed in Chapter 3 and Chapter 4, namely the multi layer inductor effects, L/C ratio scaling, switched capacitor bank feasibility, topological advantages and the adequacy of the process technology used are tested and validated.

Chapter 6 presents one experimental and one industrial quality 5GHz VCOs. The experimental VCO is aimed to push the boundary of the phase noise performance of monolithic 5GHz VCOs and demonstrates the feasibility of integrating 2a VCO into a high performance Access Point (AP) quality radio front-end chip.

The industrial quality VCO is designed with a stringent set of specifications to meet the requirements of a monolithic high performance CMOS VCO needed for the high performance dual-band wireless AP equipped product lines of Cisco Systems.

The performances of some of the VCOs developed in this research work are compared against other state-of-the-art monolithic VCOs reported in the literature to date.

Lastly, Chapter 7 concludes the thesis and presents few recommendations for the future work.

# **Chapter 2**

# VCO PHASE NOISE

### 2.1 INTRODUCTION

Since the invention of the triode vacuum tube by Lee de Forest in 1907 [33], studies on electronic oscillators were commenced. Development of electronic oscillators was led by the wireless communications industry. The quality of oscillator was under constant demand for improvement. However, it was only over the past few decades or so, integrated oscillators have seen significant advance in phase noise theory and performance. This was to meet the often-stringent specifications of modulation techniques used in the explosively growing digital wireless communication industry of today.

As pointed out in the previous chapter, the data throughput of a wireless communication system depends on the spectral purity of the LO. Ability to estimate the phase noise of an oscillator allows designers to predict achievable SER or data throughput of the system and estimate its overall performance.

An accurate and reliable way of estimating the phase noise of a VCO to be integrated in the system is to actually fabricate a prototype VCO and measure its

performance with a spectrum analyzer or phase noise measurement instrument set such as the EUROPTEST PN9000. The downsides of this approach are lengthy turn-around period of fabrication processes and high cost involved in producing the prototype.

Usually there are a number of circuit parameters affecting VCO noise performance. Circuit designers are able to optimize the circuit for optimal performance by experimenting with these parameters liberally. However, fabricating and measuring phase noise for every parameter change would be simply not be viable.

Fabrication of prototypes is a sensible design practice in many cases. However, the number of prototype fabrication runs should be minimized in order to lower development time and cost. Instead, maximum utilization of simulations and performance estimates based on theory should be practiced.

Over the years, researchers have derived different phase noise estimation theories and equations. Earlier phase noise analysis often over simplified practical oscillators to a simple linear time-invariant (LTI) system [34]-[36]. Limitations with this model were soon realized by many and replaced with a more sophisticated linear time-varying (LTV) model [9], [37], [38]. Investigation of nonlinear properties of practical oscillators have led to identification of upconversion or downconversion processes of noise in oscillators [9], [29], [37]-[44].

To help designers to estimate VCO performance from as early as the design stage, modern CAD tools such as SpectreRF from Cadence Design Systems are equipped with a sophisticated nonlinear phase noise simulator [45].

In this chapter, a brief description of oscillator phase noise is presented first.

After that, the pros and cons of LTI and LTV models, and the limitations of modern SPICE circuit simulators are discussed.

### 2.2 PHASE NOISE

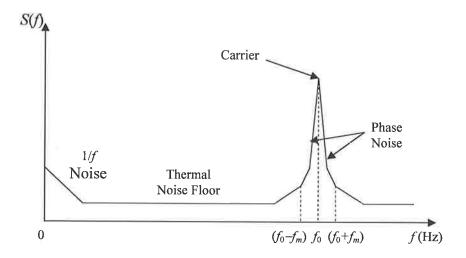

Due to the unavoidable noise present in every electronic circuit building blocks, output signal of a VCO is noisy like any real electrical signal. The spectral power density of an oscillator output consists of the carrier power mostly concentrated at the frequency of oscillation, and noise components spread out symmetrically about the carrier frequency as side skirts for small frequency offsets ( $f_m \ll f_0$ ) as shown in Fig. 2.1.

Fig. 2.1: Power spectral density of a VCO output.

An oscillator tuned at frequency  $f_0$  can be represented by

$$s(t) = [A_0 + \alpha(t)] \cos[\omega_o t + \theta(t)]$$

(2.1)

where  $A_0$  is the oscillation amplitude, and  $\alpha(t)$  and  $\theta(t)$  represent amplitude noise and phase noise respectively.

The equipartition theorem of thermodynamics states that each independent degree of freedom of a system in equilibrium at temperature T has a mean energy of 0.5kT, where k is the Boltzmann constant [46]. Assuming oscillator amplitude and phase noise have the same thermal origin, the oscillator noise energy is equally divided between the two. However, because any practical oscillator has some sort of amplitude limiting mechanism built in to limit the amplitude from growing without a bound, the amplitude noise component at the output is suppressed ( $\alpha(t) \rightarrow 0$ ).

On the other hand, there is no equivalent self-limiting mechanism that exists for the phase noise. Therefore, most practical VCOs exhibit only the phase noise component on their output [33].

Suppose a amplitude limited carrier is frequency modulated by a sine wave with frequency  $f_m$ . Then (2.1) is then written as

$$s(t) = A_0 \cos(\omega_0 t + \theta_p \sin \omega_m t)$$

(2.2)

where  $\theta_p = \Delta f / f_m$  is the peak phase deviation. (2.2) expands to

$$s(t) = A_0 \left[ \cos(\omega_0 t) \cos(\theta_p \sin \omega_m t) - \sin(\omega_0 t) \sin(\theta_p \sin \omega_m t) \right]$$

(2.3)

For the peak phase deviation or  $\theta_p$  much less than 1 ( $\theta_p \le 1$ ),

$$\cos(\theta_n \sin \omega_m t) \approx 1 \tag{2.4}$$

and

$$\sin(\theta_p \sin \omega_m t) \approx \theta_p \sin \omega_m t \tag{2.5}$$

Therefore, s(t) can be written as

$$s(t) = A \left[ \cos(\omega_o t) - \sin(\omega_o t) \theta_p \sin \omega_m t \right]$$

$$= A \left\{ \cos(\omega_o t) - \frac{\theta_p}{2} \left[ \cos(\omega_o + \omega_m) t - \cos(\omega_o - \omega_m) t \right] \right\}$$

(2.6)

This means, any small phase variation with frequency  $f_m$  and peak amplitude  $\theta_p$  results in two frequency components on both sides of the carrier with an equal magnitude of  $\theta_p/2$  and frequency offset of  $f_m$  from the carrier. This is why the phase noise appears symmetrically about the frequency of oscillation for small frequency offsets [47].

Phase noise of an oscillator ( $\mathcal{L}\{f_m\}$ ) is most commonly represented as a ratio of single sideband (SSB) oscillator noise power at  $f_m$  offset from the carrier in 1Hz bandwidth to the total oscillator carrier power [48]. The unit is given in dBc/Hz, meaning the noise is in dB below the carrier per Hz of bandwidth. Also, because phase noise is a measure of noise power at a given frequency offset from the carrier, stating a phase noise of an oscillator must accompany the offset frequency where the measurement is made.

### 2.3 LINEAR OSCILLATORS

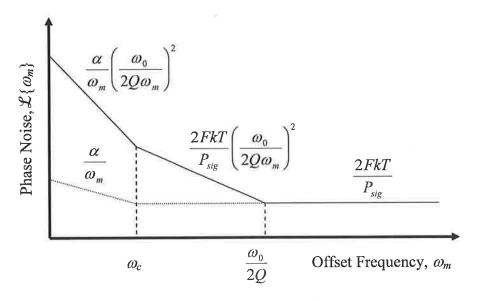

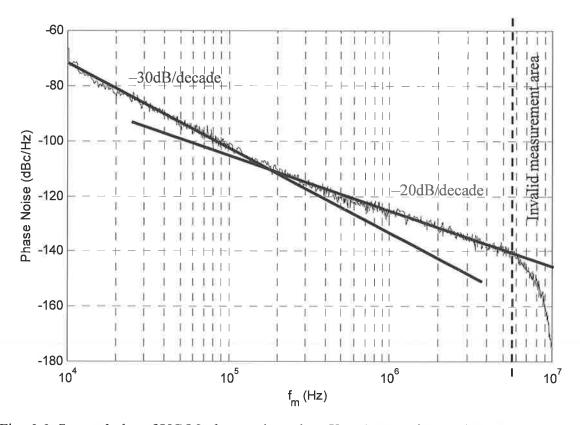

In 1966, D. B. Leeson published the first generation phase noise model of *LC* tuned feedback oscillators. This was a heuristic derivation of short-term stability or phase noise behavior of oscillators without formal proof [34]. Leeson's phase noise equation acknowledged the –30dB/decade and –20dB/decade slopes and flat regions in

single-sided (SS) oscillator output power spectral density (PSD) when plotted against the offset frequency,  $\omega_m$  from the carrier frequency,  $\omega_0$  as illustrated in Fig. 2.2.

Fig. 2.2: Phase noise plot of a typical electronic oscillator.

$$\mathcal{L}\{\omega_{m}\} = \left(\frac{\alpha}{\omega_{m}} + \frac{2FkT}{P_{sig}}\right) \left[\left(\frac{\omega_{0}}{2Q\omega_{m}}\right)^{2} + 1\right]$$

$$= \frac{\alpha}{\omega_{m}} \left(\frac{\omega_{0}}{2Q\omega_{m}}\right)^{2} + \frac{2FkT}{P_{sig}} \left(\frac{\omega_{0}}{2Q\omega_{m}}\right)^{2} + \frac{\alpha}{\omega_{m}} + \frac{2FkT}{P_{sig}}$$

(2.7)

In Leeson's equation (2.7), k is the Boltzmann's constant, T is absolute temperature, Q is the loaded quality factor of the resonator, F is an empirical noise factor of the oscillator,  $\alpha$  is another empirical parameter 1that joins the  $\omega^{-3}$  region to the  $\omega^{-2}$  region of the phase noise plot at  $\omega_c$ , which is the flicker noise corner frequency of the amplifier,  $P_{sig}$  is the average power of oscillation, and  $\omega_0/(2Q)$  is the half-bandwidth or the 3dB attenuation frequency offset of the resonator.

Leeson's model qualitatively describes the shape of phase noise close to the carrier. It looks as if the flicker noise component,  $\left(\frac{\alpha}{\omega_m}\right)$  and the white noise component,  $\left(\frac{2FkT}{P_{sig}}\right)$  of oscillator noise sources are given additional -20dB/decade slope,

$$\left(\frac{\omega_0}{2Q\omega_m}\right)^2$$

within the pass-band,  $\left(\frac{\omega_0}{2Q}\right)$  of the resonator. The empirical fitting

parameter F determines the vertical displacement of the phase noise curves based on actual measurement of the phase noise in the  $-20 \, \mathrm{dB/decade}$  slope region.

Although Leeson's equation acknowledges the appearance of flicker noise near the carrier, no explanation was provided as to how this low frequency noise was upconverted to the high frequencies of oscillation.

### 2.3.1 Linear LC Tuned Oscillator Analysis

Others [35], [49], [50] have reproduced Leeson's equation in an attempt to mathematically estimate the noise factor, F. In their analyses, the phase noise component resulting from upconversion of flicker noise was considered not as important since it often appeared with very small offset frequency. Instead, emphases were given on the prediction of F that determined the vertical displacement of the – 20dB/decade slope, which was often the dominant phase noise component in the output phase noise PSD plot.